इंटरनेट पर, आप वेरिलॉग एचडीएल के परिचय के साथ बहुत सारे लेख पा सकते हैं। वे सभी भाषा के वाक्यविन्यास और शब्दार्थ का वर्णन करते हैं, लेकिन, दुर्भाग्य से, डिजिटल सर्किट के डिजाइन में उपयोग किए जाने वाले मूल प्रतिमानों का खुलासा नहीं करते हैं। जावा भाषा के सिंटैक्स को आपको समझाने की कल्पना करें, लेकिन ऑब्जेक्ट-ओरिएंटेड डिज़ाइन के बारे में आपको कुछ भी नहीं बता रहा है। यदि आप ओओपी से परिचित हैं, तो ऐसा परिचय पर्याप्त होगा, लेकिन यदि आप केवल सी जानते हैं, तो आप "पुराने तरीके से" लिखेंगे, जटिल तरीकों से विशाल कक्षाएं बना सकते हैं।

डिजिटल सर्किटरी और हार्डवेयर विवरण भाषाओं का अध्ययन करने वाले प्रोग्रामर के साथ कुछ ऐसा होता है। भाषा के सरल वाक्यविन्यास को जल्दी से समझने के लिए, वे निर्माण का वर्णन करना शुरू करते हैं जो हार्डवेयर इंजीनियर के दृष्टिकोण से पागल हैं। मेरे छात्रों में ऐसे लोग थे जिन्होंने प्रति घड़ी चक्र में "बबल सॉर्टिंग" लिखा था, पागल अतुल्यकालिक सर्किट जो प्रत्येक शुरुआत में अलग-अलग काम करते थे और खिड़की के बाहर अलग-अलग मौसम में, विशाल संयोजन डिवाइडर जो कई घंटों तक गहन विचारशीलता में जगह और मार्ग लेते थे।

उन लोगों के लिए जिनके पास प्राइमर पढ़ने का समय नहीं है, लेकिन उनकी इच्छा है या

कुछ सरल सर्किट को डिजाइन करने की आवश्यकता है, मैंने डिजिटल सर्किट डिजाइन करने के लिए मुख्य आधुनिक प्रतिमान के बारे में यह संक्षिप्त परिचय लिखने का फैसला किया - सिंक्रोनस सर्किट। और उनमें से एक भाषा के बारे में उनका वर्णन करते थे।

लेख शुरुआती के लिए करना है। पाठ को समझने के लिए, ज्ञान के एक न्यूनतम सेट की आवश्यकता होती है - समकालिक डी-ट्रिगर और गेट्स की समझ।

सिंक्रोनस सर्किट

सिंक्रोनस डिजिटल सर्किट में गेट, सर्किट (नेट) और फ्लिप-फ्लॉप शामिल हैं। सिंक्रोनस सर्किट में, एक एकल सिंक्रनाइज़ेशन सिग्नल होता है जो सभी मेमोरी एलिमेंट्स (ट्रिगर्स) को नियंत्रित करता है।

औपचारिक रूप से, एक तुल्यकालिक सर्किट को निम्नानुसार परिभाषित किया जा सकता है:

एक तुल्यकालिक सर्किट एक डिजिटल सर्किट

सी है जिसमें गेट्स, ट्रिगर्स और सिग्नल प्रसार सर्किट शामिल हैं जो निम्न स्थितियों को संतुष्ट करता है:

- सर्किट में एक एकल क्लक सर्किट होता है जिसके साथ सिंक्रोनाइज़ेशन सिग्नल फैलता है (क्लॉक सिग्नल, क्लॉक सिग्नल)

- क्लॉक सिग्नल को सर्किट के इनपुट पोर्ट द्वारा नियंत्रित किया जाता है।

- Clk सिग्नल द्वारा नियंत्रित कई पोर्ट्स कई ट्रिगर सिंक्रोनाइज़ेशन इनपुट के बराबर हैं

- हम सर्किट सी को निम्नानुसार परिभाषित करते हैं: स्कीम सी ' सर्किट सी से प्राप्त होता है: (1) क्लॉक सर्किट को हटाने से, (2) इनपुट पोर्ट को हटाने वाले क्लर्क सिग्नल को नियंत्रित करता है, (3) सभी ट्रिगर्स को आउटपुट पोर्ट (इनपुट डी के बजाय) और इनपुट से बदल देता है पोर्ट (क्यू आउटपुट के बजाय)। परिणामी सर्किट सी ' कॉम्बिनेशन होना चाहिए

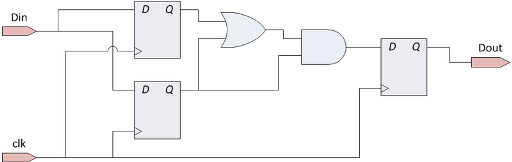

एक तुल्यकालिक सर्किट का एक उदाहरण चित्र में दिखाया गया है:

यहां गैर-समकालिक सर्किट के कुछ उदाहरण दिए गए हैं:

लगभग सभी मौजूदा डिजिटल सर्किट सिंक्रोनस हैं, या एसिंक्रोनस चैनलों के माध्यम से बातचीत करने वाले कई सिंक्रोनस सर्किट शामिल हैं। सिंक्रोनस सर्किट की लोकप्रियता का कारण संकेतों के प्रसार समय के विश्लेषण की सादगी है। समय विश्लेषण एक अलग लेख के लिए एक विषय है, लेकिन हमें अभी भी इस मुद्दे पर संक्षेप में छूने की आवश्यकता है।

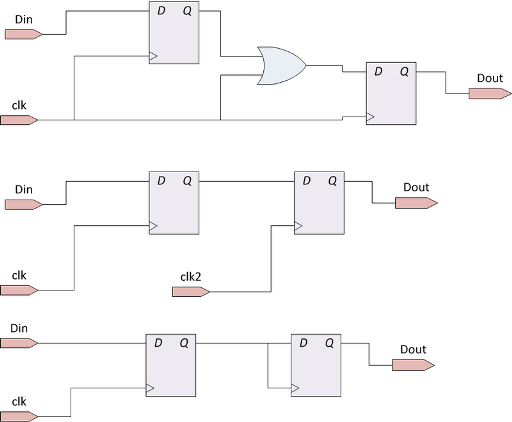

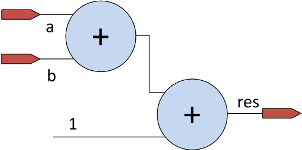

फ़ंक्शन R = A + B + 1 को लागू करने वाली निम्न योजना पर विचार करें:

रजिस्टरों ए, बी और आर तुल्यकालन सिग्नल के प्रमुख किनारे (डीएल) के साथ इनपुट डी पर मूल्यों को संग्रहीत करते हैं, अर्थात। उस समय में जब clk मान 0 से 1 तक बदलता है।

संकेत योजक (और अन्य दहनशील तत्वों) के माध्यम से तुरंत नहीं, बल्कि फाटकों (सबसे महत्वपूर्ण पथ) से सबसे बड़े पथ की लंबाई के आधार पर देरी से फैलते हैं, अर्थात्। तत्व की जटिलता से। उदाहरण के लिए, योजक में महत्वपूर्ण पथ स्थानांतरण संकेतों के माध्यम से उच्च क्रम तक जाएगा ("कॉलम" में योग की गणना करने की कल्पना करें)।

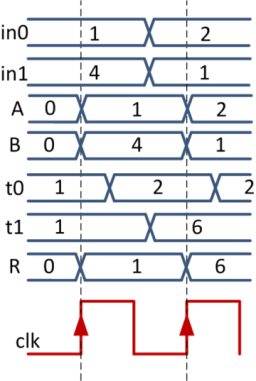

मान लीजिए कि पहले 0. सभी रजिस्टरों में लिखा गया था। और 1 और 4 इनपुट पहले 1 और 4 के मान के साथ दिए गए हैं, और फिर 2 और 1. तब हमारे सर्किट के लिए समय आरेख इस तरह दिख सकता है:

क्लक के पहले किनारे पर, मूल्य 1 और 4 को रजिस्टरों ए और बी में लिखा जाएगा। सिग्नल को जोड़ने के माध्यम से प्रसारित होने के बाद, परिणाम मान 1 + 4 + 1 = 6 तार टी 1 पर दिखाई देगा। फिर, clk के दूसरे किनारे पर, परिणाम को R रजिस्टर करने के लिए लिखा जाएगा, और A और B को रजिस्टर करने के लिए नए इनपुट मान।

अब मान लीजिए कि clk सिग्नल की अवधि आधी है। तब सिग्नल आरके का दूसरा किनारा रजिस्टर आर पर दिखाई देता है इससे पहले कि सही डेटा टी 1 पर दिखाई दे। यानी सर्किट सही ढंग से काम नहीं करेगा!

यहाँ से सिंक्रोनस सर्किट के सही संचालन के मूल नियम का पालन किया जाता है:

सर्किट में महत्वपूर्ण पथ के माध्यम से देरी सिंक्रनाइज़ेशन सिग्नल की अवधि से कम होनी चाहिए।महत्वपूर्ण पथ सर्किट में सबसे लंबा पथ है, आउटपुट से रजिस्टर के इनपुट तक। एक नियम इस नियम से लिया गया है जो तुल्यकालिक सर्किट की सबसे बड़ी कमियों में से एक है।

सिंक्रोनस सर्किट सर्किट में गंभीर रूप से निर्धारित आवृत्ति पर संचालित होता है।कल्पना कीजिए कि 1 नैनोसेकंड की देरी के साथ सर्किट में हजारों संयोजन मार्ग हैं। और 2 नैनोसेकेंड की देरी से एक रास्ता। इस एकमात्र तरीके के कारण, सर्किट को 500 मेगाहर्ट्ज की आवृत्ति पर देखना चाहिए, हालांकि यह गीगाहर्ट्ज़ पर काम कर सकता है। इसलिए, जब सिंक्रोनस सर्किट डिजाइन करते हैं, तो लंबे कॉम्बिनेशन चेन को रजिस्टरों द्वारा कन्वेयर स्टेज में तोड़ दिया जाता है। उदाहरण के लिए, एएमडी बुलडोजर प्रोसेसर में, कॉम्बिनेशन पथ की औसत लंबाई 12-14 एफओ 4 समतुल्य गेट्स (4 इनवर्टर के साथ लोड एक यूनिट आकार इन्वर्टर के बराबर देरी) है।

इस दोष के बावजूद, सिंक्रोनस सर्किट बहुत लोकप्रिय हो गए हैं। समकालिक सर्किट को आसानी से समय विश्लेषण द्वारा स्वचालित किया जा सकता है, अर्थात। आवृत्ति जिस पर सर्किट सही ढंग से काम कर सकता है वह स्वचालित रूप से कार्यक्रम (अस्थायी विश्लेषक) द्वारा निर्धारित किया जाता है। जब कोई डेवलपर इन विवरणों से दूर जा सकता है, तो सिंक्रोनस सर्किट को रजिस्टरों के बीच स्थानान्तरण के एक सेट द्वारा निर्दिष्ट किया जा सकता है। सर्किट के विवरण के लिए यह दृष्टिकोण - डिजिटल सर्किट के तर्क के विवरण में रजिस्टर ट्रांसफर लॉजिक (आरटीएल) मुख्यधारा बन गया है। उदाहरण के लिए, हमारे उदाहरण से सर्किट निम्नलिखित तबादलों द्वारा वर्णित किया जा सकता है:

A = in0

B = in1

R = A+B+1

प्रत्येक घड़ी पर, in0 को A रजिस्टर करने के लिए लिखा जाता है, B को रजिस्टर करने के लिए in1 लिखा जाता है, और A + B + 1 को R रजिस्टर करने के लिए लिखा जाता है। RTL सर्किट का वर्णन करने का विचार पाठ को हार्डवेयर विवरण भाषाओं को रेखांकित करता है: वेरिलॉग HLD और VHDL। यह उनमें से एक को बेहतर तरीके से जानने का समय है।

वेरिलॉग एचडीएल पर सिंक्रोनस सर्किट का विवरण

मॉड्यूल

वेरिलोग पर कार्यक्रम, यह सर्किट का विवरण भी है, जिसमें मॉड्यूल (मॉड्यूल), अधिक सटीक रूप से, मॉड्यूल के उदाहरण (मॉड्यूल उदाहरण) शामिल हैं। मॉड्यूल को "ब्लैक बॉक्स" के रूप में सोचा जा सकता है, जिसमें से तारों को चिपकाया जाता है - पोर्ट। पोर्ट तीन प्रकार के होते हैं: इनपुट (इनपुट), आउटपुट (आउटपुट) और द्विदिश (इनऑउट)। ज्यादातर मामलों में, पहले दो प्रकार के बंदरगाहों का उपयोग किया जाता है। तीन राज्यों और खुली नाली के साथ आउटपुट के आधार पर द्विदिश बसों को मॉडल करने के लिए द्विदिशीय बंदरगाहों की आवश्यकता होती है। हम उन पर विचार नहीं करेंगे।

बंदरगाहों की सूची मॉड्यूल हेडर में वर्णित है। उदाहरण के लिए, इस खाली मॉड्यूल पर विचार करें:

module blackbox // module - , blackbox -

(

input a, b, c // a,b,c

input [7:0] bus, // bus - 8-

output [7:0] bus_out // bus_out, 8-

);

//

endmodule // endmodule - ,

मॉड्यूल का शरीर इसकी कार्यक्षमता का वर्णन करता है। यह मॉड्यूल खाली है, इसके पोर्ट कहीं भी कनेक्ट नहीं हैं। मॉड्यूल की कार्यक्षमता का वर्णन करने के लिए आगे बढ़ने से पहले, हम आपको वेरिलोग में बुनियादी डेटा प्रकारों से परिचित कराएंगे।

डेटा प्रकार

वेरिलॉग में दो प्रकार के प्रकार होते हैं: सी से नकल किए गए हार्डवेयर और मानक अंकगणितीय डेटा प्रकार के प्रकार। हम केवल कक्षाओं में से पहले पर विचार करेंगे, क्योंकि यह वह है जो सर्किट में संकेतों को मॉडल करने के लिए उपयोग किया जाता है।

वेरिलोग में, एक संकेत 4 मान ले सकता है:

- ० - तार्किक शून्य या असत्य

- 1 - तार्किक इकाई, या सत्य

- x एक अपरिभाषित मान है। उदाहरण के लिए, सिमुलेशन के प्रारंभिक क्षण में रजिस्टर का मूल्य (रीसेट से पहले या रजिस्टर में पहला रिकॉर्ड)

- z एक उच्च प्रतिबाधा अवस्था है। सबसे अधिक, एक सिग्नल इस मूल्य को लेता है अगर यह कहीं भी जुड़ा नहीं है - "वायर ब्रेक"

अधिकांश वेरिलोग मॉड्यूल 2 मुख्य डेटा प्रकारों का उपयोग करते हैं -

तार और

reg । नाम से ऐसा लग सकता है कि

वायर मॉडल एक तार है, और

रेग एक रजिस्टर है, लेकिन, जैसा कि बाद में दिखाया जाएगा, यह पूरी तरह सच नहीं है। दो प्रकार की उपस्थिति भाषा के डिजाइन में एक बग है, सिस्टमविरलॉग में, वेरिलोग का आधुनिक संस्करण, एक सार्वभौमिक प्रकार का

तर्क है जो सभी मामलों में उपयोग किया जा सकता है।

प्रत्येक प्रकार पर अलग से विचार करें।

तारोंतार प्रकार का उपयोग संकेतों को अनुकरण करने के लिए किया जाता है जो "स्टोर" नहीं कर सकते हैं। उदाहरण के लिए, कॉम्बिनेशन सर्किट के आउटपुट में मूल्य पूरी तरह से इनपुट पर मूल्यों द्वारा निर्धारित किया जाता है। यदि इनपुट में मान बदलते हैं, तो आउटपुट में मूल्य बदल जाता है, अर्थात्। राज्य संग्रहीत नहीं है।

तार प्रकार का उपयोग निरंतर असाइनमेंट ऑपरेशन के साथ संयोजन में किया जाता है -

असाइन करें । निरंतर असाइनमेंट के साथ, जब भी असाइनमेंट के दाईं ओर चर का मान बदलता है, तो बाईं ओर चर का मान अपडेट किया जाता है। उदाहरण के लिए, एक सरल संयोजन सर्किट को निम्नानुसार वर्णित किया जा सकता है:

module comb

(

input wire [7:0] a,b,

output [7:0] res // wire -, output wire [7:0] res

);

assign res = a+b+1;

endmodule

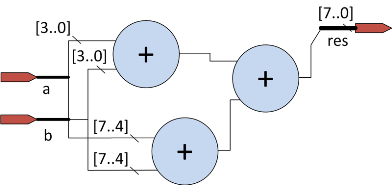

मॉड्यूल बॉडी के अंदर सिग्नल भी घोषित किए जा सकते हैं:

module comb

(

input wire [7:0] a,b,

output [7:0] res

);

wire [3:0] x,y;

assign x = a[3:0] + b[3:0]; // 4 b

assign y = a[7:4] + b[7:4]; // 4 b

assign res = x+y;

endmodule regs

regsप्रकार

reg एक मान को संग्रहीत कर सकता है और प्रक्रियात्मक ब्लॉकों में उपयोग किया जाता है। वेरिलोग की प्रक्रिया ब्लॉक एक ऐसी प्रक्रिया है जो एक विशिष्ट घटना पर आग लगाती है। उदाहरण के लिए, यह घटना घड़ी संकेत के सामने या सिमुलेशन की शुरुआत हो सकती है। प्रक्रियात्मक ब्लॉकों में, सी-जैसे नियंत्रण संरचनाओं का उपयोग किया जा सकता है:

- अगर ... और ..

- के लिए

- करो ... जबकि ..

- मामला (एनालॉग स्विच)

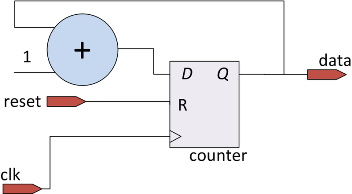

प्रक्रियात्मक ब्लॉक दोनों तुल्यकालिक सर्किट (मेमोरी वाले सर्किट) और संयोजन सर्किट का अनुकरण कर सकते हैं। उदाहरण के लिए, एक बाइनरी काउंटर सर्किट के विवरण पर विचार करें:

module counter

(

input clk, reset,

output [7:0] data

);

reg [7:0] counter;

assign data = counter;

always @( posedge clk) // clk

begin

if (reset)

counter = 0;

else

counter = counter + 1;

end

endmodule हमेशा

हमेशा @ (

posedge clk) लाइन को संवेदनशीलता सूची कहा जाता है। यह उन घटनाओं को परिभाषित करता है जिनके द्वारा प्रक्रियात्मक ब्लॉक निष्पादित किया जाता है। इस ब्लॉक को सिंक्रनाइज़ेशन सिग्नल के प्रत्येक सकारात्मक किनारे पर निष्पादित किया जाता है। इस प्रकार, ब्लॉक काउंटर के तर्क का अनुकरण करता है, काउंटर सिग्नल को एक रजिस्टर के रूप में संश्लेषित किया जाएगा।

प्रक्रियात्मक ब्लॉक भी कॉम्बिनेशन सर्किट को मॉडल कर सकते हैं। उदाहरण के लिए, निम्न कोड को एक कंबाइन में संश्लेषित किया जाता है:

wire [7:0] a,b;

reg [7:0] res;

always @*

begin

res = a+b;

end

यहां, संवेदनशीलता सूची

हमेशा @ * का अर्थ है कि हर बार असाइनमेंट ऑपरेशन के दाईं ओर सिग्नल मूल्यों को बदलने के लिए प्रक्रियात्मक ब्लॉक को निष्पादित किया जाता है। इस मामले में, प्रक्रियात्मक ब्लॉक हर बार ट्रिगर होता है a और b परिवर्तन का संकेत देता है। इस पंक्ति के समतुल्य, संवेदनशीलता की निम्न सूची होगी:

always @(a or b) // , a b

हमेशा प्रक्रिया ब्लॉक का उपयोग करके एक कॉम्बिनेशन सर्किट का वर्णन करते

समय, यह याद रखना चाहिए कि संवेदनशीलता सूची में संकेतों द्वारा ब्लॉक में परिवर्तित सभी संकेतों के मूल्यों को पूरी तरह से निर्धारित किया जाना चाहिए। अन्यथा, सिंथेसाइज़र को सर्किट - लैच में मेमोरी तत्वों को सम्मिलित करना होगा।

उदाहरण के लिए, निम्नलिखित प्रक्रिया ब्लॉक पर विचार करें:

wire a,b;

reg res;

always @*

begin

if(a & b) res = 1;

else if (!a & b) res = 0;

end

प्रक्रियात्मक इकाई यह नहीं बताती है कि क्या होता है यदि b = 0. यदि b = 0 है, तो Res का मान नहीं बदलना चाहिए, भले ही a का मान हो। इसलिए, निम्नलिखित योजना को संश्लेषित किया जाएगा:

एक नियम के रूप में, सर्किट में कुंडी की उपस्थिति का मतलब कोड में त्रुटि है।

गैर-अवरुद्ध असाइनमेंटवे सभी कार्य जिन्हें हमने प्रक्रियात्मक ब्लॉक उदाहरणों में उपयोग किया था उन्हें वेरिलोग में "ब्लॉकिंग" असाइनमेंट कहा जाता है। वे एक प्रोग्रामर के लिए सामान्य तरीके से काम करते हैं।

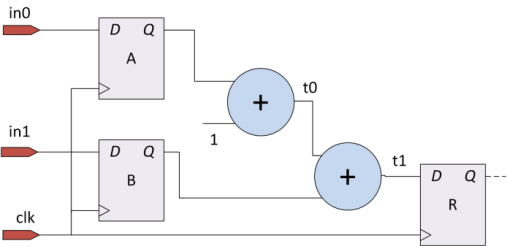

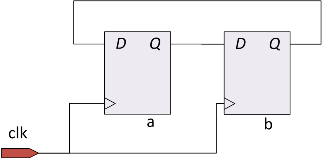

ब्लॉक असाइनमेंट के अलावा, वेरिलॉग के पास एक और प्रकार का असाइनमेंट है जो प्रक्रियात्मक ब्लॉकों में उपयोग किया जाता है - गैर-ब्लॉक असाइनमेंट, ऑपरेटर द्वारा निर्दिष्ट "<="। गैर-अवरुद्ध असाइनमेंट तुरंत उस स्थान पर नहीं किया जाता है, जहां यह घोषित किया गया है, लेकिन प्रक्रियात्मक ब्लॉक से बाहर निकलने तक स्थगित कर दिया जाता है। एक उदाहरण पर विचार करें:

reg a,b;

always @( posedge clk)

begin

a <= b;

b <= a;

end

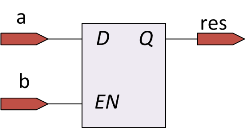

इस उदाहरण में, प्रत्येक माप पर, संकेत ए और बी मूल्यों का आदान-प्रदान करेंगे। संश्लेषित सर्किट इस प्रकार दिखेगा:

गैर-अवरोधक असाइनमेंट आमतौर पर रजिस्टरों के संचालन के तर्क का वर्णन करते समय उपयोग किया जाता है। ब्लॉक असाइनमेंट अधिक बार संयोजन पैटर्न का वर्णन करने के लिए उपयोग किया जाता है।

निष्कर्ष

यह वेरिलोग के छोटे परिचय का निष्कर्ष है। मुझे आशा है कि यह किसी के लिए उपयोगी था।

जो लोग वेरिलोग और डिजिटल सर्किट के डिजाइन से गहराई से परिचित होना चाहते हैं, उनके लिए मैं इन दो पुस्तकों की सिफारिश कर सकता हूं: