मुझे लगता है कि FPGA के साथ काम करने वाले कई लोगों ने सोचा - और नहीं कि आपके कंप्यूटर को पूरी तरह से उस पर बनाना है, एक x86 प्रोसेसर, बाह्य उपकरणों और अधिक के साथ? 8-बिट कंप्यूटरों को अक्सर FPGA में लागू किया जाता था, लेकिन यहाँ एक पूरा पीसी है ...

सफल संचालन के लिए, x86 प्रोसेसर के अलावा, आपको सभी कार्यान्वित इंटरप्ट (एसडी कार्ड पर "डिस्क" तक पहुंच सहित), एक वीजीए-संगत वीडियो कार्ड का BIOS, सभी बाह्य उपकरणों, एक मेमोरी कंट्रोलर, एक टाइमर और बहुत कुछ के साथ एक BIOS की भी आवश्यकता है। पहली नज़र में लगता है कि यह कार्य बहुत अधिक जटिल है, लेकिन फिर भी, इसे

ZetCPU परियोजना में हल किया गया था।

सीमाओं में से - केवल 16-बिट मोड 12.5Mhz पर काम करता है, गणितीय गणक के बिना।

लोहा

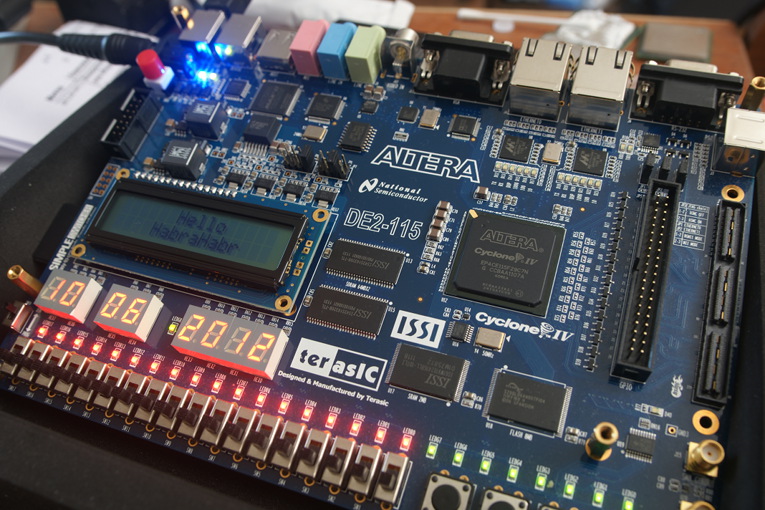

शुरू करने के लिए, हमें FPGA के साथ एक डिबग बोर्ड की आवश्यकता है। मुझे वास्तव में

टेरासिक DE2-115 बोर्ड (

एल्टर साइक्लोन IV पर 115k। LE के साथ) पसंद आया। एक चिप के खुदरा मूल्य से कम छात्र की कीमत $ 299 है।

बोर्ड पर बहुत सारे बिल्ट-इन आयरन हैं - 2 जिसमें 8MB SDRAM मेमोरी, 256KB SRAM, 1MB फ्लैश मेमोरी, 2 PHY 1Gb इथरनेट, VGA, LED / स्विच / बटन, SD कार्ड स्लॉट और बहुत कुछ कनेक्ट करने के लिए VideoDAC है। लेकिन इस परियोजना में सभी का उपयोग नहीं किया जाता है (केवल एसडी कार्ड, फ्लैश, एसडीआरएएम और वीडियोडैक)।

इसके अलावा, परियोजना को $ 59 के छात्र मूल्य के साथ

DE0 नैनो पर लॉन्च किया जा सकता है, लेकिन केवल पाठ मोड वहां काम करेगा।

हम लॉन्च करते हैं

इंस्टॉलेशन में कई गैर-स्पष्ट बिंदु हैं जो

निर्देशों में वर्णित नहीं हैं:

- बोर्ड को DE2_115_ControlPanel.sof फर्मवेयर डाउनलोड करें

- DE2 ControlPanel लॉन्च करें और निर्देशों के अनुसार BIOS और बूट डिस्केट को फ्लैश मेमोरी में भरें

- हम win32- छवि-लेखक का उपयोग करके एसडी कार्ड को हार्ड डिस्क की छवि लिखते हैं, WinImage को नहीं - यह बड़े कार्ड के साथ बूट छवि को तोड़ता है

- हम BIOS / VGA BIOS संकलित करते हैं या हम इंस्टॉलेशन आर्काइव से रेडीमेड तैयार करते हैं

- हम अपने पीसी-कार्ड को कर्टस में वेरिलोग में लिखे गए संकलन के लिए संकलित करते हैं या हम तैयार किए गए kotku.sof को लेते हैं और इसे बोर्ड पर फ्लैश करते हैं

अब आप एक मॉनिटर, PS / 2 कीबोर्ड को बोर्ड से जोड़ सकते हैं - और इसे :-)

आप प्रोसेसर में अपने निर्देश जोड़ सकते हैं, आपकी परिधीय, किसी भी निर्देश का कार्यान्वयन verilog स्रोत में देख सकते हैं ...

पूर्णांक विभाजन का एक उदाहरण कार्यान्वयनmodule zet_div_uu(clk, ena, z, d, q, s, div0, ovf);

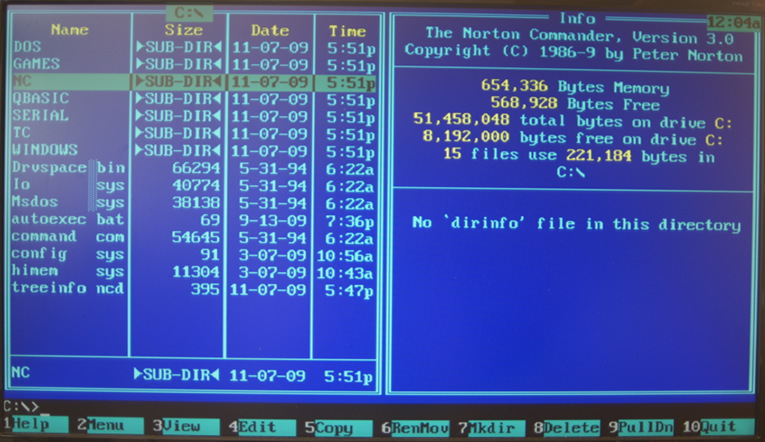

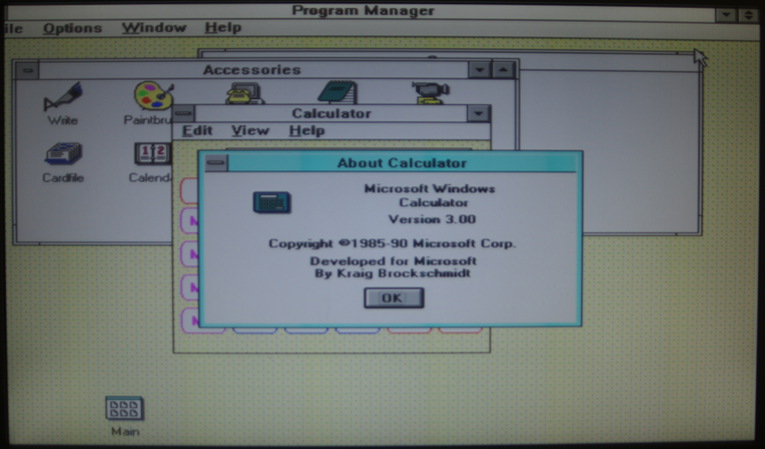

हम परीक्षा पास करते हैं

मैं स्क्रीन प्रतियों के लिए अग्रिम माफी चाहता हूं:

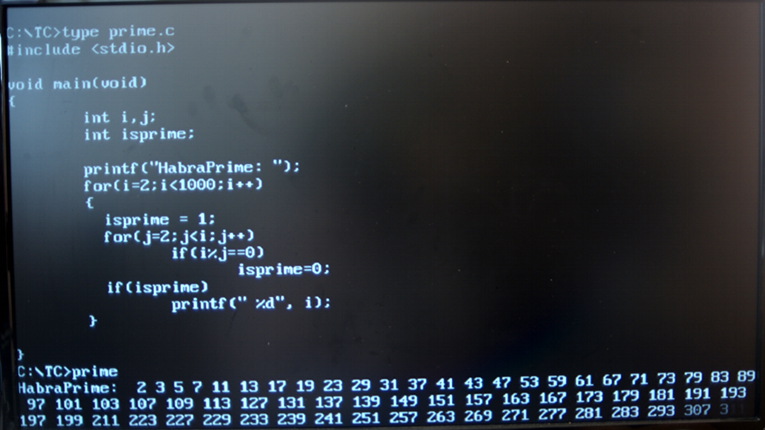

अगला प्रोग्रामिंग है। संकलन और निष्पादन की गति उदासीनता को जन्म देती है ...

निष्कर्ष

मुझे उम्मीद है कि लेख ने आपको FPGA की शक्ति पर विश्वास किया और वेरिलॉग का अध्ययन करना जारी रखा।

और किसी को अब अपने पीसी-लाठी बनाने के लिए एक सपना सच हो सकता है :-)

प्रश्न / टिप्पणी?