सिद्धांत

सामान्य जानकारी

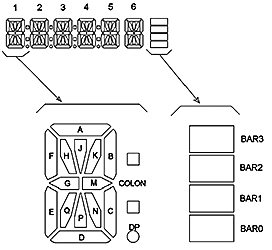

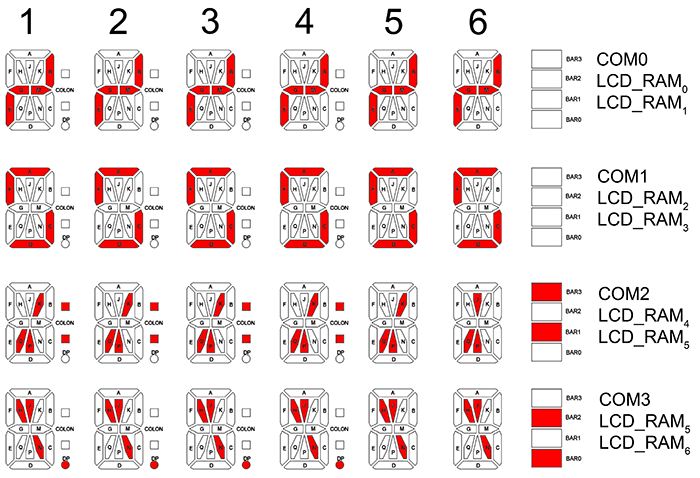

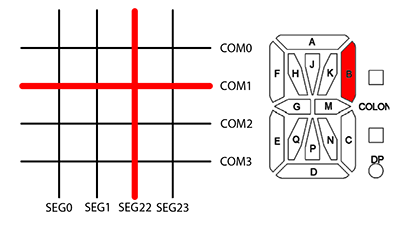

STM32L- डिस्कवरी डिबग बोर्ड में एक लिक्विड क्रिस्टल इंडिकेटर (एलसीडी, इंग्लिश एलसीडी। लिक्विड क्रिस्टल डिस्प्ले) है, जिसमें छह 14 सेगमेंट कैरेक्टर, 4 कोलन कैरेक्टर (कोलन), 4 डॉट्स (DP), 4 स्ट्रिप्स (बार) हैं। सभी खंडों को 24 खंडों में से प्रत्येक को OM0, COM1, COM2, COM3 समूहों में जोड़ा जाता है। प्रत्येक समूह का अपना अलग "सामान्य तार" होता है।

माइक्रोकंट्रोलर STM32L152RBT6 डिबग बोर्ड पर स्थापित है। माइक्रोकंट्रोलर में एक एकीकृत एलसीडी नियंत्रक होता है जो मोनोक्रोम एलसीडी संकेतक को नियंत्रित करता है।

एलसीडी नियंत्रक:

- आपको रिफ्रेश रेट (फ्रेम रेट - फ्रीक्वेंसी जिसके साथ एलसीडी पर जानकारी अपडेट होती है)

- स्थिर और मल्टीप्लेक्स नियंत्रण मोड का समर्थन करता है

- सॉफ्टवेयर कंट्रास्ट सेटिंग का समर्थन करता है

- नियंत्रण वोल्टेज के कई स्तरों के उपयोग की अनुमति देता है (चार तक)

- यह डबल बफ़रिंग का उपयोग करता है, जो प्रदर्शित जानकारी की अखंडता का उल्लंघन किए बिना प्रोग्राम निष्पादन के किसी भी समय LCD_RAM रजिस्टरों में डेटा अपडेट करने की अनुमति देता है

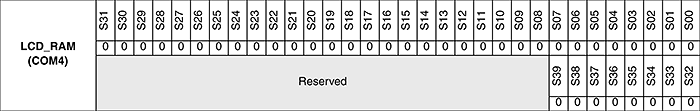

एलसीडी नियंत्रक स्मृति रजिस्टरों

STM32L152RB माइक्रोकंट्रोलर में विशेष LCD_RAM रजिस्टर होता है, जिसमें संग्रहित जानकारी खंड समूह COM0 - COM3 से मेल खाती है। प्रत्येक समूह दो 32 बिट रजिस्टरों से मेल खाता है। इस तरह के कई रजिस्टर डिबग बोर्ड पर स्थापित किए गए से अधिक सेगमेंट के साथ माइक्रोकंट्रोलर को एलसीडी को नियंत्रित करने की अनुमति देते हैं।

एलसीडी को 176 सेगमेंट के साथ नियंत्रित करने के लिए, 4 COM0 - COM3 में से प्रत्येक 44 सेगमेंट का उपयोग किया जाता है, 320 सेगमेंट वाले एलसीडी को नियंत्रित करने के लिए, 40 कॉम्प्लेक्स के 8 COM0 - COM7 समूहों का उपयोग किया जाता है।

STM32L-डिस्कवरी डिबग बोर्ड 96 खंडों के साथ 4 खंड COM0 - COM3 में 24 खंडों के साथ एक एलसीडी का उपयोग करता है।

STM32L-डिस्कवरी डिबग बोर्ड पर एलसीडी इस तरह से जुड़ा हुआ है कि बिट्स S40, प्रत्येक समूह में दूसरे LCD_RAM रजिस्टरों के S41 और पहले LCD_RAM रजिस्टरों के S0-S27 का उपयोग किया जाता है। उपयोग किए जाने वाले रजिस्टरों की संख्या को कम करने के लिए, बिट्स S40-S43 की जानकारी मुक्त बिट्स S28-S31 में रीमेक फ़ंक्शन का उपयोग करके दर्ज की जाएगी।

फ्रीक्वेंसी डिवाइडर ब्लॉक

फ़्रिक्वेंसी जनरेटर ब्लॉक आपको एलसीडी पर 32 kHz से 1 MHz तक की सीमा में विभिन्न फ्रेम दर प्राप्त करने की अनुमति देता है। घड़ी संकेत के स्रोत के रूप में इस्तेमाल किया जा सकता है:

- 32 kHz बाहरी कम आवृत्ति थरथरानवाला (LSE। कम गति बाहरी)

- 37 kHz आंतरिक कम आवृत्ति थरथरानवाला (LSI। कम गति आंतरिक)

- 2.48 और 16 की आवृत्ति डिवाइडर के साथ बाहरी आरएफ जनरेटर और 1 मेगाहर्ट्ज की अधिकतम आवृत्ति। (एचएसई। उच्च गति बाहरी)

सटीक तुल्यकालन को प्राप्त करने और एलसीडी खंडों में डीसी वोल्टेज पूर्वाग्रह को कम करने के लिए, घड़ी स्रोत स्थिर होना चाहिए। LCDCLK क्लॉक सिग्नल को LCD कंट्रोलर को भेजा जाता है। घड़ी की आवृत्ति को विभाजन के गुणांक के अनुसार विभाजित किया गया है, जो LCD_FCR रजिस्टर (फ्रेम कंट्रोल रजिस्टर) के PS [3: 0], DIV [3: 0] बिट्स के साथ सेट किए गए हैं। आवृत्ति डिवाइडर के ब्लॉक के आउटपुट पर परिणामी आवृत्ति की गणना सूत्र द्वारा की जाती है:

f

ck_div = F

LCDCLK / (2

PS * (16 + DIV))

फ्रेम दर की गणना सूत्र द्वारा की जाती है:

f

फ्रेम = f

ck_div * कर्तव्य

जहां कर्तव्य है, कर्तव्य चक्र अपनी अवधि के लिए नाड़ी अवधि का अनुपात है। एक फ्रेम के दौरान, रजिस्टरों LCD_RAM [x], LCD_RAM [x + 1] और इसी तरह से क्रमिक रूप से एलसीडी पर प्रदर्शित की जाती है। डिबग बोर्ड पर स्थापित एलसीडी के लिए, एक फ्रेम के लिए, एलसीडी नियंत्रक को COM0 - COM3 खंडों के 4 समूहों से जानकारी का उत्पादन करना चाहिए, इसलिए, एक समूह के लिए नियंत्रण पल्स अवधि फ्रेम अवधि का 1/4 होगी, अर्थात। कर्तव्य = १/४।

एलसीडी प्रबंधन

एलसीडी को नियंत्रित करने के दो तरीके हैं- स्टैटिक कंट्रोल मोड और मल्टीप्लेक्स कंट्रोल मोड। एक स्थिर संकेत के साथ, सूचक निर्वहन का प्रत्येक खंड माइक्रोकंट्रोलर के आउटपुट से जुड़ा हुआ है। एलसीडी के संबंध में, STM32LDiscovery डिबग बोर्ड पर, आपको माइक्रोकंट्रोलर के 6 * 14 = 84 पिन (कॉलोन, डॉट्स और स्ट्रिप्स को छोड़कर) की आवश्यकता होगी। इतने सारे पिन के उपयोग के कारण, अन्य बाह्य उपकरणों से जुड़ना असंभव हो जाएगा। STM32L152RB माइक्रोकंट्रोलर में 64 पिन हैं। मल्टीप्लेक्स कंट्रोल मोड (गतिशील नियंत्रण मोड) में, संकेतक बिट्स के समान खंडों को समूहों में जोड़ा जाता है। सूचना संकेतक बिट्स के वैकल्पिक प्रज्वलन के कारण प्रदर्शित होती है, जिसकी आवृत्ति मानव आंख से नहीं होती है।

मल्टीप्लेक्स नियंत्रण आपको बड़ी संख्या में खंडों का प्रबंधन करने की अनुमति देता है। प्रत्येक तत्व को अलग से नियंत्रित करने के बजाय, उन्हें पंक्तियों और स्तंभों (COM और SEG) द्वारा संबोधित किया जा सकता है, इस प्रकार नियंत्रण सर्किट को सरल बनाया जा सकता है, क्योंकि प्रत्येक खंड को अपनी नियंत्रण रेखा की आवश्यकता नहीं होती है। चयनित सेगमेंट को सक्षम करने के लिए, संभावित अंतर COM और SEG को इसे लागू करना आवश्यक है। संकेतक के पहले निर्वहन का एक उदाहरण ("1:" संकेतक पर प्रदर्शित होता है):

सूचक का पहला अंक समय 0 पर

सूचक का पहला अंक समय 0 पर समय पर सूचक का पहला अंक t 1

समय पर सूचक का पहला अंक t 1 समय टी 2 पर सूचक का पहला अंक

समय टी 2 पर सूचक का पहला अंक खंडों को एलसीडी टर्मिनलों से जोड़ने की सामान्य योजना

खंडों को एलसीडी टर्मिनलों से जोड़ने की सामान्य योजना माइक्रोकंट्रोलर के बंदरगाहों पर एलसीडी टर्मिनलों को जोड़ने की योजना

माइक्रोकंट्रोलर के बंदरगाहों पर एलसीडी टर्मिनलों को जोड़ने की योजनासेगमेंट लाइनों के लिए, एक नियंत्रण वोल्टेज का उपयोग किया जाता है, जिसके स्तर की संख्या पूर्वाग्रह गुणांक द्वारा निर्धारित की जाती है। डीबग बोर्ड पर एलसीडी ड्यूटी = 1/4 और पूर्वाग्रह = 1/3 के साथ मल्टीप्लेक्स कंट्रोल मोड का उपयोग करता है। कर्तव्य और पूर्वाग्रह का मान DUTY [2: 0] और BIAS [1: 0] बिट्स में LCD_CR (नियंत्रण रजिस्टर) के माध्यम से निर्धारित किया जाता है।

अभ्यास

माइक्रोकंट्रोलर पोर्ट को कॉन्फ़िगर करना

एलसीडी को नियंत्रित करने के लिए, माइक्रोकंट्रोलर के बंदरगाहों को तदनुसार कॉन्फ़िगर किया जाना चाहिए:

- बाहर निकलने पर

- वैकल्पिक फ़ंक्शन AF 11 (वैकल्पिक फ़ंक्शन) का उपयोग करना

- 400 kHz पोर्ट पर आउटपुट फ्रिक्वेंसी है

- पुश-पुल मोड का उपयोग करें

- पुल-अप प्रतिरोधों के बिना

जब पोर्ट वैकल्पिक फ़ंक्शन मोड में होता है, तो पोर्ट के आउटपुट डेटा बफर को परिधि से संकेतों द्वारा नियंत्रित किया जाता है। CMSIS लाइब्रेरी के हेडर फ़ाइल stm32lxx.h में सभी परिधीय रजिस्टरों का विवरण है, साथ ही उनकी पहुंच संरचना भी है।

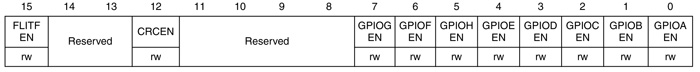

एलसीडी पिन माइक्रोकंट्रोलर के GPIOA (PA1-PA3, PA8-PA10, PA15), GPIOB (PB3-PB5, PB8-PB15), GPIOC (PC0-PC3, PC6-PC11) पोर्ट से जुड़े हैं। एलसीडी काम करने के लिए, चयनित बंदरगाहों पर एक घड़ी संकेत लागू किया जाना चाहिए। माइक्रोकंट्रोलर के GPIO पोर्ट की क्लॉकिंग RCC (रीसेट एंड क्लॉक कंट्रोल) सिस्टम के AHB बस से आती है - क्लॉकिंग और रीसेट सिस्टम। RCC_AHBENR (AHB परिधीय घड़ी सक्षम रजिस्टर) रजिस्टर में संबंधित बिट्स सेट करके घड़ी सिग्नल की आपूर्ति की जाती है।

रजिस्टर RCC_AHBENR (यह आंकड़ा पहले 15 अंक दिखाता है)

रजिस्टर RCC_AHBENR (यह आंकड़ा पहले 15 अंक दिखाता है)GPIOA, GPIOB, GPIOC पोर्ट के लिए, रजिस्टर के 1 से 0, 1, 2 बिट्स सेट करना आवश्यक है।

अगला, मैं कोड को बिटमास्क और हेक्साडेसिमल कोड का उपयोग करके जानकारी लिखने के लिए कोड का हवाला दूंगा। बिटमास्क का उपयोग करना अधिक सुविधाजनक है, लेकिन हेक्साडेसिमल कोड के साथ काम करना आपको रजिस्टरों के साथ काम करने के सार को समझने की अनुमति देता है।

RCC->AHBENR |=(RCC_AHBENR_GPIOAEN|RCC_AHBENR_GPIOBEN|RCC_AHBENR_GPIOCEN); RCC->AHBENR = 0x7;

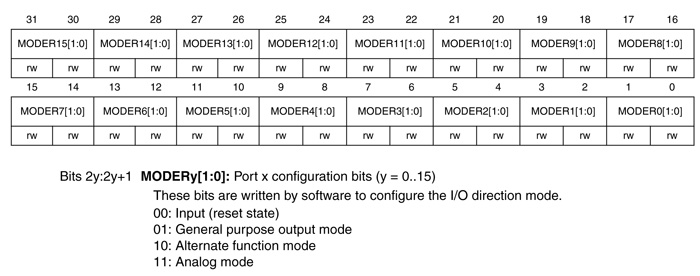

GPIOx_MODER (GPIO पोर्ट मोड रजिस्टर) रजिस्टर (x = A..H) का उपयोग पोर्ट ऑपरेटिंग मोड को इंगित करने के लिए किया जाता है। रजिस्टर के सभी बिट्स को MODERy समूहों [1: 0] में वर्गीकृत किया गया है, जहां y संबंधित पोर्ट का पिन नंबर है। पोर्ट को वैकल्पिक फ़ंक्शन मोड के लिए कॉन्फ़िगर किया जाना चाहिए, अर्थात पिन के लिए जिम्मेदार समूह में, मान को 10 पर सेट करें। GPIOA पोर्ट के लिए, आपको पिन 1-3.8-10.15 को कॉन्फ़िगर करने की आवश्यकता है, अर्थात 1 से 3,5,7,17,19,21,31 बिट्स सेट करें।

GPIOx_MODER रजिस्टर (GPIO पोर्ट मोड रजिस्टर)

GPIOx_MODER रजिस्टर (GPIO पोर्ट मोड रजिस्टर) GPIOA->MODER |= (GPIO_MODER_MODER1_1 | GPIO_MODER_MODER2_1 | GPIO_MODER_MODER3_1 | GPIO_MODER_MODER8_1 | GPIO_MODER_MODER9_1 | GPIO_MODER_MODER10_1 | GPIO_MODER_MODER15_1); GPIOA->MODER = 0x802A00A8; /* 0x802A00A8=1000 0000 0010 1010 0000 0000 1010 1000 */ GPIO_MODER_MODER2_1 | GPIO_MODER_MODER3_1 | GPIO_MODER_MODER8_1 | GPIO_MODER_MODER9_1 | GPIO_MODER_MODER10_1 | GPIO_MODER_MODER15_1); GPIOA->MODER |= (GPIO_MODER_MODER1_1 | GPIO_MODER_MODER2_1 | GPIO_MODER_MODER3_1 | GPIO_MODER_MODER8_1 | GPIO_MODER_MODER9_1 | GPIO_MODER_MODER10_1 | GPIO_MODER_MODER15_1); GPIOA->MODER = 0x802A00A8; /* 0x802A00A8=1000 0000 0010 1010 0000 0000 1010 1000 */

माइक्रोकंट्रोलर पोर्ट्स को पुश-पुल मोड में रखा जाना चाहिए। इसके लिए, GPIOx_OTYPER (GPIO पोर्ट आउटपुट टाइप रजिस्टर) रजिस्टर में पिन के लिए जिम्मेदार बिट्स में 1 सेट करना आवश्यक है।

GPIOx_OTYPER रजिस्टर (GPIO पोर्ट आउटपुट प्रकार रजिस्टर)

GPIOx_OTYPER रजिस्टर (GPIO पोर्ट आउटपुट प्रकार रजिस्टर) GPIOA->OTYPER &= ~(GPIO_OTYPER_OT_1 | GPIO_OTYPER_OT_2 | GPIO_OTYPER_OT_3 | GPIO_OTYPER_OT_8 | GPIO_OTYPER_OT_9 | GPIO_OTYPER_OT_10 | GPIO_OTYPER_OT_15); GPIOA->OTYPER &= ~0x0000870E; /* 0x870E=1000 0111 0000 1110 */ | GPIO_OTYPER_OT_2 | GPIO_OTYPER_OT_3 | GPIO_OTYPER_OT_8 | GPIO_OTYPER_OT_9 | GPIO_OTYPER_OT_10 | GPIO_OTYPER_OT_15); GPIOA->OTYPER &= ~(GPIO_OTYPER_OT_1 | GPIO_OTYPER_OT_2 | GPIO_OTYPER_OT_3 | GPIO_OTYPER_OT_8 | GPIO_OTYPER_OT_9 | GPIO_OTYPER_OT_10 | GPIO_OTYPER_OT_15); GPIOA->OTYPER &= ~0x0000870E; /* 0x870E=1000 0111 0000 1110 */

दोनों विकल्प चयनित पिंस को प्रभावित करते हैं। (GPIOA पोर्ट के लिए, पिन 1-3.8-10.15 कॉन्फ़िगर किए गए हैं)। यदि आपको पोर्ट के सभी पिन को पुश-पुल मोड में रखने की आवश्यकता है, तो आप रजिस्टर में मूल्य लिख सकते हैं:

GPIOA->OTYPER = 0x0;

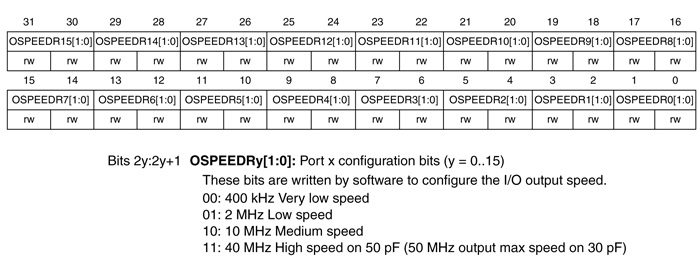

GPIOx_OSPEEDR (GPIO पोर्ट आउटपुट स्पीड रजिस्टर) का उपयोग पोर्ट में सूचना आउटपुट की आवृत्ति को इंगित करने के लिए किया जाता है। सभी रजिस्टर बिट्स को OSPEEDRy [1: 0] समूहों में बांटा गया है, जहां y संबंधित पोर्ट का पिन नंबर है। इस काम में, 400 kHz की आवृत्ति अर्थात् पिन के लिए जिम्मेदार समूह में, मान को 00 पर सेट करें।

GPIOx_OSPEEDR रजिस्टर (GPIO पोर्ट आउटपुट स्पीड रजिस्टर)

GPIOx_OSPEEDR रजिस्टर (GPIO पोर्ट आउटपुट स्पीड रजिस्टर) GPIOA->OSPEEDR &= ~(GPIO_OSPEEDER_OSPEEDR1 | GPIO_OSPEEDER_OSPEEDR2 | GPIO_OSPEEDER_OSPEEDR3 | GPIO_OSPEEDER_OSPEEDR8 | GPIO_OSPEEDER_OSPEEDR9 | GPIO_OSPEEDER_OSPEEDR10 | GPIO_OSPEEDER_OSPEEDR15); GPIOA->OSPEEDR &= ~0xC03F00FC; /*0xC03F00FC=1100 0000 0011 1111 0000 0000 1111 1100 */

यदि सभी पिनों के लिए 400 kHz पोर्ट पर आउटपुट आवृत्ति सेट करना आवश्यक है, तो आप रजिस्टर में मूल्य लिख सकते हैं:

GPIOA->OSPEEDR = 0x0;

GPIOx_PUPDR (GPIO पोर्ट पुलअप / पुल-डाउन रजिस्टर) का उपयोग चयनित पिन के लिए पुल-अप और पुल-डाउन पुल-अप प्रतिरोधों को निष्क्रिय करने के लिए किया जाता है। रजिस्टर के सभी बिट्स को PUPDRy समूहों में वर्गीकृत किया जाता है [1: 0], जहां y संबंधित पोर्ट का पिन नंबर है। पिन के लिए जिम्मेदार समूह में पुल-अप प्रतिरोधों को अक्षम करने के लिए, मान 00 सेट किया गया है।

GPIOx_PUPDR रजिस्टर (GPIO पोर्ट पुल-अप / पुल-डाउन रजिस्टर)

GPIOx_PUPDR रजिस्टर (GPIO पोर्ट पुल-अप / पुल-डाउन रजिस्टर) GPIOA->PUPDR &= ~(GPIO_PUPDR_PUPDR1 | GPIO_PUPDR_PUPDR2 | GPIO_PUPDR_PUPDR3 | GPIO_PUPDR_PUPDR8 | GPIO_PUPDR_PUPDR9 | GPIO_PUPDR_PUPDR10 | GPIO_PUPDR_PUPDR15); GPIOA->PUPDR &= ~0xC03F00FC; /*0xC03F00FC=1100 0000 0011 1111 0000 0000 1111 1100 */

यदि सभी पिनों के लिए पुल-अप प्रतिरोधों को निष्क्रिय करना आवश्यक है, तो आप रजिस्टर में मूल्य लिख सकते हैं:

GPIOA->PUPDR = 0x0;

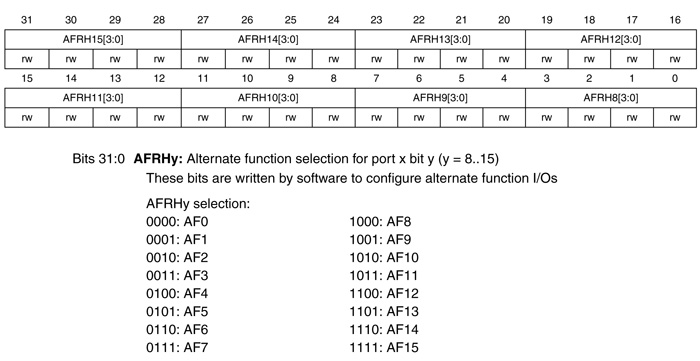

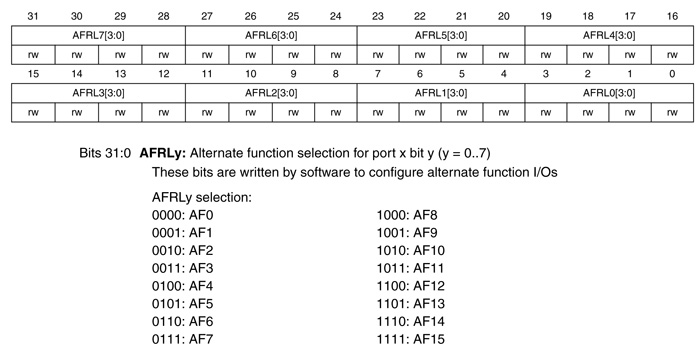

माइक्रोकंट्रोलर के बंदरगाहों के लिए एक वैकल्पिक फ़ंक्शन का उपयोग करने के लिए, दो रजिस्टर GPIOx_AFRL (GPIO वैकल्पिक फ़ंक्शन कम रजिस्टर), जो कम पिन (0 से 7) और GPIOx_AFRH (GPIO वैकल्पिक फ़ंक्शन उच्च रजिस्टर) के लिए जिम्मेदार है, जो उच्च पिन (8 से 15 तक) के लिए जिम्मेदार है। रजिस्टरों के सभी बिट्स को AFRLy [3: 0] और AFRHy [3: 0] समूहों में बांटा गया है, जहाँ y संबंधित पोर्ट का पिन नंबर है। पोर्ट को वैकल्पिक फ़ंक्शन AF11 का उपयोग करने के लिए कॉन्फ़िगर किया जाना चाहिए, इसके लिए, पिन के लिए जिम्मेदार समूह में, मान 1011 सेट किया जाना चाहिए।

GPIOx_AFRL रजिस्टर (GPIO वैकल्पिक फ़ंक्शन कम रजिस्टर)

GPIOx_AFRL रजिस्टर (GPIO वैकल्पिक फ़ंक्शन कम रजिस्टर) GPIOx_AFRH रजिस्टर (GPIO वैकल्पिक कार्य उच्च रजिस्टर)

GPIOx_AFRH रजिस्टर (GPIO वैकल्पिक कार्य उच्च रजिस्टर)ऐसा करने के लिए, रजिस्टरों में मान लिखें:

GPIOA->AFR[0] = 0xBBB0; GPIOA->AFR[1] = 0xB0000BBB;

AFR [0] = 0xBBB0 - GPIOx_AFRL रजिस्टर का मान लिखता है।

AFR [1] = 0xB0000BBB - GPIOx_AFRH रजिस्टर का मान लिखता है।

इसी GPIOB, GPIOC पोर्ट पिन की सेटिंग उसी तरह से बनाई गई हैं।

एलसीडी नियंत्रक सेटअप

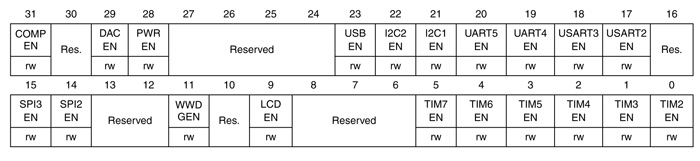

एलसीडी नियंत्रक के साथ काम करते समय, अन्य बाह्य उपकरणों के साथ, इसके लिए एक घड़ी संकेत लागू करना आवश्यक है। बिजली प्रबंधन प्रणाली के लिए एक घड़ी संकेत भी प्रदान किया जाता है। कंट्रोलर और पावर मैनेजमेंट सिस्टम क्लॉकिंग के लिए APB1 बस का उपयोग करते हैं। RCC_APB1ENR रजिस्टर (APB1 परिधीय घड़ी सक्षम रजिस्टर) में क्लॉकिंग सक्षम करने के लिए, 9 वें और 28 वें अंक में 1 सेट करना आवश्यक है।

रजिस्टर RCC_APB1ENR (APB1 परिधीय घड़ी सक्षम रजिस्टर)

रजिस्टर RCC_APB1ENR (APB1 परिधीय घड़ी सक्षम रजिस्टर) RCC->APB1ENR |= RCC_APB1ENR_PWREN|RCC_APB1ENR_LCDEN; RCC->APB1ENR |= 0x10000200;

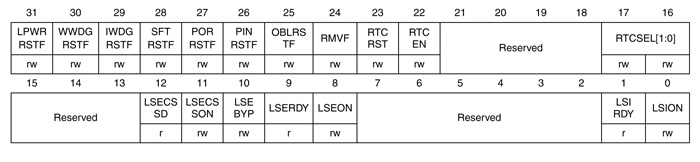

एलसीडी नियंत्रक के संचालन के लिए, घड़ी संकेतों के स्रोत को इंगित करना आवश्यक है। स्रोत रजिस्टर RCC_CSR में इंगित किया गया है। डिफ़ॉल्ट रूप से, इस रजिस्टर पर लिखना प्रतिबंधित है। पॉवर कंट्रोल रजिस्टर PWR_CR (पीडब्लूआर पॉवर कंट्रोल रजिस्टर) में, RCC_CSR रजिस्टर में सुरक्षा लिखी जाती है। RCC_CSR रजिस्टर आरटीसी और एलसीडी नियंत्रक के घड़ी स्रोतों को नियंत्रित करता है

RCC_CSR रजिस्टर को लिखना PWR_CR रजिस्टर के 1 से 8 वें अंक को सेट करने में सक्षम है।

PWR_CR रजिस्टर (PWR पावर कंट्रोल रजिस्टर)

PWR_CR रजिस्टर (PWR पावर कंट्रोल रजिस्टर) PWR->CR |= PWR_CR_DBP; PWR->CR |= 0x100;

LCD कंट्रोलर (और RTC क्लॉक) के क्लॉक सोर्स को बदलने के लिए, आपको पहले RCC_CSR (कंट्रोल / स्टेटस रजिस्टर) रजिस्टर में RTCRST बिट (सेटिंग 1 से 23 वें बिट) सेट करके क्लॉक सोर्स को रीसेट करना होगा।

रजिस्टर RCC_CSR (नियंत्रण / स्थिति रजिस्टर)

रजिस्टर RCC_CSR (नियंत्रण / स्थिति रजिस्टर) RCC->CSR |= RCC_CSR_RTCRST;

या ऑपरेटर का उपयोग करके रजिस्टर के लिए एक मूल्य लिखकर | = =, क्योंकि द्वारा मूल्य

डिफ़ॉल्ट रजिस्टर 0x0 से अलग है:

RCC->CSR |= 0x800000;

एक नया घड़ी स्रोत चुनने के लिए, RTCRST बिट को निकालना आवश्यक है:

RCC->CSR &= ~RCC_CSR_RTCRST; RCC->CSR &= ~0x800000;

एक बाहरी बास जनरेटर घड़ी स्रोत के रूप में चुना गया है। RCC_CSR रजिस्टर में जनरेटर को सक्षम करने के लिए, LSEON बिट (1 से 8 बिट सेट) सेट करना आवश्यक है:

RCC->CSR |= RCC_CSR_LSEON; RCC->CSR |= 0x100;

जनरेटर को चालू करने के बाद, इसे स्थिर करने में कुछ समय लगता है। जनरेटर उपलब्धता RCC_CSR रजिस्टर में LSERDY बिट की हार्डवेयर सेटिंग द्वारा जाँच की जाती है:

while(!(RCC->CSR&RCC_CSR_LSERDY))

RCC_CSR रजिस्टर के RTCSEL [1: 0] समूह में मान 01 सेट करके बाहरी LF जनरेटर को घड़ी स्रोत के रूप में चुना गया है:

RCC->CSR |= RCC_CSR_RTCSEL_LSE; RCC->CSR |= 0x10000;

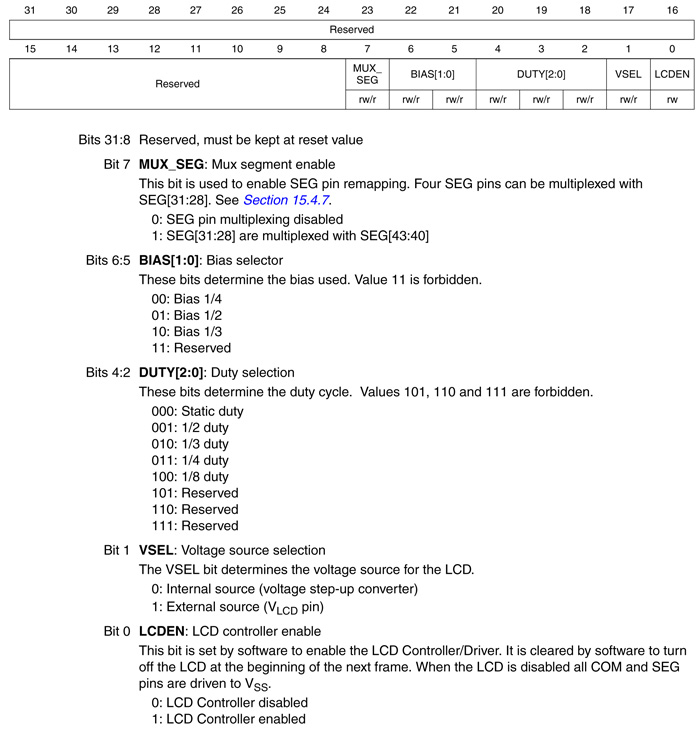

एलसीडी नियंत्रक में, आपको वांछित पूर्वाग्रह मोड सेट करना होगा। ऐसा करने के लिए, LCD_CR (LCD कंट्रोल रजिस्टर) रजिस्टर में, आपको 10 मूल्य BIAS समूह [1: 0] पर सेट करना होगा। बिट्स सेट करने से पहले, "कचरा" से बिट्स को साफ करना आवश्यक है।

रजिस्टर LCD_CR (LCD नियंत्रण रजिस्टर)

रजिस्टर LCD_CR (LCD नियंत्रण रजिस्टर)रीसेट करें बिट्स:

LCD->CR &= ~LCD_CR_BIAS; LCD->CR &= ~0x60;

बीमास का विकल्प = 1/3 बिटमास्क का उपयोग कर:

LCD->CR |= LCD_CR_BIAS_1; LCD->CR |= 0x40;

कर्तव्य निर्धारित करें = 1/4 मोड। ऐसा करने के लिए, पहले सभी बिट्स रीसेट करें:

LCD->CR &=~LCD_CR_DUTY; LCD->CR &= ~0x1C;

LCD_CR के लिए DUTY [1: 0] समूह के लिए मान 011 सेट करें

ड्यूटी मोड = 1/4:

LCD->CR |= LCD_CR_DUTY_0|LCD_CR_DUTY_1; LCD->CR |= 0x;

हम निष्कर्ष के पुनर्निर्देशन के कार्य को सक्रिय करते हैं। ऐसा करने के लिए, LCD_CR रजिस्टर के 7 वें अंक में 1 सेट करें:

LCD->CR |= LCD_CR_MUX_SEG; <source lang=«C»>LCD->CR |= 0x80;

हम LCDCLK घड़ी सिग्नल की आवृत्ति के विभाजन कारकों के मूल्यों को निर्धारित करते हैं। गुणांक LCD_FCR रजिस्टर (LCD फ्रेम कंट्रोल रजिस्टर) में सेट किए गए हैं। सबसे पहले, हम सभी बिट्स को भी साफ़ करते हैं, फिर आवश्यक सेट करते हैं।

रजिस्टर LCD_FCR (एलसीडी फ्रेम कंट्रोल रजिस्टर)

रजिस्टर LCD_FCR (एलसीडी फ्रेम कंट्रोल रजिस्टर) LCD->FCR &= ~LCD_FCR_PS; LCD->FCR &= ~LCD_FCR_DIV; LCD->FCR &= ~0x3C00000; LCD->FCR &= ~0x3C0000;

घड़ी की आवृत्ति के विभाजन गुणांक के मान ck_ps = LCDCLK / 16, ck_div = ck_ps / 17 के बराबर सेट किए गए हैं। ऐसा करने के लिए, 1 से 24 और 18 अंक निर्धारित करें:

LCD->FCR |= 0x1040000;

वांछित कंट्रास्ट स्तर सेट करने के लिए, CC समूह [१: ०] का मान ०१० निर्धारित करना आवश्यक है, साथ ही पुराने मानों से बिट्स को हटा दिया है:

LCD->FCR &= ~LCD_FCR_CC; LCD->FCR |= LCD_FCR_CC_1; LCD->FCR &= ~0x1C00; LCD->FCR |= 0x800;

सभी मान सेट करने के बाद, LCD_FCR रजिस्टर को सिंक्रनाइज़ करने में कुछ समय लगता है। LCD_SR रजिस्टर (LCD स्थिति रजिस्टर) में FCRSF बिट को हार्डवेयर सेटिंग द्वारा रजिस्टर सिंक्रोनाइज़ेशन की जाँच की जाती है।

रजिस्टर LCD_SR (एलसीडी स्थिति रजिस्टर)

रजिस्टर LCD_SR (एलसीडी स्थिति रजिस्टर) while(!(LCD->SR&LCD_SR_FCRSR))

एलसीडी के लिए वोल्टेज स्रोत के रूप में, वी

एलसीडी बनाने के लिए आंतरिक स्टेप-अप कनवर्टर का चयन करें। ऐसा करने के लिए, LCD_CR रजिस्टर (LCD नियंत्रण रजिस्टर) का पहला अंक 0 पर सेट है:

LCD->CR &= ~LCD_CR_VSEL; LCD->CR &= ~0x2;

LCD_CR रजिस्टर (LCD नियंत्रण रजिस्टर) के 1 से 0 बिट सेट करके एलसीडी कंट्रोलर के संचालन को सक्षम किया गया है:

LCD->CR |= LCD_CR_LCDEN; LCD->CR |= 0x1;

वोल्टेज स्रोत के रूप में आंतरिक स्टेप-अप कनवर्टर स्थापित करने के बाद, आपको इसकी तत्परता की प्रतीक्षा करनी चाहिए। उपलब्धता LCD_SR रजिस्टर (LCD स्थिति रजिस्टर) में RDY बिट हार्डवेयर सेटिंग द्वारा जाँच की जाती है:

while(!(LCD->SR&LCD_SR_RDY))

एलसीडी नियंत्रक के संचालन की अनुमति देने के बाद, इसकी तत्परता की प्रतीक्षा करना आवश्यक है। उपलब्धता LCD_SR रजिस्टर (LCD स्थिति रजिस्टर) में ENS बिट हार्डवेयर सेटिंग द्वारा जाँच की जाती है:

while(!(LCD->SR&LCD_SR_ENS))

एलसीडी इमेजिंग

संकेतक के सभी खंडों को समूह COM0 - COM3 में 24 खंडों (प्रत्येक SEG-SEG23) के साथ जोड़ा गया है। सेगमेंट के बारे में जानकारी LCD_RAM में LCD कंट्रोलर मेमोरी के रजिस्टरों में संग्रहीत होती है। पीसीबी लेआउट ऐसा है कि खंड संख्या LCD_RAM रजिस्टरों के अंकों के अनुरूप नहीं है।

एलसीडी के पहले अंक में 1 प्रदर्शित करने के लिए, 1 बी, 1 सी सेगमेंट को लाइट करना आवश्यक है। खंड 1 बी समूह COM0 का है, खंड 1C समूह COM1 का है। इसलिए, उनके बारे में जानकारी क्रमशः रजिस्टरों रैम [0] (LCD_RAM0), रैम [2] (LCD_RAM2) में दर्ज की जानी चाहिए। सेगमेंट 1B के लिए, LCDSEG22 आउटपुट जिम्मेदार है, जिसके बारे में जानकारी RAM रजिस्टर [1] (LCD_RAM1) के SEG40 श्रेणी में संग्रहीत है। पुन: असाइनमेंट फ़ंक्शन का उपयोग करते हुए, RAMSEG22 सेगमेंट के लिए RAM रजिस्टर [0] (LCD_RAM0) का SEG28 बिट जिम्मेदार होगा। खंड 1C के लिए, LCD LCDSEG1 का आउटपुट जिम्मेदार है, जिसके बारे में जानकारी RAM रजिस्टर [2] (LCD_RAM2) के SEG1 श्रेणी में संग्रहीत है।

LCD->RAM[0]= 0x10000000; LCD->RAM[2] = 0x2;

मेमोरी रजिस्टर में मान लिखने से पहले, यह जांचना आवश्यक है कि क्या एलसीडी में पिछला डेटा ट्रांसफर पूरा हो गया है। ऐसा करने के लिए, UDR (अपडेट डिस्प्ले अनुरोध) LCD_SR (एलसीडी स्टेटस रजिस्टर) रजिस्टर की जाँच की जाती है। एलसीडी कंट्रोलर में दो आउटपुट बफर होते हैं, सूचना को पहले बफर में दर्ज किया जाता है, और दूसरे बफर से एलसीडी पर प्रदर्शित किया जाता है। UDR बिट पहले बफर से दूसरे में ट्रांसमिशन के दौरान सेट किया जाता है, LCD_RAM रजिस्टरों को लिखने से बचाता है:

while(LCD->SR & LCD_SR_UDR)

LCD_RAM रजिस्टर में जानकारी लिखने के बाद, LCD_SR रजिस्टर (LCD स्थिति रजिस्टर) में UDR बिट सेट करना आवश्यक है (सेट 1 से 2 बिट):

LCD->SR |= LCD_SR_UDR; LCD->SR |= 0x4;

तैयार प्रोजेक्ट कोड #include "stm32l1xx.h" void gpio(void); void controller(void); int main() { gpio(); controller(); while(LCD->SR & LCD_SR_UDR); LCD->RAM[0]= 0x3E300FFF; LCD->RAM[2] = 0x2EB00382; LCD->RAM[6] = 0x400; LCD->SR |= LCD_SR_UDR; while(1); } void gpio(void) { RCC->AHBENR |= 0x7; GPIOA->MODER |= 0x802A00A8; GPIOB->MODER |= 0xAAAA0A80; GPIOC->MODER |= 0xAAA0AA; GPIOA->OTYPER &= ~0x870E; GPIOB->OTYPER &= ~0xFF38; GPIOC->OTYPER &= ~0xFCF; GPIOA->PUPDR &= ~0xC03F00FC; GPIOB->PUPDR &= ~0xFFFF0FC0; GPIOC->PUPDR &= ~0xFFF0FF; GPIOA->OSPEEDR &= ~0xC03F00FC; GPIOB->OSPEEDR &= ~0xFFFF0FC0; GPIOC->OSPEEDR &= ~0xFFFFF0FF; GPIOA->AFR[0] |= 0xBBB0; GPIOA->AFR[1] |= 0xB0000BBB; GPIOB->AFR[0] |= 0xBBB000; GPIOB->AFR[1] |= 0xBBBBBBBB; GPIOC->AFR[0] |= 0xBB00BBBB; GPIOC->AFR[1] |= 0xBBBB; } void controller(void) { RCC->APB1ENR |= 0x10000200; PWR->CR |= 0x100; RCC->CSR |= 0x800000; RCC->CSR &= ~0x800000; RCC->CSR |= 0x100; while(!(RCC->CSR&RCC_CSR_LSERDY)); RCC->CSR |= 0x10000; LCD->CR &= ~0x60; LCD->CR |= 0x40; LCD->CR &= ~0x1C; LCD->CR |= 0xC; LCD->CR |= 0x80; LCD->FCR &= ~0x3C00000; LCD->FCR &= ~0x3C0000; LCD->FCR |= 0x1040000; LCD->FCR &= ~0x1C00; LCD->FCR |= 0x800; while(!(LCD->SR&LCD_SR_FCRSR)); LCD->CR &= ~0x2; LCD->CR |= 0x1; while(!(LCD->SR&LCD_SR_RDY)); while(!(LCD->SR&LCD_SR_ENS)); }

UPD: गारिक्स उपयोगकर्ता

ने रैम रजिस्टरों के लिए मान उत्पन्न करने के लिए एक उपयोगी कार्यक्रम लिखासंदर्भ:

- http://chipspace.ru/ STM32L-DISCOVERY एलसीडी कनेक्ट करें

- http://easyelectronics.ru एआरएम। प्रशिक्षण पाठ्यक्रम

- http://radiokot.ru/ गतिशील संकेत

- STM32 L1 श्रृंखला के लिए डिस्कवरी किट - STM32L152 MCU के साथ