इतना समय पहले नहीं, मैंने पीसीआई उपकरणों के मतदान के लिए तंत्र के बारे में

पूछा । मुझे नौकरी मिलने के बाद, मैंने परीक्षण कार्य पूरा किया, और मैंने उसके बारे में पूछा, और सुरक्षित रूप से उसके बारे में भूल गया। लेकिन हाल ही में उन्होंने एक नया प्रोजेक्ट जारी किया और उन्हें सब कुछ याद रखना पड़ा, उसी समय मैंने यहाँ लिखने का फैसला किया।

पीसीआई बस में बहुत सारे लेनदेन हैं, केवल इस विषय में निम्नलिखित वर्णित किया जाएगा:

- कॉन्फ़िगरेशन लेनदेन

- मैं / हे लेनदेन

- मेमोरी एक्सेस लेनदेन

लेनदेन करते समय, 2 विकल्प संभव हैं:

- जब गुरु दक्षिण पुल होता है

- जब मास्टर पीसीआई बस से जुड़ा एक उपकरण है

जैसा कि पहले ही हुआ, पीसीआई बस पर विचार करते समय, मैं मास्टर डिवाइस को मास्टर कहूँगा, दास डिवाइस को लक्ष्य (लक्ष्य)।

यह लेख केवल लेनदेन से संबंधित है जब मास्टर दक्षिण पुल है, लेनदेन के बाद से जब मास्टर पीसीआई बस से जुड़ा एक उपकरण है, एक अलग लेख के हकदार हैं।

और इसलिए, बस के साथ काम करने के लिए, हमें निम्नलिखित संकेतों की आवश्यकता है:

entity main is Port ( clk : in std_logic; AD : inout std_logic_vector(31 downto 0); IDSEL : in std_logic; CBE : in std_logic_vector(3 downto 0); FRAME : in std_logic; IRDY : in std_logic; TRDY : inout std_logic; STOP : inout std_logic; PAR : inout std_logic; RST : in std_logic; DEVSEL : inout std_logic ); end main;

clk (क्लॉक) - PCI पर सभी लेनदेन का सिंक्रनाइज़ेशन प्रदान करता है, और प्रत्येक PCI डिवाइस के लिए एक इनपुट भी है।

AD (पता और डेटा) - बस का पता और डेटा बहुसंकेतन।

IDSEL (इनिशियलाइज़ेशन डिवाइस सिलेक्ट) - इनिशियलाइज़ेशन डिवाइस का चयन, कॉन्फ़िगरेशन पढ़ने और लिखने के दौरान चिप का चयन करने के लिए उपयोग किया जाता है।

CBE (बस कमांड और बाइट सक्षम) - बस कमांड और बाइट रिज़ॉल्यूशन।

फ्रेम (फ्रेम) - संकेत लेनदेन की शुरुआत में मास्टर द्वारा जारी किया जाता है और इसकी अवधि निर्धारित करता है। एकल-चरण लेनदेन के लिए, FRAME हमेशा एक घड़ी चक्र तक रहता है। मल्टीफ़ेज़ लेनदेन में, लेनदेन पूरा होने से पहले FRAME को एक चक्र हटा दिया जाता है।

IRDY (पहल तैयार) - गुरु की तत्परता का संकेत। यह वर्तमान डेटा चरण को पूरा करने के लिए विज़ार्ड की इच्छा को इंगित करता है।

TRDY (लक्ष्य तैयार) - लक्ष्य की तत्परता का संकेत, डेटा के वर्तमान चरण को पूरा करने के लिए लक्ष्य की तत्परता का संकेत देता है।

STOP (रोक) - यह संकेत एक लक्ष्य द्वारा जारी किया जाता है यदि वह वर्तमान लेनदेन को रोकना चाहता है।

PAR (समानता) - AD और CBE लाइनों पर समानता।

RST (रीसेट) - संकेत रीसेट करें। यह अतुल्यकालिक है।

DEVSEL (डिवाइस चयन) - डिवाइस चयन संकेत।

किसी भी उपकरण के साथ काम करने से पहले, इसे आरंभीकृत किया जाना चाहिए। इसलिए, हम कॉन्फ़िगरेशन लेनदेन निष्पादन की सुविधाओं पर विचार करते हैं।

कॉन्फ़िगरेशन लेनदेन सामान्य जानकारी।

OS से कॉन्फ़िगरेशन लेनदेन का दृश्यपीसी पर पीसीआई कॉन्फ़िगरेशन लेन-देन उत्पन्न करने के लिए, कॉनफिड_एडीआरडीएस और CONFIG_DATA नाम के दो I / O पोर्ट पर कॉल किया जाता है, क्रमशः 0CF8h और 0CFCh के पते के साथ, और होस्ट में शामिल किया गया - PCI पीसी जिसके माध्यम से पीसीआई बस सीधे या अप्रत्यक्ष रूप से प्रोसेसर से जुड़ती है।

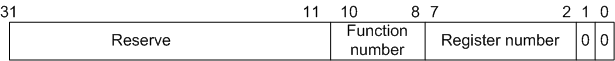

CONFIG_ADDRESS पोर्ट आकार में एक डबल शब्द है और केवल एक इकाई के रूप में उपलब्ध है। इससे संबंधित पतों पर छोटी कॉल को सामान्य I / O लेनदेन के रूप में PCI बस में स्थानांतरित कर दिया जाता है। यह पोर्ट पढ़ा और लिखा गया है और इसके निम्न प्रारूप हैं:

जब एक कॉन्फ़िगरेशन लेनदेन करना आवश्यक होता है, तो पीसीआई कॉन्फ़िगरेशन स्पेस रजिस्टर का पता इस पोर्ट को लिखा जाता है, जिसमें बस नंबर (बिट्स २३-१६), डिवाइस (१५-११), फ़ंक्शंस (१०-,), और रजिस्टर स्वयं (2-२) शामिल होता है। बिट्स 1 और 0 में हमेशा शून्य होना चाहिए, और सबसे महत्वपूर्ण बिट में एक होना चाहिए, जिससे कॉन्फ़िगरेशन लेनदेन का निष्पादन हो सके। अंक 30-24 आरक्षित हैं और इसमें शून्य होना चाहिए।

दरअसल, CONFIG_DATA पोर्ट को पढ़ते या लिखते समय कॉन्फ़िगरेशन लेन-देन उत्पन्न होता है, जब होस्ट-पीसीआई पुल से जुड़ी बस के लिए निर्धारित उच्च बिट और बस नंबर के साथ पता, या इस बस के नीचे स्थित किसी भी पीसीआई बस से कनेक्ट किया गया और CONFIG_ADDRESS के माध्यम से इसे कनेक्ट किया गया। एक या कई पीसीआई - पीसीआई पुल (बस संख्याओं की वैध सीमा इसके विन्यास के दौरान होस्ट - पीसीआई पुल द्वारा निर्दिष्ट है)। CONFIG_DATA पोर्ट पर पहुंच का आकार पढ़ने या लिखने के रजिस्टर के समान होना चाहिए, जिसका पता CONFIG_ADDRESS में है।

यदि CONFIG_ADDRESS में निर्दिष्ट बस संख्या होस्ट से जुड़ी हुई बस की संख्या से मेल खाती है - PCI ब्रिज, टाइप 0 के पते के साथ एक कॉन्फ़िगरेशन लेनदेन उत्पन्न होता है, और CONFIG_ADDRESS पोर्ट के 15-12 बिट्स में स्थित डिवाइस नंबर IDSEL संकेतों में से एक को जारी करने के लिए उपयोग किया जाता है। जिसका उपयोग किसी विशिष्ट डिवाइस को चुनने के लिए किया जाता है। इसके अलावा, कॉन्फ़िगरेशन लेनदेन के पता चरण में डिकोड किए गए डिवाइस नंबर (एक इकाई और शेष शून्य बिट्स) पते के 31-11 बिट्स में प्रेषित होता है।

यदि CONFIG_ADDRESS में पता होस्ट से सीधे जुड़ी गलत बस को इंगित करता है - PCI पुल, बाद वाला टाइप 1 के पते के साथ एक कॉन्फ़िगरेशन लेनदेन उत्पन्न करता है। यह PCI - PCI पुल द्वारा संसाधित किया जाएगा, जो पते में निहित बस नंबर को पहचान लेगा। यह पुल या तो टाइप 0 के पते के साथ एक कॉन्फ़िगरेशन लेनदेन को अंजाम देगा (यदि संबोधित डिवाइस इस पुल से सीधे जुड़ा हुआ है), या यह टाइप 1 के पते के साथ लेनदेन उत्पन्न करेगा, जिससे अगले पुल के माध्यम से इसका मार्ग सुनिश्चित होगा। इस श्रृंखला की लंबाई सैद्धांतिक रूप से बस संख्या (8 बिट्स) के लिए आवंटित क्षेत्र की थोड़ी गहराई से सीमित है।

यदि लेन-देन के दौरान यह पता चलता है कि कॉन्फ़िगरेशन रजिस्टर का पता मौजूद नहीं है (बस, डिवाइस, फ़ंक्शन, या रजिस्टर की संख्या मौजूद नहीं है), तो लेखन ऑपरेशन कोई कार्रवाई नहीं करेगा, और रीड ऑपरेशन प्रोसेसर में वापस आ जाएगा प्रत्येक श्रेणी में इकाइयों वाले एक मूल्य।

लेनदेन प्रकार 1 के लिए पता प्रारूप।

लेनदेन के लिए पता प्रारूप 0 है।

कॉन्फ़िगरेशन रजिस्टर का प्रारूप:

रजिस्टरों का न्यूनतम सेट:

- विक्रेता आईडी - फ़ील्ड डिवाइस के निर्माता की पहचान करता है। 0xFFFF मान का उपयोग करना निषिद्ध है।

- डिवाइस आईडी - क्षेत्र एक विशिष्ट प्रकार के डिवाइस की पहचान करता है। 0xFFFF मान का उपयोग करना निषिद्ध है।

- संशोधन आईडी - डिवाइस पहचानकर्ता के अलावा। शून्य हो सकता है।

- हैडर प्रकार - बहुक्रिया उपकरणों के लिए। यदि 7 वीं बिट 0 है, तो डिवाइस एकल-कार्यात्मक है, अन्यथा यह बहुआयामी है।

- कक्षा कोड - केवल पढ़ें डिवाइस की सामान्य कार्यक्षमता की पहचान करने के लिए उपयोग किया जाता है। उच्च बाइट (पता 0Bh) बेस क्लास, सबक्लास द्वारा मध्य, प्रोग्राम इंटरफ़ेस द्वारा कम (यदि मानकीकृत है) को परिभाषित करता है।

- सबसिस्टम आईडी, सबसिस्टम विक्रेता आईडी - निर्माता द्वारा निर्धारित। केवल पढ़ें वे पहचानकर्ताओं को संग्रहीत करते हैं जो कार्ड और उपकरणों की सटीक पहचान को सक्षम करते हैं (सिस्टम में स्थापित किए जा सकते हैं

डिवाइस और निर्माता पहचानकर्ताओं (डिवाइस आईडी और विक्रेता आईडी) के साथ कई कार्ड। - BAR0 - BAR5 - मेमोरी और इनपुट / आउटपुट पोर्ट का वर्णन करता है।

मेमोरी क्षेत्र और पोर्ट विवरण अलग-अलग हैं:

- बिट 0 = 0 मेमोरी का संकेत है। आकार में 2 जीबी से अधिक नहीं

- बिट 0 = 1 - बंदरगाह क्षेत्र का संकेत। आकार में 256 बाइट्स तक।

क्षेत्रों के आकार की गणना निम्नानुसार की जाती है। 0xFFFFFFFF बार को लिखा है। अगला, मान BAR से पढ़ा जाता है, और 0xFFFFFFFF से घटाया जाता है। परिणाम क्षेत्र का आकार है। कम बिट में इकाई को ध्यान में नहीं रखा जाता है।

सामान्य लेनदेन एल्गोरिथ्म

मास्टर AD बस में डिवाइस पते को उजागर करता है, CBE बस में निष्पादित होने वाली कमांड, FRAME सिग्नल को 0 और IRDY सिग्नल को 0. पर सेट करता है, मास्टर TRDY और DEVEL सिग्नल सेट करने के लिए लक्ष्य की प्रतीक्षा करता है। इसके अलावा, लक्ष्य AD बस में अनुरोधित डेटा को उजागर करता है। IRDY, TRDY, और DEVSEL तर्क शून्य पर होने पर डेटा वैध माना जाता है।

कार्यान्वयन

FPGA के निष्कर्ष तक पहुँचने के लिए, आपको विशेष घटकों की आवश्यकता होगी: I / O बफर राज्य के साथ काम करने के लिए।

तो, AD बस के लिए, कनेक्शन इस तरह दिखेगा:

signal AD_I: std_logic_vector (AD'range); signal AD_O: std_logic_vector (AD'range); signal AD_T: std_logic; AD_BUF: for iCount in AD'low to AD'high generate begin IOBUF_AD : IOBUF generic map ( DRIVE => 12, IOSTANDARD => "PCI33_3", SLEW => "SLOW") port map ( O => AD_I(iCount), IO => AD(iCount), I => AD_O(iCount), T => AD_T ); end generate;

जहां,

- ओ - बफर आउटपुट।

- IO - बफर के इनपुट / आउटपुट, सीधे FPGA पिन से जुड़े।

- मैं - बफर आउटपुट।

- टी - इनपुट नियंत्रण, यूनिट स्तर - इनपुट, शून्य स्तर - आउटपुट।

शेष संकेतों के लिए, इसी तरह, मैं इसे उद्धृत नहीं करूंगा ताकि लेख को अव्यवस्थित न किया जा सके।

जैसा कि मैंने ऊपर लिखा था, एक लेन-देन की शुरुआत में, जब कोई पता AD बस पर सेट होता है, तो FRAME सिग्नल हमेशा शून्य होता है। नीचे वह कोड है जो AdrPhASE सिग्नल उत्पन्न करता है, जिसके दौरान आपको बाद के काम के लिए एड्रेस बस और कमांड बस पर क्लिक करना होगा। वास्तव में, AdrPhASE सिग्नल FRAME सिग्नल के गिरते छोर से ज्यादा कुछ नहीं है, जो विशिष्ट रूप से लेनदेन की शुरुआत की पहचान करता है।

signal AdrPhASE: std_logic; signal FRAME_D: std_logic; signal Addres: std_logic_vector(AD_I'range); signal Command: std_logic_vector(CBE'range); signal bCfgTr: boolean; process (clk_i, RST_I) begin if (RST_I = '0') then FRAME_D <= '1' after cTCQ; elsif (rising_edge(clk_I)) then FRAME_D <= FRAME_I after cTCQ; end if; end process; AdrPhASE <= not FRAME_I and FRAME_D; process (clk_I, RST_I) begin if (RST_I = '0') then Address <= (others => '0') after cTCQ; Command <= (others => '0') after cTCQ; bCfgTr <= false after cTCQ; elsif (rising_edge(clk_I)) then if (AdrPhASE = '1') then Address <= AD_I after cTCQ; Command <= CBE_I after cTCQ; bCfgTr <= (IDSEL_I = '1') after cTCQ; end if; end if; end process;

इसके अलावा, मशीन का उपयोग करके पूरे डिवाइस के संचालन का वर्णन किया जा सकता है।

मशीन कोड type TSM_PCI_T is (sIDLE, sDECODE, sCFG_READ, sCFG_WRITE, sIO_READ, sIO_WRITE, sMEM_READ, sMEM_WRITE); signal smPCI_T: TSM_PCI_T; process(clk_I, RST_I) begin if (RST_I = '0') then smPCI_T <= sIDLE after cTCQ; elsif (rising_edge(clk_I)) then case (smPCI_T) is when sIDLE => if (AdrPhASE = '1') then smPCI_T <= sDECODE after cTCQ; end if; when sDECODE => if (bCfgTr and Address(10 downto 8) = b"000" and Command(3 downto 1) = b"101") then if (Command(0) = '0') then smPCI_T <= sCFG_READ after cTCQ; else smPCI_T <= sCFG_WRITE after cTCQ; end if; elsif (Command(3 downto 1)= b"001") and (Addres(31 downto 8) = BAR0(31 downto 8))then if (Command(0) = '0') then smPCI_T <= sIO_READ after cTCQ; else smPCI_T <= sIO_WRITE after cTCQ; end if; elsif (Command(3 downto 1) = b"011") and (Addres(31 downto 16) = BAR1(31 downto 16)) then if (Command(0) = '0') then smPCI_T <= sMEM_READ after cTCQ; else smPCI_T <= sMEM_WRITE after cTCQ; end if; else smPCI_T <= sIDLE after cTCQ; end if; when sCFG_READ => if (IRDY_I = '0') then smPCI_T <= sIDLE after cTCQ; end if; when sCFG_WRITE => if (IRDY_I = '0') then smPCI_T <= sIDLE after cTCQ; end if; when sIO_WRITE => if (IRDY_I = '0') then smPCI_T <= sIDLE after cTCQ; end if; when sIO_READ => if (IRDY_I = '0') then smPCI_T <= sIDLE after cTCQ; end if; when sMEM_READ => if (IRDY_I = '0') then smPCI_T <= sIDLE after cTCQ; end if; when sMEM_WRITE => if (IRDY_I = '0') then smPCI_T <= sIDLE after cTCQ; end if; when others => smPCI_T <= sIDLE after cTCQ; end case; end if; end process;

उपरोक्त समझने के लिए, मैं सीबीई बस के माध्यम से प्रेषित संभावित आदेश देगा।

- 0010 आई / ओ पढ़ें

- 0011 I / O लिखें

- 0110 मेमोरी रीड

- 0111 मेमोरी लिखें

- 1010 कॉन्फ़िगरेशन पढ़ें

- 1011 विन्यास लिखें

प्रत्येक टीम की मशीन की अपनी स्थिति है। मेमोरी और I / O पोर्ट तक पहुंचने वाले लेन-देन के लिए CBE बस और AD बस की वर्तमान स्थिति पर निर्भर करता है। प्रारंभिक अवस्था से बाहर निकलें, मास्टर से IRDY संकेत प्राप्त होने पर किया जाता है।

कॉन्फ़िगरेशन पढ़ें

जैसा कि ऊपर वर्णित है, टाइप 0 के लेनदेन का उपयोग डिवाइस द्वारा प्रसंस्करण के लिए किया जाता है। चूंकि डिवाइस एकल-फ़ंक्शन है, फ़ंक्शन संख्या 000 है, जिसे नियंत्रण मशीन में चेक किया जाएगा। उपरोक्त संख्या के अनुसार, रजिस्टर संख्या (बिट्स AD.0 की बिट्स) पर निर्भर करता है, AD बस में वांछित रजिस्टर जारी किया जाता है।

कॉन्फ़िगरेशन कोड पढ़ें signal CfgRData: std_logic_vector(31 downto 0):=x"00000000"; signal CommandReg: std_logic_vector(15 downto 0) := x"0000"; signal StatusReg: std_logic_vector(15 downto 0) := x"0200"; signal LatencyTimer: std_logic_vector(7 downto 0) := x"00"; signal CacheLineSize: std_logic_vector(7 downto 0) := x"00"; signal BAR0: std_logic_vector(31 downto 0) := x"00000001"; signal BAR1: std_logic_vector(31 downto 0) := x"00000000"; signal InterruptLine: std_logic_vector(7 downto 0); process (clk_I) begin if (rising_edge(clk_I)) then case (Address(7 downto 0)) is when x"00" => CfgRData <= x"00017788" ;

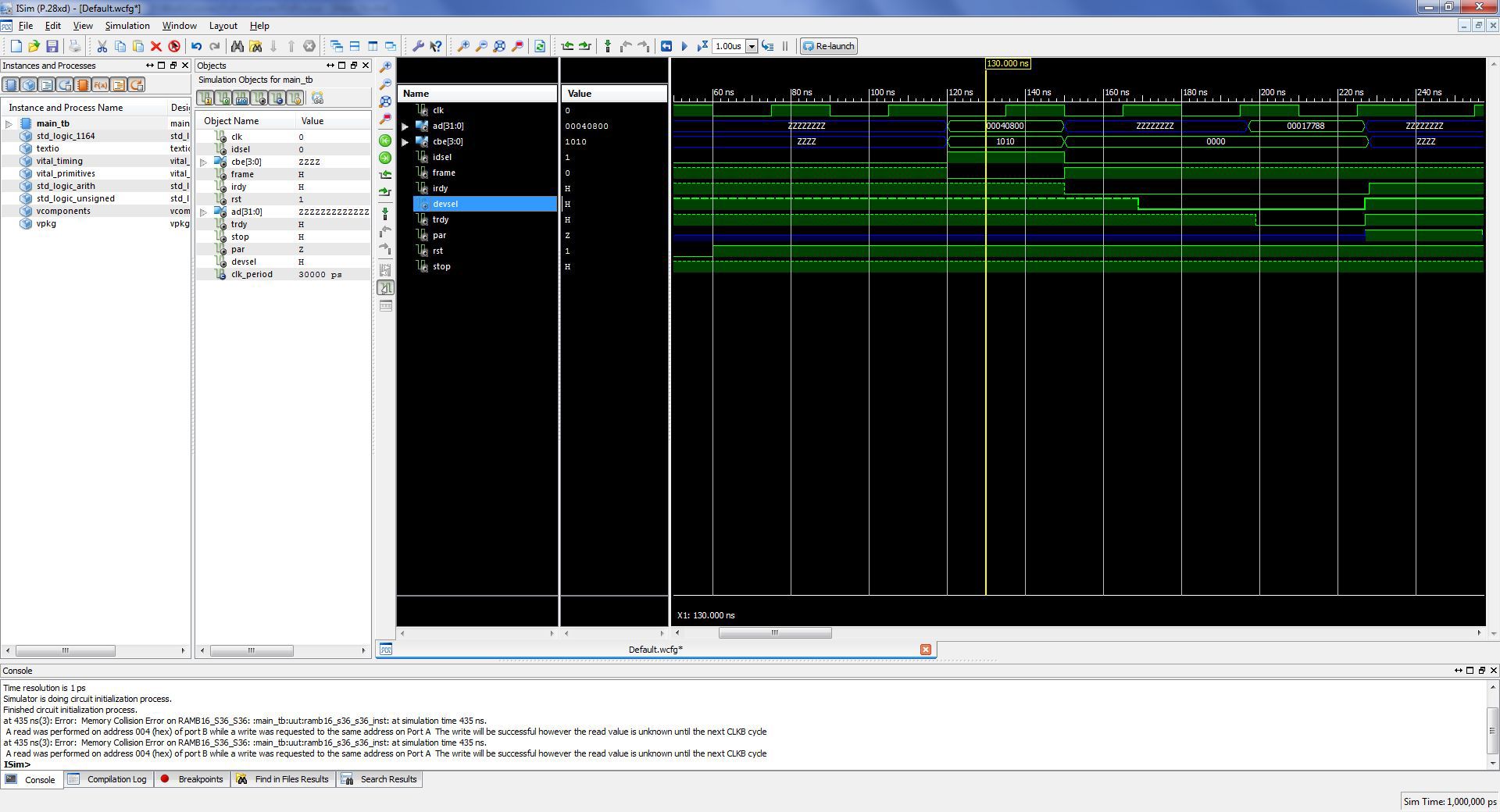

यह कैसे सिम्युलेटर में विन्यास पढ़ने की तरह लग रहा है:

कॉन्फ़िगरेशन रिकॉर्ड

AD बस में, मास्टर रिकॉर्डिंग के लिए रजिस्टर पता सेट करता है, और अगले घड़ी चक्र में, लिखा जाने वाला डेटा सेट किया जाता है। BAR0 में, बिट्स 7..0 केवल-पढ़ने के लिए हैं, BAR1 में, बिट्स 15..0 केवल-पढ़ने के लिए हैं। इसलिए, मैं / ओ 256 पते, स्मृति पते 4,294,967,296।

कॉन्फ़िगरेशन रिकॉर्ड कोड process(clk_I, RST_I) begin if(RST_I = '0')then CommandReg <= x"0000" after cTCQ; StatusReg <= x"0200" after cTCQ; LatencyTimer <= x"00" after cTCQ; CacheLineSize <= x"00" after cTCQ; BAR0 <= x"00000001" after cTCQ; BAR1 <= x"00000000" after cTCQ; elsif(rising_edge(clk_I)) then if (smPCI_T = sCFG_WRITE) then case(Address(7 downto 0)) is when x"04" => if (CBE_I(1) = '0') then CommandReg(15 downto 8) <= AD_I(15 downto 8) after cTCQ; end if; if (CBE_I(0) = '0') then CommandReg(7 downto 0) <= AD_I(7 downto 0) after cTCQ; end if; when x"0C" => if (CBE_I(1) = '0') then LatencyTimer <= AD_I(15 downto 8) after cTCQ; end if; if (CBE_I(0) = '0') then CacheLineSize <= AD_I(7 downto 0) after cTCQ; end if; when x"10" => if (CBE_I(3) = '0') then BAR0(31 downto 24) <= AD_I(31 downto 24) after cTCQ; end if; if (CBE_I(2) = '0') then BAR0(23 downto 16) <= AD_I(23 downto 16) after cTCQ; end if; if (CBE_I(1) = '0') then BAR0(15 downto 8) <= AD_I(15 downto 8) after cTCQ; end if; when x"14" => if (CBE_I(3) = '0') then BAR1(31 downto 24) <= AD_I(31 downto 24) after cTCQ; end if; if (CBE_I(2) = '0') then BAR1(23 downto 16) <= AD_I(23 downto 16) after cTCQ; end if; when x"3C" => if (CBE_I(0) = '0') then InterruptLine <= AD_I(7 downto 0) after cTCQ; end if; when others => null; end case; end if; end if; end process;

पोर्ट करने के लिए लिखें

AD बस में, मास्टर रिकॉर्डिंग के लिए रजिस्टर नंबर सेट करता है, अगली घड़ी में लिखा जाने वाला डेटा सेट किया जाता है।

हम केवल एक रजिस्टर लिखने के लिए एक उदाहरण देते हैं, बाकी उसी तरह से लिखे जाते हैं।

signal IOReg0: std_logic_vector (31 downto 0); process(clk_I, RST_I) begin if(RST_I = '0') then IOReg0 <= x"00000000" after cTCQ; elsif (rising_edge(clk_I)) then if (smPCI_T = sIO_WRITE and Address(7 downto 0) = x"00") then if (CBE_I(0) = '0') then IOReg0( 7 downto 0) <= AD_I( 7 downto 0) after cTCQ; end if; if (CBE_I(1) = '0') then IOReg0(15 downto 8) <= AD_I(15 downto 8) after cTCQ; end if; if (CBE_I(2) = '0') then IOReg0(23 downto 16) <= AD_I(23 downto 16) after cTCQ; end if; if (CBE_I(3) = '0') then IOReg0(31 downto 24) <= AD_I(31 downto 24) after cTCQ; end if; end if; end if; end process;

पोर्ट पढ़ें

AD बस में, मास्टर पढ़ने के लिए रजिस्टर नंबर सेट करता है। डिवाइस तब AD बस में अनुरोधित डेटा जारी करता है।

पोर्ट रीड कोड signal IORDate: std_logic_vector (31 downto 0); process (clk_I, RST_I) begin if (RST_I = '0') then IORDate <= x"00000000"; elsif (rising_edge(clk_I)) then case (Address(7 downto 0)) is when x"00" => IORDate <= IOReg0 after cTCQ; when x"04" => IORDate <= IOReg1 after cTCQ; when x"08" => IORDate <= IOReg2 after cTCQ; when x"0C" => IORDate <= IOReg3 after cTCQ; when x"10" => IORDate <= IOReg4 after cTCQ; when x"14" => IORDate <= IOReg5 after cTCQ; when x"18" => IORDate <= IOReg6 after cTCQ; when x"1C" => IORDate <= IOReg7 after cTCQ; when x"20" => IORDate <= IOReg8 after cTCQ; when x"24" => IORDate <= IOReg9 after cTCQ; when others => IORDate <= (others => '0'); end case; end if; end process;

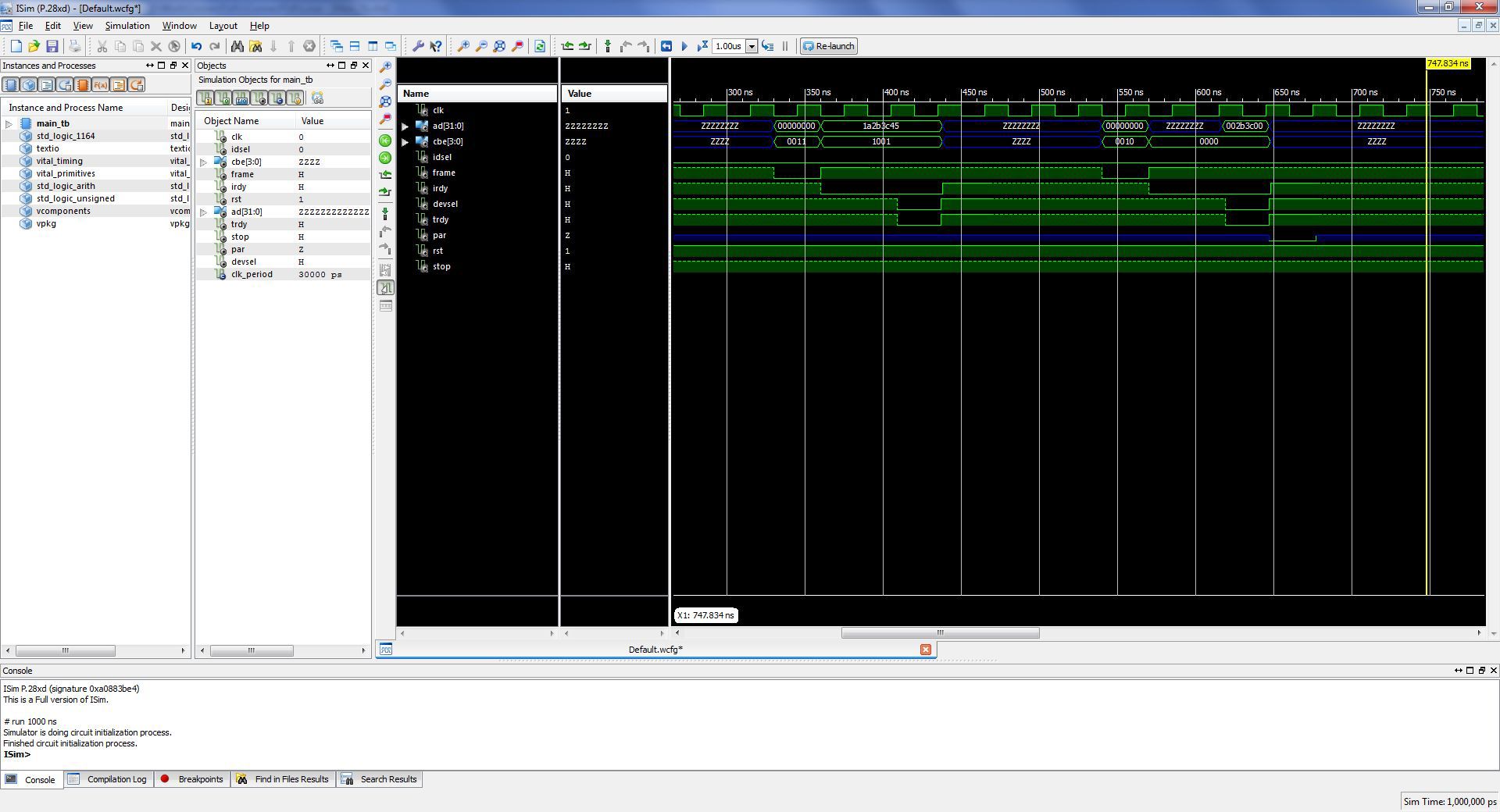

इस तरह इनपुट / आउटपुट पोर्ट लिखना और पढ़ना कैसा दिखता है:

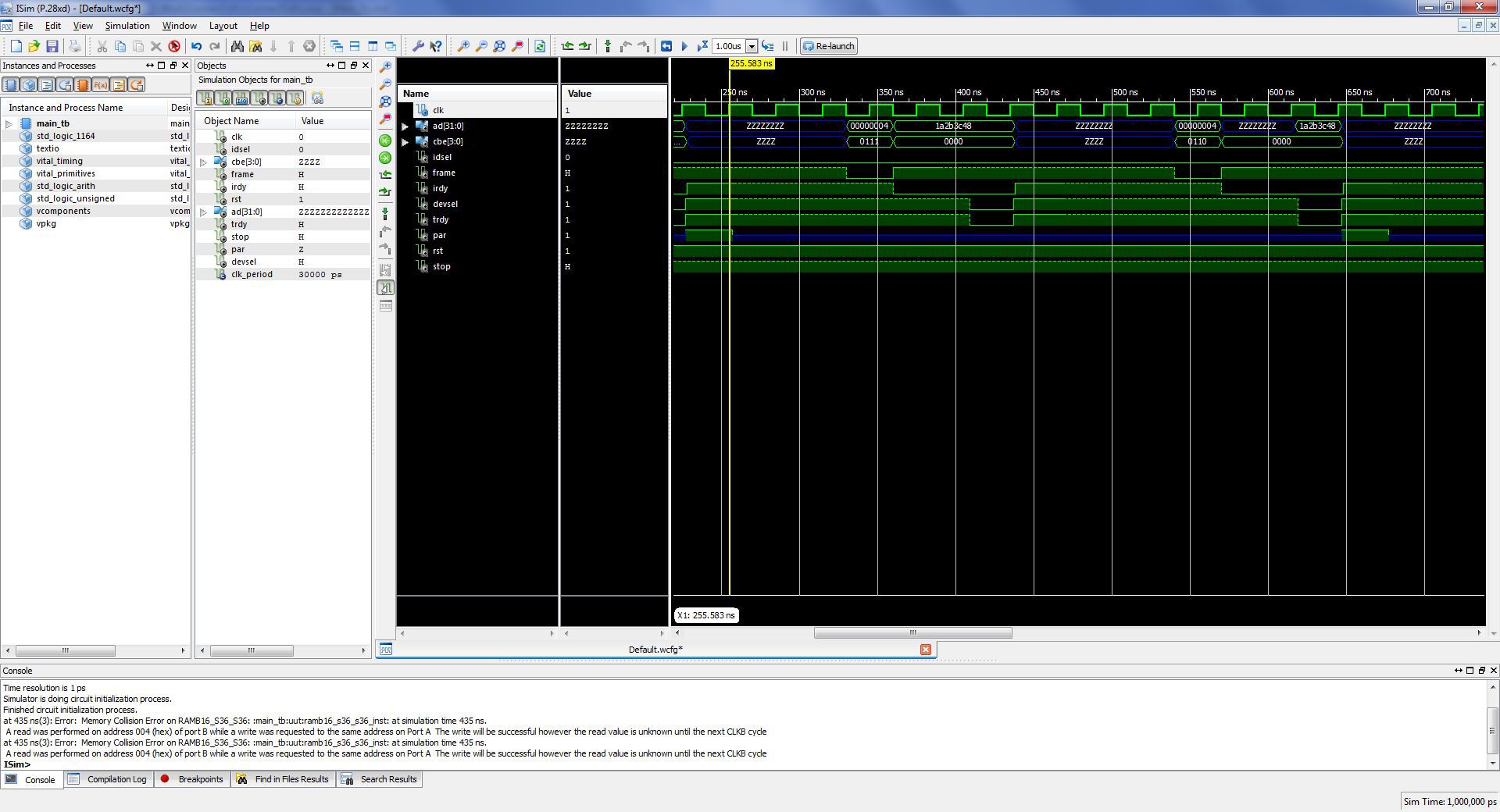

लेखन और स्मृति पढ़ना

AD बस में, मास्टर पता निर्धारित करता है कि किस डेटा को लिखा जाना चाहिए, और अगली घड़ी में डेटा स्वयं। जब एडी बस पर पढ़ते हैं, तो मास्टर पढ़ने के लिए पता सेट करता है, फिर डेटा खुद एडी बस को लक्षित करता है।

पोर्ट ए में रैम के लिए डेटा लिखा गया है, पोर्ट बी से पढ़ा गया।

मेमोरी एक्सेस कोड signal RamWrEn: std_logic; signal RamOutputDate: std_logic_vector (31 downto 0); signal RamInputDate: std_logic_vector (31 downto 0); signal RamRst: std_logic := '0'; RAMB16_S36_S36_inst : RAMB16_S36_S36 port map ( DOA => open,

इस तरह से मेमोरी लिखना और पढ़ना सिम्युलेटर में दिखता है:

AD बस पर डेटा निम्नानुसार आउटपुट है। मशीन की स्थिति के आधार पर, संबंधित रजिस्टर आउटपुट बफर से जुड़ा हुआ है।

process (clk_I, RST_I) begin if (RST_I = '0') then AD_O <= (others => '0') after cTCQ; elsif (rising_edge(clk_I)) then if (smPCI_T = sCFG_READ) then AD_O <= CfgRData after cTCQ; elsif (smPCI_T = sIO_READ) then AD_O <= IORDate after cTCQ; elsif (smPCI_T = sMEM_READ) then AD_O <= RamOutputDate after cTCQ; end if; end if; end process;

AD बस में डेटा जारी करने के लिए सक्षम संकेत निम्नानुसार उत्पन्न होता है:

process (clk_I, RST_I) begin if (RST_I = '0') then AD_T <= '1' after cTCQ; elsif (rising_edge(clk_I)) then AD_T <= not b2l(smPCI_T = sCFG_READ or smPCI_T = sIO_READ or smPCI_T = sMEM_READ) after cTCQ; end if; end process;

अलग से, मैं DEVSEL संकेत पीढ़ी का उपयोग करके STS घटक के बारे में जोड़ना चाहूंगा

DEVSEL_STS : entity WORK.componentIO(Behavioral) port map (iD => DEVSEL_O, oT => DEVSEL_T, clk => clk_I, rst => RST_I)

चूंकि नियंत्रण संकेतों के सक्रिय स्तर शून्य के बराबर हैं, फिर जेड - राज्य पर स्विच करने और लाइन जारी करने के लिए, आपको पहले तार्किक इकाई का स्तर जारी करना होगा और उसके बाद ही इसे जेड राज्य में स्थानांतरित करना होगा।

निष्कर्ष

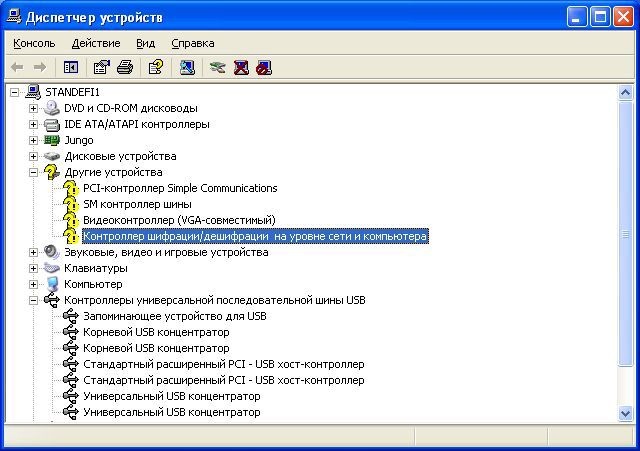

निष्कर्ष में, मैं यह कहना चाहता हूं कि पीसीआई बस में लेनदेन का निष्पादन उतना मुश्किल नहीं है जितना लगता है। विकसित फर्मवेयर को FPGA पर अपलोड किया गया था। FPGA के साथ बोर्ड को PCI स्लॉट में डाला गया है और कंप्यूटर चालू हो गया है। सिस्टम ने बोर्ड पाया और इसके लिए एक ड्राइवर का अनुरोध किया।

यह काम करता है! :)

ड्राइव .

google.com/file/d/0B-i4aT8Q0ZNxc1VkV3J2b0dTRlU/view?usp=sharing प्रोजेक्ट स्वयं। ओपन xilinx ise 14.2।