अमूर्त

इस लेख में पीसीआई एक्सप्रेस बस के माध्यम से कई एफपीजीए की एक साथ भागीदारी के साथ डेटा के हस्तांतरण पर चर्चा की गई है। कंप्यूटर सिस्टम में कई (हमारे मामले में 8) टर्मिनल डिवाइस (PCIe एंडपॉइंट) FPGAs के साथ, दो प्रकार के कई डेटा ट्रांसफर लेनदेन एक साथ शुरू होते हैं: A) RAM और FPGA (पढ़ें / लिखें) और B) के बीच डीएमए डायरेक्ट दो FPGAs (रिकॉर्डिंग) के बीच डेटा स्थानांतरण। मेमोरी एक्सेस करते समय PCI एक्सप्रेस x4 जनरल 2.0 कनेक्शन का उपयोग करते हुए, 1451 एमबी / एस की एक लेखन गति प्राप्त की गई (अधिकतम का 90%)। FPGAs के बीच डेटा लिखने की गति 1603 एमबी / एस (अधिकतम का 99%) है जिसकी पैकेट लंबाई 128 बाइट्स और 1740 एमबी / एस (अधिकतम का 99%) 256 बाइट्स की एक पैकेट लंबाई के साथ है। FPGAs के बीच डेटा हस्तांतरण की विलंबता मध्यवर्ती स्विच की संख्या पर निर्भर करती है, और एक स्विच के लिए 0.7 μs और तीन के लिए 1 μs के बराबर थी। यह भी दिखाया गया है कि एक सामान्य चैनल के माध्यम से एक साथ प्रसारण के साथ, व्यक्तिगत प्रसारण की गति तब तक कम नहीं होती है जब तक कि कुल संचरण की गति सामान्य चैनल की बैंडविड्थ से अधिक न हो जाए; तब चैनल का उपयोग 100% पर किया जाता है, और इसकी बैंडविड्थ को उपकरणों के बीच समान रूप से विभाजित किया जाता है।

परिचय

PCI एक्सप्रेस उच्च प्रदर्शन कम्प्यूटिंग (HPC) कार्यों के लिए CPU, सिस्टम मेमोरी और हार्डवेयर एक्सेलेरेटर (GPU, FPGAs) के बीच डेटा स्थानांतरित करने के लिए वास्तविक मानक बन गया है। सबसे पहले, पीसीआई एक्सप्रेस बस में एक छोटी विलंबता होती है, और दूसरी बात, इसमें उच्च डेटा ट्रांसफर दर (पीसीआई एक्सप्रेस x8 जनरल 3.0 कनेक्शन के साथ लगभग 7 जीबी / एस) है। अंत में, PCIe बस में अच्छी मापनीयता है: आमतौर पर मदरबोर्ड पर PCI Express बस कनेक्टर्स की कोई कमी नहीं होती है, जिससे आप GPU या FPGA के कई त्वरक बोर्डों को जोड़ सकते हैं। इसके अलावा, तकनीकी समाधान हाल ही में सामने आए हैं जो पीसीआई एक्सप्रेस बस को केबल कनेक्शन के माध्यम से और कंप्यूटर केस (1) के बाहर अतिरिक्त परिधीय उपकरणों को जोड़ने की अनुमति देते हैं।

आधुनिक एचपीसी प्रणालियों में, एक एकल हार्डवेयर त्वरक होना पर्याप्त नहीं है। यह पहले से ही गणना नोड के स्थानीय PCI एक्सप्रेस बस पर दो GPU बोर्ड देखने के लिए प्रथागत हो गया है। जीपीयू के बीच सीधे डेटा एक्सचेंज सुनिश्चित करने के लिए, GPUDirect तकनीक विकसित की गई (2)। इस तकनीक का उपयोग करके, एक बफर के रूप में रैम का उपयोग किए बिना सीधे PCI एक्सप्रेस बस के माध्यम से GPU उपकरणों के बीच डेटा के आदान-प्रदान को व्यवस्थित करना संभव है, जो डेटा ट्रांसफर के ओवरहेड को काफी कम कर सकता है।

पीसीआई एक्सप्रेस बस में कई एक्सेलेरेटर के अन्य उदाहरणों में वे सिस्टम शामिल हैं जो GPU और FPGA दोनों को चलाते हैं। पहले उदाहरण में, ऑस्ट्रेलिया के शोधकर्ताओं की एक टीम ने एक इंटेल मदरबोर्ड, एक कोर आई 7 प्रोसेसर, एक एनवीडिया टेस्ला सी 2070 जीपीयू बोर्ड और एक एलटर डीए -570 बोर्ड के साथ एक स्थापित स्ट्रैटिक्स-IV एफपीजीए चिप (3) के साथ एक व्यक्तिगत कंप्यूटर को इकट्ठा किया। उन्होंने इसका नाम प्राचीन यूनान चिमेरा के पौराणिक राक्षस के सम्मान में "चिमेरा" रखा, जिसके एक शरीर पर 3 सिर (बकरी, सांप, शेर) हैं। उन्होंने कई समस्याओं को सफलतापूर्वक हल किया है (मोंटे कार्लो पद्धति का उपयोग करके एकीकरण, एक 2D सरणी में टेम्पलेट की खोज) और निरंतर गुरुत्वाकर्षण तरंगों के विश्लेषण के लिए इस प्रणाली के उपयोग पर काम कर रहे हैं। उनके प्रोजेक्ट की मुख्य विशेषता यह थी कि GPU और FPGA एक ही कार्य पर एक साथ काम करते थे, और डेटा को GPU से FPGA में PCI एक्सप्रेस बस के माध्यम से स्थानांतरित किया जाता था। हालांकि, यह ध्यान दिया जाना चाहिए कि यह एक्सचेंज केंद्रीय प्रोसेसर के नियंत्रण में था और रैम में एक बफर के माध्यम से।

ब्रसेल्स की एक अन्य टीम ने एनवीडिया टेस्ला C2050 जीपीयू और पिको कम्प्यूटिंग EX-500 FPGAs (4) के साथ एक हाइब्रिड कंप्यूटर को इकट्ठा किया। अंतिम बोर्ड में 1 से 6 Xilinx Virtex6 FPGAs शामिल हो सकते हैं, प्रत्येक का अपना PCI एक्सप्रेस होस्ट इंटरफ़ेस है। परियोजना का विवरण अभी तक स्पष्ट नहीं है, संदेश केवल एक छाप के रूप में उपलब्ध है।

अंत में, माइक्रोसॉफ्ट के डेवलपर्स की एक टीम ने पीसीआई एक्सप्रेस बस (5) के माध्यम से सीधे GPU और FPGA के बीच डेटा के हस्तांतरण की जांच की। उनके सिस्टम में, 1 वीरटेक्स 6 चिप के साथ एनवीडिया जियफोर्स जीटीएक्स 580 जीपीयू और एक्सलिनक्स एमएल605 एफपीजीएएस लगाए गए थे। डेवलपर्स ने CUDA API, GPUDirect तकनीक और Linux FPGA डिवाइस ड्राइवर का उपयोग करके GPU और FPGA के बीच सीधे डेटा ट्रांसफर शुरू करने का एक तरीका खोज लिया है। इसने हमें गति को बढ़ाने और एक मध्यवर्ती बफर के रूप में रैम का उपयोग करने वाले दृष्टिकोण की तुलना में डेटा हस्तांतरण की विलंबता को कम करने की अनुमति दी। इस मामले में, GPU मास्टर था, और FPGA गुलाम था।

PCI एक्सप्रेस बस का उपयोग FPGAs के बीच सीधे डेटा स्थानांतरित करने के लिए भी किया जा सकता है। Xilinx ने इस क्षमता (6) का प्रदर्शन किया है। Xilinx इंजीनियरों ने दो FPGAs को पीसीआई एक्सप्रेस बस के माध्यम से सीधे स्विच का उपयोग किए बिना और एक केंद्रीय प्रोसेसर वाले कंप्यूटर के बिना कनेक्ट किया। एक चिप ने अपने पीसीआई एक्सप्रेस इंटरफ़ेस को स्वतंत्र रूप से कॉन्फ़िगर किया, दूसरे के साथ एक कनेक्शन स्थापित किया और इसे कॉन्फ़िगर किया। जिसके बाद दो FPGA क्रिस्टल के बीच दोनों दिशाओं में डेटा स्थानांतरित करना संभव था। यह दृष्टिकोण PCI एक्सप्रेस बस के माध्यम से FPGAs के बीच डेटा स्थानांतरित करने की मूलभूत संभावना को प्रदर्शित करता है, लेकिन इसका उपयोग तब नहीं किया जा सकता है जब कई FPGAs पीसीआई एक्सप्रेस स्विच के माध्यम से एक केंद्रीय प्रोसेसर के साथ कंप्यूटर से जुड़े हों।

यह लेख एक पीसीआई एक्सप्रेस बस में कई FPGAs युक्त प्रणाली में डेटा हस्तांतरण का वर्णन करता है। सिस्टम मेमोरी और कई FPGAs के बीच एक साथ डेटा ट्रांसफर के मुद्दों पर चर्चा की जाती है, साथ ही साथ कई FPGAs के बीच डेटा का एक साथ प्रसारण सीधे एक दूसरे के साथ होता है। हमारी जानकारी के लिए, यह संदेश कंप्यूटर के पीसीआई एक्सप्रेस बस के माध्यम से FPGAs के बीच डेटा के हस्तांतरण का वर्णन करने के मामले में पहला है।

सिस्टम विवरण

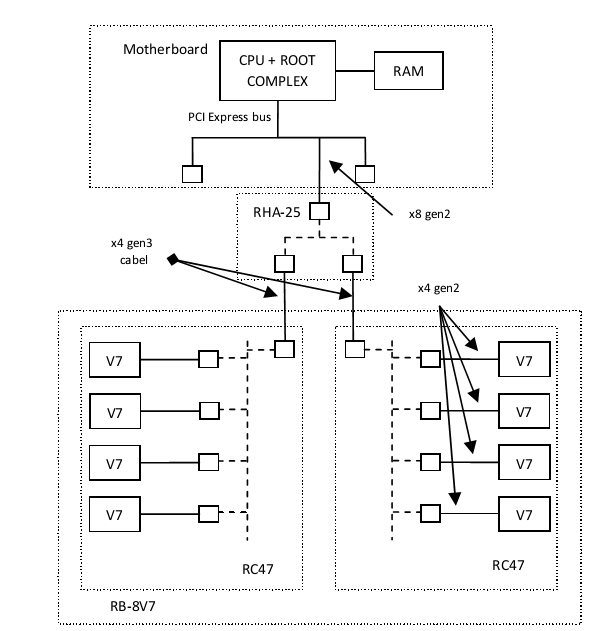

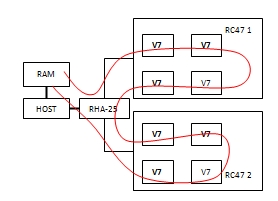

प्रयोग निम्नलिखित प्रणाली में किए गए थे। इंटेल कोर i7 प्रोसेसर के साथ मदरबोर्ड में, रोस्टा (1) द्वारा निर्मित एक आरएचए -25 एडाप्टर पीसीआई एक्सप्रेस 2.0 x8 कनेक्टर में स्थापित किया गया था, जो केबल कनेक्शन के माध्यम से पीसीआई एक्सप्रेस बस का विस्तार करता है। एक पीसीआई एक्सप्रेस स्विच (पीएलएक्स टेक्नोलॉजी) आरएचए -25 एडेप्टर पर स्थापित किया गया है, जिसके तीन पोर्ट बाहरी कनेक्शन के लिए उपयोग किए जाते हैं: एक एक्स 8 जनरल 3.0 ब्लेड अपस्ट्रीम पोर्ट और दो एक्स 4 जनरल 3.0 केबल डाउनस्ट्रीम पोर्ट। RB-8V7 कंप्यूटिंग यूनिट (1) 2 केबल कनेक्शन PCI Express x4 Gen 3.0 के माध्यम से इस प्रणाली से जुड़ा था। RB-8V7 इकाई में एक सममित वास्तुकला है और रचनात्मक रूप से दो RC-47 बोर्ड हैं। प्रत्येक RC-47 कार्ड में एक केबल अपस्ट्रीम पोर्ट और चार डाउनस्ट्रीम पोर्ट के साथ PLX PCI एक्सप्रेस स्विच होता है, जिनमें से प्रत्येक अपने Xilinx Virtex-7 FPGA (XC7V585T) से जुड़ा होता है। इस प्रकार, हमारे सिस्टम में, 8 वीरटेक्स -7 (V7) FPGAs एक RHA-25 अडैप्टर का उपयोग करके PCI एक्सप्रेस बस के माध्यम से मेजबान से जुड़े थे। पीसीएक्स एक्सप्रेस एक्स 4 जनरल 2.0 के माध्यम से पीएलएक्स स्विच से जुड़े सभी एफपीजीए।

अंजीर। 1 हार्डवेयर। RB-8V7 यूनिट केबल PCIe कनेक्शन और होस्ट कंप्यूटर के लिए RHA-25 एडाप्टर के माध्यम से जुड़ा हुआ है

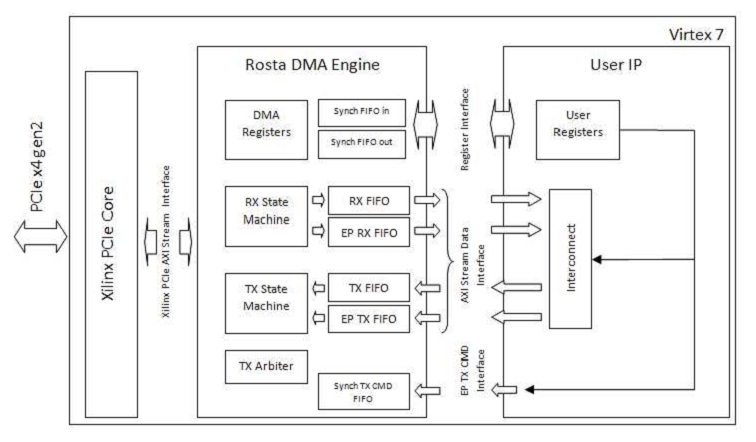

FPGA के अंदर, निम्नलिखित योजना लागू की गई थी (चित्र 2)। परियोजना Xilinx के PCI एक्सप्रेस IP कोर (7) का उपयोग करती है। रोस्टा डीएमए इंजन ब्लॉक पीसीआई एक्सप्रेस बस पर डिवाइस की कार्यक्षमता निर्धारित करता है। FPGA एक मास्टर या दास के रूप में कार्य कर सकता है। एक दास डिवाइस के रूप में, FPGA केंद्रीय रजिस्टरों को अपने रजिस्टरों तक पढ़ने और लिखने के लिए पहुंच प्रदान करता है, और EPP -RX_FIFO कतार में डेटा प्राप्त करते समय बस में अन्य उपकरणों (उदाहरण के लिए, अन्य FPGAs से) से बड़े डेटा पैकेट प्राप्त कर सकता है। एक मास्टर डिवाइस के रूप में, FPGAs कंप्यूटर की रैम को DMA (रीड / राइट) मोड में एक्सेस कर सकते हैं। इस स्थिति में, मेमोरी में लिखते समय डेटा TX_FIFO से पढ़ा जाएगा, और मेमोरी से पढ़ते समय, यह RX_FIFO को लिखा जाएगा। डिवाइस बस पर एक मनमाने पते पर लिखने के लेनदेन को उत्पन्न करने में सक्षम है (उदाहरण के लिए, अन्य FPGAs को डेटा स्थानांतरित करने के लिए), इस मामले में, ट्रांसमिशन के लिए डेटा EP_TX_FIFO कतार से पढ़ा जाता है। आने वाले पैकेट प्राप्त करने के लिए RX_STATE_MACHINE सबमशीन गन जिम्मेदार है; TX_STATE_MACHINE सबमशीन पैकेट के प्रसारण के लिए जिम्मेदार है। पैकेट के रिसेप्शन और ट्रांसमिशन एक साथ जा सकते हैं। TX_ARBITER ब्लॉक निर्धारित करता है कि ट्रांसमिशन के लिए कौन से पैकेट को निम्नानुसार प्रसारित करना है: केंद्रीय प्रोसेसर द्वारा रजिस्टरों को पढ़ने के दौरान प्रतिक्रियाओं की पीढ़ी को पूर्ण प्राथमिकता दी जाती है, शेष पैकेट (एक यादृच्छिक पते के लिए अनुरोध पढ़ने / लिखने या एक मनमाने पते पर लिखने के अनुरोध) को समान प्राथमिकता (राउंड-रॉबिन) के साथ नियोजित किया जाता है। ।

अंजीर। FPGA परियोजना के 2 ब्लॉक आरेख

केंद्रीय प्रोसेसर (DMA_REGISTERS ब्लॉक को लिखकर) FPGA और RAM के बीच DMA डेटा ट्रांसफर करने में लगा हुआ है, और दूसरे FPGA में एक मनमाने पते पर डेटा लिखने की प्रक्रिया को नियंत्रित करने के लिए एक आंतरिक EP TX CMD हार्डवेयर इंटरफ़ेस है। उपयोगकर्ता आईपी ब्लॉक में उपयोगकर्ता रजिस्टरों तक पहुंच के लिए, एक रजिस्टर इंटरफ़ेस है, और पीसीआई एक्सप्रेस अंतरिक्ष और उपयोगकर्ता सर्किट के बीच डेटा हस्तांतरण को ब्लॉक करने के लिए, RX_FIFO, TX_FIFO, EP_RX_FIFO, EP_TX_FIFO कतारों से जुड़े चार AXI स्ट्रीम इंटरफेस हैं। अंत में, PCI एक्सप्रेस Xilinx कोर की ओर, रोस्टा डीएमए इंजन Xilinx PCIe AXI स्ट्रीम इंटरफ़ेस का समर्थन करता है, जिसकी चौड़ाई 64 बिट्स है। इकाई दो घड़ी आवृत्तियों पर संचालित होती है: Xilinx कोर PCIe आवृत्ति (250 MHz) पर सर्किट के बाईं ओर, और एक मनमाना उपयोगकर्ता आवृत्ति पर सर्किट के दाईं ओर। FIFO कतारों के माध्यम से फ्रीक्वेंसी डिकंपलिंग होती है। लेकिन नीचे वर्णित सभी प्रयोगों में, उपयोगकर्ता आवृत्ति उस आवृत्ति के बराबर थी जिस पर PCIe कोर (250 मेगाहर्ट्ज) काम करता था।

उपयोगकर्ता IP ब्लॉक एप्लिकेशन स्तर पर डिवाइस के व्यवहार को परिभाषित करता है। इस कार्य में, विभिन्न प्रयोजनों के लिए कई अलग-अलग योजनाओं का उपयोग किया गया था।

सबसे पहले, एक सर्किट का उपयोग FPGA और रैम के बीच डेटा ट्रांसफर की शुद्धता को सत्यापित करने के लिए किया गया था। इस मामले में, इंटरकनेक्ट ब्लॉक में, आउटपुट RX_FIFO केवल TX_FIFO इनपुट पर बंद हुआ। इससे रैम में ठीक वैसा ही डेटा लिखना संभव हो गया जैसा कि इससे पढ़ा गया था। केंद्रीय प्रोसेसर पर कार्यक्रम (बाद में बस मेजबान) ने FPGA को डेटा लिखा, उन्हें पढ़ा, तुलना की और सुनिश्चित किया कि डेटा की तुलना सही ढंग से की गई थी।

दूसरे, दोनों दिशाओं में FPGA और RAM के बीच अधिकतम डेटा अंतरण दर को मापने के लिए एक सर्किट का उपयोग किया गया था। इसके लिए, RX_FIFO से, डेटा लगातार पढ़ा गया था, अर्थात्। कतार हमेशा खाली थी, और इसके अतिप्रवाह के कारण डेटा प्राप्त करने में कोई देरी नहीं हुई थी, और TX_FIFO लगातार डेटा लिख रहा था, अर्थात। कतार में डेटा की कमी के कारण ट्रांसमिशन में कोई देरी नहीं हुई।

तीसरे, FPGAs के बीच सीधे डेटा हस्तांतरण की शुद्धता को सत्यापित करने के लिए एक योजना विकसित की गई थी। इंटरकनेक्ट ब्लॉक में, आउटपुट RX_FIFO और EP_RX_FIFO के इनपुट और TX_FIFO और EP_TX_FIFO के सर्किट को लागू किया गया था। पहले मामले में, आउटपुट RX_FIFO को इनपुट TX_FIFO, और आउटपुट EP_RX_FIFO को EP_TX_FIFO के लिए बंद कर दिया गया था। दूसरे मामले में, आउटपुट RX_FIFO इनपुट EP_TX_FIFO और आउटपुट EP_RX_FIFO इनपुट TX_FIFO के लिए बंद था। यह सर्किट उपयोगकर्ता रजिस्टरों में से एक से थोड़ा नियंत्रित किया गया था। EP TX CMD इंटरफ़ेस को नियंत्रित करने के लिए रजिस्टरों को उपयोगकर्ता रजिस्टरों ब्लॉक में जोड़ा गया है। इस मामले में, होस्ट ने FPGAs के बीच डेटा ट्रांसफर को नियंत्रित किया था, लेकिन सामान्य तौर पर EP TX CMD इंटरफ़ेस को डिज़ाइन किया गया था ताकि FPGA सर्किट स्वयं डेटा ट्रांसफर शुरू कर सके।

चौथा, FPGAs के बीच अधिकतम डेटा अंतरण दर को मापने के लिए, एक विशेष योजना विकसित की गई थी जो डेटा संचारित करते समय लगातार EP_TX_FIFO तक डेटा पहुँचाती है, और डेटा प्राप्त करते समय लगातार EP_RX_FIFO से डेटा पढ़ती है। उसी समय, सर्किट के अंदर एक हार्डवेयर टाइमर लागू किया गया था, जिसके मूल्यों को सहेजा गया था और बाद में मेजबान को भेजा गया था। EP TX CMD इंटरफ़ेस को होस्ट द्वारा उपयोगकर्ता रजिस्टरों के माध्यम से नियंत्रित किया गया था।

अंत में, विलंबता को मापने के लिए, एक सर्किट का उपयोग किया गया जो डेटा को दूसरे FPGA में स्थानांतरित करता है। FPGA डेटा प्राप्त करने ने तुरंत उन्हें उसी डिवाइस पर वापस लिख दिया। ट्रांसमिटिंग FPGA में, एक हार्डवेयर टाइमर उसी समय शुरू किया गया था जब हस्तांतरण शुरू हुआ था, जो उस समय बंद हो गया जब डेटा EP_RX_FIFO कतार में प्रवेश करना शुरू हुआ। इसके अलावा, टाइमर रजिस्टर उपयोगकर्ता रजिस्टरों के माध्यम से मेजबान को पढ़ा जा सकता है।

होस्ट पर लिनक्स स्थापित किया गया था। उपकरण के साथ काम करने के लिए हमारे स्वयं के डिजाइन के ड्राइवरों और पुस्तकालयों का उपयोग किया गया था।

PCI एक्सप्रेस बस बैंडविड्थ

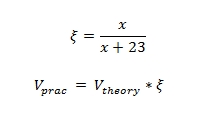

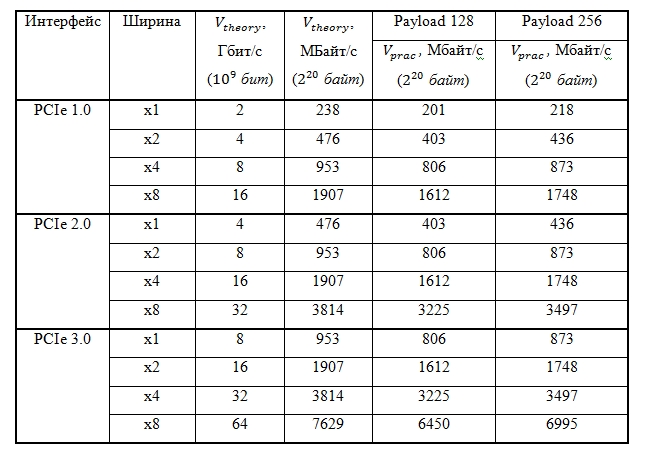

डेटा ट्रांसफर दर को मापने पर प्रयोगों के विवरण के लिए आगे बढ़ने से पहले, इसकी सैद्धांतिक सीमा का पता लगाना आवश्यक है। यह ज्ञात है कि 8B / 10B कोडिंग के उपयोग के कारण, 2.5 गीगाहर्ट्ज (जीन 1) की आवृत्ति पर एकल पीसीआई एक्सप्रेस लाइन के लिए अधिकतम सैद्धांतिक डेटा दर V_theory = 2.0 Gbit / s है। 5 गीगाहर्ट्ज़ की आवृत्ति के साथ जेन 2.0 की दूसरी पीढ़ी के प्रोटोकॉल के लिए, यह गति 2 गुना अधिक है (V_theory = 4.0 Gbit / s)। तीसरी पीढ़ी के लिए सूचना अंतरण दर 2 गुना अधिक है और V_theory = 8.0 Gbit / s प्रति पंक्ति के बराबर है (हालांकि आवृत्ति 8 गीगाहर्ट्ज़ है, तीसरी पीढ़ी का प्रोटोकॉल अलग 128B / 130B वर्ण एन्कोडिंग विधि का उपयोग करता है जो अतिरिक्त भार को कम करता है)।

हालांकि, डेटा इस तथ्य के कारण थोड़ा कम गति पर प्रेषित होता है कि संचरण पैकेट में है जिसमें अतिरिक्त जानकारी (स्टार्ट / स्टॉप बिट्स, हेडर, चेकसम, आदि) शामिल हैं। नतीजतन, जब डेटा के अलावा, लेखन लेनदेन के एक पैकेट को प्रेषित किया जाता है, तो एक ही पैकेट से संबंधित अतिरिक्त 20 बाइट्स प्रेषित होते हैं। इसके अलावा, पीसीआई एक्सप्रेस बस पर पैकेट्स का प्रसारण किया जाता है जिसमें डेटा बिल्कुल नहीं होता है, लेकिन विशुद्ध रूप से सेवा कार्य करता है। इनमें डेटा पैकेट की प्राप्ति की पुष्टि, चेकसम की बेमेल स्थिति में प्रसारण को दोहराने की आवश्यकता, पैकेट जो स्विच में मुक्त अंतरिक्ष बफर के काउंटरों को अद्यतन करते हैं, और अन्य शामिल हैं। डेटा ट्रांसफर दर (यह विशेष रूप से कार्यान्वयन पर निर्भर करता है) पर उनके प्रभाव का सही आकलन करना मुश्किल है, हालांकि, औसतन, उनके योगदान का अनुमान लगभग 1 डेटा पैकेट (8) प्रति 3 अतिरिक्त बाइट्स के रूप में लगाया जा सकता है। कुल में, हम स्वीकार करते हैं कि एक एकल डेटा पैकेट को प्रेषित करने के लिए औसतन 23 अतिरिक्त सेवा बाइट्स प्रेषित की जाती हैं। यह (8) में और अधिक विस्तार से वर्णित है। भविष्य में, जब तक अन्यथा निर्दिष्ट नहीं किया जाता है, पैकेट की लंबाई से हमारा मतलब पैकेट में डेटा की मात्रा से होगा।

पीसीआई एक्सप्रेस बस पर, डेटा को विभिन्न लंबाई के पैकेट में प्रेषित किया जा सकता है। एक पैकेट को प्रेषित करते समय डेटा की अधिकतम मात्रा पैरामीटर MAX_PAYLOAD_SIZE द्वारा निर्धारित की जाती है, जिसका मूल्य दो की शक्ति के बराबर है। प्रत्येक डिवाइस में एक पैरामीटर है MAX_PAYLOAD_SIZE_SUPPORTED, जो अधिकतम पैकेट आकार निर्धारित करता है जिसे इस उपकरण द्वारा प्रेषित किया जा सकता है। कॉन्फ़िगरेशन सॉफ़्टवेयर (BIOS प्रोग्राम) सिस्टम में सभी उपकरणों के लिए MAX_PAYLOAD_SIZE पैरामीटर सेट करता है, जो सिस्टम में उपकरणों द्वारा समर्थित मूल्यों में सबसे छोटा है। एक नियम के रूप में, आधुनिक चिपसेट पैकेट आकार को 128 बाइट तक का समर्थन करते हैं, लेकिन 256 बाइट के साथ सिस्टम हैं। हमारे प्रयोगों में, MAX_PAYLOAD_SIZE_SUPPORTED चिपसेट पैरामीटर 128 बाइट्स था, और यद्यपि RHA-25 और RC-47 बोर्डों पर FPGA और PCI एक्सप्रेस स्विच ने बड़े पैकेट आकार (512 तक) का समर्थन किया, BIOS ने सभी उपकरणों के लिए MAX_PAYLOAD_SIZE पैरामीटर सेट किया। 128 बाइट्स के बराबर प्रणाली।

संचरित पैकेटों का आकार जितना बड़ा होता है, बैंडविड्थ उतनी ही अधिक जानकारी हस्तांतरण की सैद्धांतिक सीमा तक पहुंचता है। यदि सैद्धांतिक सीमा 1 ली जाती है, तो निम्न सूत्र के अनुसार, हम पैकेट के आकार के आधार पर डेटा स्थानांतरण की व्यावहारिक सीमा की गणना कर सकते हैं (तालिका 1 देखें)।

जहां x पैकेट का आकार है।

तालिका 1. पैकेट आकार बनाम सापेक्ष डेटा दर

तालिका में। चित्रा 2 एक पैकेट लंबाई 128 और 256 बाइट्स के लिए अधिकतम सैद्धांतिक और व्यावहारिक डेटा हस्तांतरण दरों की तुलना दिखाता है।

तालिका 2. 128 और 256 बाइट्स लंबाई के पैकेट के लिए पीसीआई एक्सप्रेस बस पर सूचना और डेटा की अधिकतम अंतरण दर

HOST-FPGA ट्रांसमिशन

FPGAs और सिस्टम मेमोरी के बीच डेटा ट्रांसफर करते समय, डायरेक्ट मेमोरी एक्सेस मैकेनिज्म का उपयोग किया जाता है। होस्ट पर एक उपयोगकर्ता एप्लिकेशन रैम में एक बफर तैयार करता है और एक लिखित या रीड सिस्टम कॉल करता है। PCI एक्सप्रेस डिवाइस ड्राइवर उपयोगकर्ता बफ़र पृष्ठों को स्मृति में कैप्चर करता है और तितर बितर / इकट्ठा DMA तंत्र का उपयोग करता है। पृष्ठों के डिस्क्रिप्टर (पता-लंबाई जोड़ी) की सूची को FPGA डिवाइस की आंतरिक मेमोरी में लिखा जाता है, और फिर FPGA को इस सूची के पते से एक्सेस किया जाता है। डेटा ट्रांसफर पूरा होने के बाद, FPGA एक व्यवधान उत्पन्न करता है, जो सिस्टम कॉल को पूरा करता है। जब उपयोगकर्ता एप्लिकेशन FPGA को डेटा लिखने का इरादा रखता है, तो डिवाइस रीड ट्रांजेक्शन के साथ RAM से संपर्क करता है, और FPGA से पढ़ते समय, डिवाइस राइट ट्रांजेक्शन जेनरेट करता है। इसके बाद, यह "रिकॉर्ड" और "पढ़ा" शब्द FPGAs को संदर्भित करता है, अर्थात्। लिखने की गति FPGA द्वारा शुरू की गई रिकॉर्डिंग प्रक्रिया की गति को संदर्भित करती है।

पीसीआई एक्सप्रेस बस में उत्पन्न लेन-देन हमेशा अप्रत्यक्ष होते हैं। लेखन लेनदेन आरंभकर्ता एक हेडर और डेटा से मिलकर एक पैकेज बनाता है। सर्जक स्वयं डेटा का आकार निर्धारित करता है, केवल MAX_PAYLOAD_SIZE प्रतिबंध को ध्यान में रखता है। पिछले पैराग्राफ में डेटा ट्रांसफर दर के बारे में जो कुछ भी कहा गया था वह विशेष रूप से लेनदेन लिखने के लिए संबंधित है। लेखन लेनदेन के लिए, डेटा ट्रांसफर दर को सैद्धांतिक रूप से अनुमानित किया जा सकता है और प्रेषित पैकेट के आकार पर इसकी निर्भरता को माप सकता है।

पढ़ने के लेन-देन के साथ, चीजें थोड़ी अधिक जटिल हैं। रीड ट्रांजैक्शन का आरंभकर्ता सबसे पहले एक रीड रिक्वेस्ट तैयार करता है - एक छोटा पैकेट जिसमें केवल हेडर होता है। यह पैकेज बताता है कि कहां (किस पते से) और कितना डेटा पढ़ा जाना चाहिए। एक समय में अनुरोधित अधिकतम डेटा MAX_READ_REQUEST_SIZE पैरामीटर द्वारा निर्धारित किया जाता है और आमतौर पर 4 KB है। आमतौर पर, परिधीय रैम में रीड रिक्वेस्ट बनाते हैं, लेकिन किसी अन्य डिवाइस से डेटा का अनुरोध कर सकते हैं। जब कोई डिवाइस (परिधीय या रैम नियंत्रक) एक रीड रिक्वेस्ट प्राप्त करता है, तो यह पहले इसकी मेमोरी से आवश्यक डेटा का अनुरोध करता है, और फिर पीसीआई एक्सप्रेस बस के माध्यम से ट्रांजैक्शन सर्जक को रिटर्न रिस्पॉन्स पूरा करने वाले पैकेट्स देता है।

उसी समय, यह स्वयं लौटे हुए पैकेट के आकार को निर्धारित करता है, फिर से केवल MAX_PAYLOAD_SIZE प्रतिबंध को ध्यान में रखता है। लेन-देन आरंभकर्ता लौटे पैकेट के आकार को प्रभावित नहीं कर सकता है। आमतौर पर, RAM कंट्रोलर MAX_PAYLOAD_SIZE के बराबर डेटा लंबाई के साथ पैकेट लौटाएगा।रीड ट्रांजेक्शन के लिए डेटा ट्रांसफर रेट कई कारणों से मूल्यांकन करना मुश्किल है। सबसे पहले, दो प्रकार के पैकेट उत्पन्न होते हैं जो विपरीत दिशाओं में चलते हैं - अनुरोध और अंतिम प्रतिक्रियाएं पढ़ें। दूसरे, रैम से पढ़ते समय होने वाली देरी से डेटा ट्रांसफर की गति प्रभावित होगी। अंत में, यह स्पष्ट नहीं है कि पैकेट में डेटा की मात्रा पर डेटा दर की निर्भरता का पता कैसे लगाया जाए। इसलिए, इस काम में, हमने डेटा के अंतिम बाइट के आगमन के लिए पहला रीड अनुरोध भेजने से अभिन्न समय को मापा, इसका उपयोग करते हुए हमने रैम से डेटा पढ़ने की गति की गणना की और पैकेट के आकार पर इसकी निर्भरता का पता नहीं लगाया।पीसीआई एक्सप्रेस बस लेन-देन के स्तर पर विश्वसनीय डेटा ट्रांसमिशन प्रदान करती है, यानी, डेटा भेजकर, एजेंट (टर्मिनल डिवाइस और इंटरमीडिएट स्विच) स्वचालित रूप से पैकेट के चेकसम की गणना करते हैं, इसे पैकेट में ही एन्कोडेड के साथ तुलना करें और ट्रांसमिशन त्रुटि का पता चलने पर पुनर्प्राप्ति की आवश्यकता होती है डेटा। हालांकि, इसका मतलब यह नहीं है कि होस्ट एप्लिकेशन या FPGA योजना प्रोग्रामर त्रुटि के परिणामस्वरूप गलत डेटा उत्पन्न और संचारित नहीं कर सकती है। इसलिए, हमारे सर्किट की शुद्धता को सत्यापित करने के लिए, जिसमें एप्लिकेशन, ड्राइवर और FPGA सर्किट शामिल हैं, डेटा ट्रांसफर की शुद्धता के लिए चेक किए गए थे। इसके लिए, पहले उपयोगकर्ता आईपी योजना का उपयोग किया गया था, जिसमें RX_FIFO आउटपुट TX_FIFO इनपुट के लिए बंद था। FIFO कतारों का आकार 4 KB था। दो प्रयोग किए गए।पहले में, होस्ट ने क्रमिक रूप से FPGA में 4 KB डेटा दर्ज किया, फिर इसे पढ़ा और तुलना की गई। दूसरे प्रयोग ने इस तथ्य का उपयोग किया कि FPGAs को डेटा प्राप्त करने और संचारित करने के लिए पथ समानांतर में काम कर सकते हैं। होस्ट ने पहले लिखने और पढ़ने के संचालन दोनों को प्रोग्राम किया, और फिर FPGA ने RAM से डेटा पढ़ना शुरू किया, और जैसे ही यह पहली बार RX_FIFO और फिर TX_FIFO पर पहुंचा, उसने तुरंत RAM पर वापस लिखना शुरू कर दिया। इसने हमें RX_FIFO और TX_FIFO कतारों (हमारे प्रयोग में, 4 एमबी) के आकार की तुलना में एक समय में बहुत अधिक मात्रा में डेटा स्थानांतरित करने की अनुमति दी। दोनों प्रयोगों में, प्रेषित और प्राप्त डेटा की तुलना सफल रही, जिसने हमें अपने सर्किट के सही संचालन का न्याय करने की अनुमति दी।मेजबान ने पहले लिखने और पढ़ने के संचालन दोनों को प्रोग्राम किया, और फिर FPGA ने RAM से डेटा पढ़ना शुरू किया, और जैसे ही यह पहली बार RX_FIFO, और फिर TX_FIFO में पहुंचा, उसने तुरंत RAM पर वापस लिखना शुरू कर दिया। इसने हमें RX_FIFO और TX_FIFO कतारों (हमारे प्रयोग में, 4 एमबी) के आकार की तुलना में एक समय में बहुत अधिक मात्रा में डेटा स्थानांतरित करने की अनुमति दी। दोनों प्रयोगों में, प्रेषित और प्राप्त डेटा की तुलना सफल रही, जिसने हमें अपने सर्किट के सही संचालन का न्याय करने की अनुमति दी।मेजबान ने पहले लिखने और पढ़ने के संचालन दोनों को प्रोग्राम किया, और फिर FPGA ने RAM से डेटा पढ़ना शुरू किया, और जैसे ही यह पहली बार RX_FIFO, और फिर TX_FIFO में पहुंचा, उसने तुरंत RAM पर वापस लिखना शुरू कर दिया। इसने हमें RX_FIFO और TX_FIFO कतारों (हमारे प्रयोग में, 4 एमबी) के आकार की तुलना में एक समय में बहुत अधिक मात्रा में डेटा स्थानांतरित करने की अनुमति दी। दोनों प्रयोगों में, प्रेषित और प्राप्त डेटा की तुलना सफल रही, जिसने हमें अपने सर्किट के सही संचालन का न्याय करने की अनुमति दी।दोनों प्रयोगों में, प्रेषित और प्राप्त डेटा की तुलना सफल रही, जिसने हमें अपने सर्किट के सही संचालन का न्याय करने की अनुमति दी।दोनों प्रयोगों में, प्रेषित और प्राप्त डेटा की तुलना सफल रही, जिसने हमें अपने सर्किट के सही संचालन का न्याय करने की अनुमति दी।डेटा ट्रांसफर दर को मापने के लिए प्रयोग संचारित पैकेट में डेटा के आकार पर एक एफपीजीए डिवाइस की रैम में लिखने की गति की निर्भरता को मापने के साथ शुरू हुआ। 8, 16, 32, 64 और 128 बाइट्स के पेलोड मूल्यों के साथ प्रयोग किए गए थे। प्रत्येक प्रयोग में, 4 एमबी को एक तरह से स्थानांतरित किया गया था। Virtex7 - RAM पथ में अड़चन FPGA और RC47 बोर्ड पर PCI एक्सप्रेस स्विच (चित्र 1 देखें) के बीच PCI एक्सप्रेस x4 जनरल 2.0 कनेक्शन था। परिणाम अंजीर में प्रस्तुत किए जाते हैं। 3. ऊपरी Voryory वक्र पैकेट लंबाई (PCI Express x4 Gen 2.0 इंटरफ़ेस के लिए) पर अधिकतम प्राप्त डेटा हस्तांतरण दर के सैद्धांतिक निर्भरता (सूत्र 1) का प्रतिनिधित्व करता है। व्रद के मध्य में वक्र गति का प्रतिनिधित्व करता है,FPGA में एक हार्डवेयर टाइमर का उपयोग करके और पीसीआई एक्सप्रेस बस पर सीधे डेटा हस्तांतरण को ध्यान में रखते हुए मापा जाता है (समय डेटा के पहले पैकेट के प्रसारण की शुरुआत से अंतिम के हस्तांतरण के अंत तक मापा गया था)। अंत में, Vapp वक्र होस्ट पर एप्लिकेशन में मापी गई गति (रीड सिस्टम कॉल का निष्पादन समय मापा गया था) का प्रतिनिधित्व करता है।

अंजीर।

3 इंटरफ़ेस PCI एक्सप्रेस x4 Gen 2.0 के लिए पैकेट की लंबाई पर रैम में लिखने की गति की निर्भरताग्राफ से पता चलता है कि 64 बाइट से कम पेलोड मूल्यों के साथ, Vhard की तुलना में Vhard और Vapp की गति बहुत कम है। ऐसा इसलिए है क्योंकि इस मामले में, डीडीआर रैम मेमोरी डेटा रिसीवर के रूप में कार्य करती है, जो केवल फट मोड में उच्च लेखन गति प्रदान करती है, एक लेनदेन में बड़ी मात्रा में डेटा स्थानांतरित करती है। 128 बाइट्स के एक पैकेट के लिए, भार = 1451 एमबी / एस, जो 1612 एमबी / एस के अधिकतम मूल्य का 90% है। यह भी देखा गया है कि Vapp एप्लिकेशन (पेलोड = 128 के साथ 1146 MB / s) में मापी गई गति 64 बाइट्स से शुरू होने वाले पेलोड मूल्यों के लिए वॉर्ड की तुलना में बहुत कम है। यह इस तथ्य के कारण है कि 4 एमबी डेटा ट्रांसमिट करते समय, लगभग 1000 पेज डिस्क्रिप्टर बनते हैं, जो प्रोसेसर एफपीजीए को लिखता है। यह प्रारंभिक विलंब (1 एमएस के आदेश) डेटा दर को महत्वपूर्ण रूप से प्रभावित करता है।पेलोड = 128 बाइट्स के लिए कुल रीड सिस्टम कॉल निष्पादन समय लगभग 3.7 एमएस है। यदि हम इस समय से 1 एमएस की प्रारंभिक देरी को दूर करते हैं, तो हमें लगभग 1450 एमबी / एस के बराबर गति मिलती है, जो हार्डवेयर में मापा गया व्रड गति के साथ मेल खाता है।हमारी योजना में डीएमए ट्रांसफर करते समय शुरुआती देरी को कम करने के लिए ड्राइवर लॉजिक और रोस्टा डीएमए इंजन सर्किट्री को बदलना शामिल है। सुधार का विचार उपयोगकर्ता बफ़र के पेज डिस्क्रिप्टर की पूरी सूची को FPGA में स्थानांतरित करना नहीं है, बल्कि इसे RAM में FPGA के लिए सुलभ क्षेत्र में सहेजना है। तब FPGA स्वयं RAM से वर्णनकर्ताओं को पढ़ने में सक्षम होगा, जिस पर डेटा पहले से ही प्रसारित किया जाएगा। मेमोरी और वास्तविक डेटा ट्रांसफर से डिस्क्रिप्टर को पढ़ने की प्रक्रिया को समानांतर में शुरू किया जा सकता है, जिससे शुरुआती देरी को काफी कम किया जा सकता है और इसके परिणामस्वरूप डेटा ट्रांसफर की गति बढ़ जाती है। इस बीच, हम हार्डवेयर में मापी गई गति पर ध्यान केंद्रित करेंगे। इसके अलावा, बाद के प्रयोगों में 128 बाइट से कम पेलोड के साथ डेटा ट्रांसफर की जांच नहीं की जाएगी।अगले प्रयोग में, अलग-अलग FPGAs से जुड़े कई डेटा प्रसारण एक साथ लॉन्च किए गए। मेजबान पर एक एप्लिकेशन ने कई थ्रेड थ्रेड शुरू किए - एक धागा प्रति अलग ट्रांसमिशन। प्रत्येक थ्रेड में, FPGA को पहले RAM से पढ़ने के लिए और फिर लिखने के लिए प्रोग्राम किया गया था। अनुप्रयोग में बाधा सिंक्रनाइज़ेशन का उपयोग करके एक साथ संचरण प्राप्त किया गया था। प्रेषित बफर का आकार 4 एमबी था, रिकॉर्डिंग के दौरान पैकेट का आकार 128 बाइट्स था। इस प्रयोग में RB-8V7 यूनिट में निहित सभी 8 वीरटेक्स 7 एफपीजीए डिवाइस शामिल थे। रैम में डेटा की गति लेखन, एक साथ संचालित FPGAs की संख्या के आधार पर अंजीर में प्रस्तुत की जाती है। 4।

अंजीर।

4 एक साथ लेन-देन की संख्या पर रैम में लिखने की गति की निर्भरता(V_average V_average_app) , . PCI Express x4 Gen 2.0, 1451 /. V_sum V_sum_app – . Vmax = 3225 / , . PCI Express x8 Gen 2.0 RHA-25 . (1451 /), Vmax. , , Vmax. , Vmax, «» . , PCI Express . - , . , . , . , 100%, .

इसी तरह, हम रैम (छवि 5) से पढ़ने के मामले पर विचार कर सकते हैं।

अंजीर।

5 एक साथ लेनदेन की संख्या पर रैम से रीड स्पीड की निर्भरता।यहां आप देख सकते हैं कि एक से तीन उपकरणों से जुड़े डेटा ट्रांसफर के लिए, प्रत्येक डिवाइस के लिए रीड स्पीड एक समान है और 1000 एमबी / एस के बराबर है। चार उपकरणों के साथ शुरू, गति मेजबान के साथ संचार चैनल के बैंडविड्थ द्वारा सीमित है।ट्रांसमिशन FPGA-FPGA

पीसीआई एक्सप्रेस बस पर मेमोरी लिखने और पढ़ने के लिए अनुरोध पैकेट हेडर में एन्कोड किए गए पते के अनुसार भेजे जाते हैं। मास्टर एक मनमाने पते के साथ एक पैकेट बनाने में सक्षम है। यह पता रैम में इंगित हो सकता है, या किसी अन्य परिधीय उपकरण को आवंटित पते के क्षेत्र से संबंधित हो सकता है। बाद के मामले में, अनुरोध पैकेट को एक डिवाइस से दूसरे में भेजा जाएगा। हमारे मामले में, विभिन्न FPGAs के बीच अनुरोधों को इस प्रकार प्रेषित किया गया था। कोई पठन परीक्षण नहीं किया गया।प्रत्येक FPGA BIOS या ऑपरेटिंग सिस्टम से उन पतों की एक श्रृंखला प्राप्त करता है जिन पर आप इस उपकरण से संपर्क कर सकते हैं। FPGA A से FPGA B तक डेटा ट्रांसफर प्रोग्राम करने के लिए, होस्ट पर एप्लिकेशन को FPGA A (यूजर IP ब्लॉक में संबंधित रजिस्टर में लिखें) FPGA B का आधार पता सूचित करना चाहिए। RSTAMA इंजन में FPGA में, हार्डवेयर इंटरफ़ेस EP EP CMD लागू किया गया था, जिसका उद्देश्य था। सर्किट से दूसरे FPGA में डेटा ट्रांसफर शुरू करना। सर्किट EP_TX_FIFO को ट्रांसमिशन के लिए डेटा लिखता है और ईपी TX CMD इंटरफ़ेस के माध्यम से अन्य डिवाइस के आधार पते और ट्रांसमिशन लंबाई को प्रसारित करता है। इसके बाद, रोस्टा डीएमए इंजन ब्लॉक में TX_STATE_MACHINE ट्रांसमिटिंग मशीन EP_TX_FIFO से निर्दिष्ट पते पर डेटा संचारित करना शुरू करती है। FPGA प्राप्त करने में, डेटा को EP_RX_FIFO कतार में लिखा जाता है।इसके साथ शुरू करने के लिए, FPGAs के बीच डेटा हस्तांतरण की शुद्धता को सत्यापित करना आवश्यक था। इसके लिए, निम्नलिखित प्रयोग किया गया था। ट्रांसमिशन में सभी 8 वीरटेक्स 7 एफपीजीए के अनुक्रम शामिल थे जो आरबी -8 वी 7 ब्लॉक (छवि 6) का हिस्सा हैं।

अंजीर।

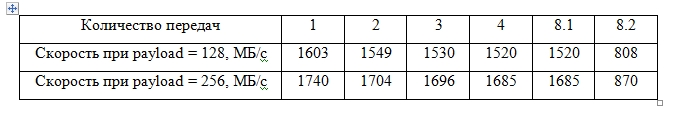

6 डेटा ट्रांसमिशन स्कीम HOST-FPGA-HOSTपहले 7 FPGAs में, मेजबान ने निम्नलिखित योजना के अनुसार उपकरणों के आधार पते दर्ज किए। पहले डिवाइस में - दूसरे का आधार पता, तीसरे में - तीसरा, और इसी तरह। होस्ट ने रैम से डेटा पढ़ने और दूसरे डेटा पर रीड डेटा ट्रांसफर करने के लिए पहला डिवाइस प्रोग्राम किया था। ऐसा करने के लिए, उपयोगकर्ता IP में, उपयोगकर्ता IP रजिस्टरों के माध्यम से इंटरकनेक्ट स्विचिंग यूनिट को आउटपुट RX_FIFO EP_TX_FIFO इनपुट से कनेक्ट करने के लिए कॉन्फ़िगर किया गया था। श्रृंखला में अगले में डेटा स्थानांतरित करने के लिए डिवाइस 2-7 को कॉन्फ़िगर किया गया था। उनमें, इंटरकनेक्ट ब्लॉक को EP_RX_FIFO को इनपुट EP_TX_FIFO से जोड़ने के लिए कॉन्फ़िगर किया गया था। अंत में, आठवें उपकरण को RAM में TX_FIFO के माध्यम से EP_RX_FIFO में प्राप्त डेटा प्रसारित करने के लिए प्रोग्राम किया गया था। स्थानांतरण के बाद, मेजबान ने डेटा की तुलना की। इस प्रयोग में, पथ में डेटा दर भी मापा गया था। यह एक FPGA डिवाइस के साथ रैम से पढ़ने की गति के बराबर था।यह सुनिश्चित करने के बाद कि डेटा स्थानांतरण सही था, गति की माप के लिए आगे बढ़ना संभव था। इस तथ्य के कारण कि चिपसेट द्वारा समर्थित अधिकतम पैकेट लंबाई 128 बाइट्स थी, सिस्टम में सभी स्विच और टर्मिनलों के लिए MAX_PAYLOAD_SIZE पैरामीटर 128 बाइट्स पर सेट किया गया था। इसलिए, डिफ़ॉल्ट रूप से, FPGAs के बीच डेटा संचरण समान लंबाई के पैकेट में था। हालाँकि, यह देखा गया कि RC-47 बोर्ड और RHA-25 एडॉप्टर पर स्थित मध्यवर्ती PCI एक्सप्रेस स्विच, साथ ही PCI एक्सप्रेस FPGA के अंदर इंटरफेस, 256 बाइट्स के पैकेट लंबाई का समर्थन करता है। उसी समय, चिपसेट ने खुद को FPGAs के बीच डेटा के हस्तांतरण में भाग नहीं लिया। यह सुझाव दिया गया था कि यदि आप FPGA-FPGA डेटा पथ में सभी डिवाइसों के लिए MAX_PAYLOAD_SIZE को 256 के बराबर कॉन्फ़िगर करते हैं, तो आप इस तथ्य के बावजूद, लंबाई में 256 बाइट्स के पैकेट संचारित करना शुरू कर सकते हैं।कि चिपसेट केवल 128 का समर्थन करता है।लिनक्स का उपयोग करके MAX_PAYLOAD_SIZE पैरामीटर को बदलने के लिए, सेटपसी कमांड का उपयोग सभी डिवाइसों के लिए PCI एक्सप्रेस डिवाइस कंट्रोल रजिस्टर और RHA-25 और RC-47 बोर्डों पर पोर्ट स्विच करने के लिए किया गया था। रोस्टा डीएमए इंजन ब्लॉक को भी संशोधित किया गया है ताकि 256 बाइट्स के पैकेट उत्पन्न हो सकें। जिसके बाद पैनकेक पैकेट 256 से डेटा ट्रांसफर को व्यवस्थित करना वास्तव में संभव हो गया, और डेटा ट्रांसफर दर में वृद्धि हुई।FPGA-FPGA रिकॉर्डिंग गति माप एक साथ प्रसारण के विभिन्न नंबरों के लिए किए गए थे। परिणाम तालिका 3. तालिका 3 में प्रस्तुत किए गए हैं। 128 और 256 बाइट्स के पैकेट लंबाई के साथ एक साथ प्रसारण की संख्या पर FPGA-FPGA की रिकॉर्डिंग गति की निर्भरता।पहले चार मामलों में, ट्रांसफर उसी RC47 बोर्ड पर उपकरणों के बीच चला गया। एक डाटा ट्रांसफर के दौरान अधिकतम लिखने की गति प्राप्त की गई और 128 बाइट्स की पैकेट लंबाई के लिए 1603 एमबी / एस और 256 बाइट्स की एक पैकेट लंबाई के लिए 1740 एमबी / एस की राशि प्राप्त की गई। दोनों मामलों में, इसी पैकेट लंबाई के लिए अधिकतम संभव 99% की गति थी।8.1 और 8.2 मामलों के लिए डिवाइस इंटरेक्शन योजनाएं अंजीर में प्रस्तुत की जाती हैं।

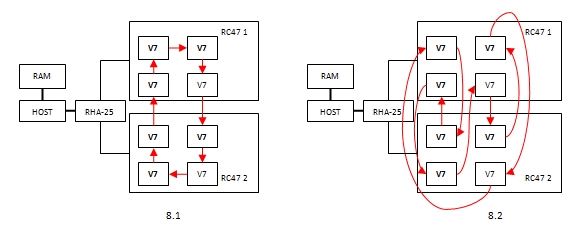

तालिका 3 में प्रस्तुत किए गए हैं। 128 और 256 बाइट्स के पैकेट लंबाई के साथ एक साथ प्रसारण की संख्या पर FPGA-FPGA की रिकॉर्डिंग गति की निर्भरता।पहले चार मामलों में, ट्रांसफर उसी RC47 बोर्ड पर उपकरणों के बीच चला गया। एक डाटा ट्रांसफर के दौरान अधिकतम लिखने की गति प्राप्त की गई और 128 बाइट्स की पैकेट लंबाई के लिए 1603 एमबी / एस और 256 बाइट्स की एक पैकेट लंबाई के लिए 1740 एमबी / एस की राशि प्राप्त की गई। दोनों मामलों में, इसी पैकेट लंबाई के लिए अधिकतम संभव 99% की गति थी।8.1 और 8.2 मामलों के लिए डिवाइस इंटरेक्शन योजनाएं अंजीर में प्रस्तुत की जाती हैं। 7।

अंजीर।

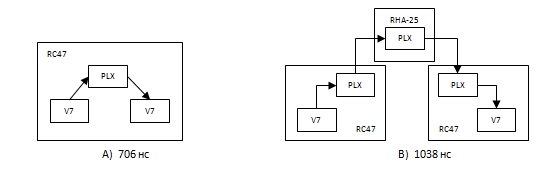

8 एक साथ स्थानान्तरण के मामले में 7 FPGA बातचीत8.1 के मामले में, डेटा को FPGA से FPGA तक क्रमिक रूप से प्रेषित किया गया था, पहले एक बोर्ड पर एक सर्कल में, और फिर बाहरी केबल कनेक्शन और RHA-25 एडाप्टर के माध्यम से, दूसरे बोर्ड पर FPGA तक संचरण जारी रहा। दूसरे बोर्ड पर, डेटा भी क्रमिक रूप से एक FPGA से दूसरे में कॉपी किया गया था, और फिर पहले पर वापस आ गया। नतीजतन, आरएचए -25 एडाप्टर के माध्यम से, एक डेटा ट्रांसमिशन प्रत्येक पक्ष में चला गया, और पीसीआई एक्सप्रेस एक्स 4 जनरल 3.0 केबल कनेक्शन ने किसी भी तरह से अपनी गति को सीमित नहीं किया। 8.2 मामले में, डेटा को एक FPGA से दूसरे में स्थानांतरित किया गया था, लेकिन दूसरे बोर्ड पर स्थित था। परिणामस्वरूप, प्रत्येक दिशा में RHA-25 एडाप्टर, 4 के माध्यम से 8 युगपत प्रसारण थे। 128 बाइट्स की एक पैकेट लंबाई के लिए, एक दिशा में सामान्य डेटा प्रवाह की गति 4 * 1520 = 6080 एमबी / एस थी, जो पीसीआई एक्सप्रेस एक्स 4 जनरल 3.0 चैनल के लिए अधिकतम गति 3225 एमबी / एस के बराबर है।इसलिए, चैनल की गति को उपकरणों के बीच समान रूप से विभाजित किया जाना चाहिए, और प्रत्येक जोड़ी में औसत डेटा अंतरण दर 3225/4 = 806 एमबी / एस हो जाना चाहिए। इसकी पुष्टि 808 एमबी / एस के मापा मूल्य से की जाती है। इसलिए, यह तर्क दिया जा सकता है कि बोर्डों के बीच संचार चैनल 100% लगे। 256 बाइट्स की लंबाई के साथ पैकेट संचारित करने के लिए एक ही तर्क बनाया जा सकता है।अंत में, डेटा ट्रांसमिशन लेटेंसी को मापने के लिए एक प्रयोग किया गया। प्रयोग का विचार इस प्रकार था। FPGA A, FPGA B को डेटा भेजता है और हार्डवेयर टाइमर शुरू करता है। विभिन्न उपकरणों में घड़ी को सिंक्रनाइज़ करना मुश्किल है, इसलिए टाइमर का उपयोग केवल FPGA ए में किया जाता है। जैसे ही FPGA B डेटा प्राप्त करता है, यह तुरंत उन्हें FPGA ए पर वापस लिखना शुरू कर देता है। जैसे ही FPGA A डेटा का पहला पैकेट प्राप्त करता है, टाइमर बंद हो जाता है। टाइमर मान एक FPGA के उपयोगकर्ता IP ब्लॉक और दूसरे के उपयोगकर्ता IP के बीच डेटा हस्तांतरण की दोगुनी विलंबता का प्रतिनिधित्व करता है। विलंबता को दो मामलों में मापा गया था: एक आरसी -47 बोर्ड पर FPGAs के बीच संचरण के दौरान (छवि 8 ए) और विभिन्न बोर्डों पर FPGAs के बीच (छवि 8 बी)।

अंजीर।

8 विलंबता मापने के लिए डेटा ट्रांसमिशन योजनाएँजब समान RC-47 बोर्ड पर उपकरणों के बीच डेटा संचारित करती हैं, तो ट्रांसमिशन पथ में एक PLX स्विच होता था, और विलंब 706 ns था। बोर्ड से बोर्ड पर स्थानांतरित करते समय, तीन मध्यवर्ती स्विच थे, और देरी 1038 एनएस थी। इस डेटा से, आप FPGA में होने वाली देरी का निर्धारण कर सकते हैं और स्विच द्वारा प्रस्तुत किया जा सकता है। रिसेप्शन और ट्रांसमिशन में FPGA में देरी 270 ns के बराबर होती है, और 166 ns स्विच में, जो कि 150 ns के PLX टेक्नोलॉजी द्वारा घोषित स्विच की विलंबता के साथ अच्छा समझौता है।निष्कर्ष

इस पत्र में, कई FPGAs की एक साथ भागीदारी के साथ PCI एक्सप्रेस बस के माध्यम से डेटा हस्तांतरण का वर्णन किया गया था। RAM में लिखते समय, PCIe x4 Gen 2.0 कनेक्शन के लिए अधिकतम 90% के बराबर गति 128 बाइट्स की पैकेट लंबाई (1451 MB / s) के साथ प्राप्त की गई थी। रैम से पढ़ते समय, गति 1000 एमबी / एस थी। एक साथ FPGA-HOST प्रसारण के मामले में, डेटा अंतरण दर में कमी नहीं हुई, जब तक कि एक साथ प्रसारण की संख्या मेजबान के साथ संचार के एक संकीर्ण चैनल को संतृप्त नहीं करती, भविष्य में चैनल का उपयोग 100% पर किया गया था, और इसकी बैंडविड्थ उपकरणों के बीच समान रूप से साझा की गई थी।FPGA-FPGA ट्रांसमिशन के दौरान, 256-बाइट पैकेटों का आदान-प्रदान शुरू करना संभव था, हालाँकि मेजबान कंप्यूटर के चिपसेट ने केवल 128 का समर्थन किया था। इस मामले में, हम 1740 एमबी / सेकेंड की गति प्राप्त करने में कामयाब रहे, जो कि पीसीआई एक्सप्रेस x4 जनरल 2.0 इंटरफ़ेस की अधिकतम अंतरण गति का 99% लंबाई के साथ है। 256 बाइट पैकेट। यह भी दिखाया गया कि कई एक साथ FPGA-FPGA प्रसारण शुरू करना संभव है, और जबकि कुल संचरण की गति सामान्य चैनल की बैंडविड्थ से अधिक नहीं है, व्यक्तिगत प्रसारण की गति कम नहीं होती है, और फिर चैनल का उपयोग 100% तक किया जाता है, और इसकी बैंडविड्थ को उपकरणों के बीच समान रूप से विभाजित किया जाता है।FPGA-FPGA डेटा ट्रांसमिशन विलंबता को मापा गया था, जो एक मध्यवर्ती स्विच के लिए 706 एनएस और तीन के लिए 1038 एनएस था।यह सब हमें यह विचार करने की अनुमति देता है कि पीसीआई एक्सप्रेस एक्सिलिनएक्स इंटरफ़ेस और पीएलएक्स टेक्नोलॉजी स्विच के एफपीजीए और आईपी कोर के उपयोग पर आधारित दृष्टिकोण का उपयोग कंप्यूटर के स्थानीय पीसीआई एक्सप्रेस बस से जुड़े बड़ी संख्या में एफपीजीए के बीच डेटा विनिमय को व्यवस्थित करने के लिए किया जा सकता है।संदर्भ

1. Rosta LTD, 2013.

www.rosta.ru .

2. nVidiaCorporation. GPUDirect.

developer.nvidia.com/gpudirect .

3. Ra Inta, David J. Bowman, Susan M. Scott, «The “Chimera”: An Off-The-Shelf CPU GPGPU FPGA Hybrid Computing Platform», International Journal of Reconfigurable Computing, 2012.

4. Bruno da Silva, An Braeken, Erik H. D'Hollander, Abdellah Touhafi, Jan G. Cornelis, Jan Lemeire, «Performance and toolchain of a combined GPU/FPGA desktop», Proceedings of the ACM/SIGDA international symposium on Field programmable gate arrays, 2013.

5. Ray Bittner, Erik Ruf, Alessandro Forin, «Direct GPU/FPGA Communication Via PCI Express», Cluster Computing, 2013.

6. सुनीता जैन, गुरु प्रसन्ना, “पीसीआई एक्सप्रेस डिज़ाइन के लिए इंटीग्रेटेड एंडपॉइंट ब्लॉक का उपयोग करके पॉइंट-टू-पॉइंट कनेक्टिविटी”, Xilinx Corporation, XAPP869, 2007.7. 7 सीरीज FPGAs PCI ब्लॉक के लिए एकीकृत ब्लॉक v1.7 उत्पाद गाइड, Xilinx Corporation 2012.8. एलेक्स गोल्डहैमर, जॉन अयेर, "पीसीआई एक्सप्रेस सिस्टम के प्रदर्शन को समझना", Xilinx Corporation, WP350, 2008।