यह आलेख VHDL में ROM और RAM मॉड्यूल का वर्णन करने के लिए मूल सिद्धांतों को दर्शाता है। यह लेख शुरुआती लोगों के लिए है। इसका उद्देश्य VHDL भाषा में मेमोरी मॉड्यूल के विवरण के बारे में एक सामान्य अवधारणा देना है। उदाहरण और चित्र क्वार्ट्स II v के लिए प्रदान किए गए हैं। 9.1। यह माना जाता है कि पाठक को पता है कि क्वार्टस II पैकेज में एक परियोजना कैसे बनाई जाए, इसे संकलित करें और अनुकरण करें।

सामान्य प्रावधान

VHDL मेमोरी को वैक्टर

array एक

array रूप में वर्णित किया गया है। वेक्टर की थोड़ी गहराई मेमोरी सेल की चौड़ाई से निर्धारित होती है, और वैक्टर की संख्या मेमोरी मॉड्यूल में कोशिकाओं की संख्या से निर्धारित होती है।

उदाहरण के लिए, 32 कोशिकाओं के एक मेमोरी मॉड्यूल के लिए, जिनमें से प्रत्येक में 8 बिट्स होते हैं, 32 सरणी वाले एक सरणी को घोषित करना आवश्यक है, जिनमें से प्रत्येक आठ-बिट है।

type mem is array (0 to 31) of std_logic_vector (7 downto 0);

इसके बाद, पता इनपुट, डेटा इनपुट और आउटपुट, नियंत्रण संकेतों का वर्णन करना आवश्यक है। डेटा पोर्ट के प्रकार को एक सेल के डेटा प्रकार से मेल खाना चाहिए। उपरोक्त उदाहरण के लिए, यह

std_logic_vector (7 downto 0) ।

data_in: in std_logic_vector (7 downto 0); data_out: out std_logic_vector (7 downto 0);

पते के लिए डेटा प्रकार

integer या इसके आधार पर प्रकार हैं।

integer प्रकार आवश्यक है क्योंकि पते का उपयोग मेमोरी सरणी के सूचकांक के रूप में किया जाता है।

addr: in integer range 0 to 31;

मेमोरी का विवरण मॉड्यूल के पैरामीटर के द्वारा सबसे अच्छा किया जाता है। यह लिखित कोड के पुन: उपयोग की अनुमति देता है। निम्नलिखित एक 32 × 8 पैरामीटर वाले मॉड्यूल का एक उदाहरण है। उदाहरण में, स्मृति मॉड्यूल का वर्णन करने के लिए

addr_width और

data_width मापदंडों का उपयोग किया जाता है, जो क्रमशः पते और डेटा बसों की चौड़ाई निर्दिष्ट करते हैं। इस मामले में मेमोरी ब्लॉक में कोशिकाओं की संख्या को

2**addr_width रूप में परिभाषित किया गया है, और उनकी बिट क्षमता

data_width बराबर है।

generic (addr_width: natural:= 5; data_width: natural:=8); port ( addr: in integer range 0 to 2**addr_width - 1; data_in: in std_logic_vector (data_width-1 downto 0); data_out: out std_logic_vector (data_width-1 downto 0) ); type mem is array (2**addr_width-1 downto 0) of std_logic_vector (7 downto 0);

VHDL भाषा में केवल-पढ़ने के लिए मेमोरी डिवाइस का विवरण

रीड-ओनली मेमोरी डिवाइस का वर्णन करते समय, प्रोग्राम लिखते समय कोशिकाओं की सामग्री का निर्धारण किया जाना चाहिए। आप मेमोरी की सामग्री निर्धारित करने के लिए कई विकल्पों का उपयोग कर सकते हैं:

- "सरणी" प्रकार के एक स्थिर या संकेत का निर्माण;

case ऑपरेटर का उपयोग;- * .mif फ़ाइल और संश्लेषण विशेषताओं का उपयोग।

तीन विकल्पों में से, पहले दो को किसी भी निर्माता के FPGAs पर लागू किया जा सकता है, और तीसरा केवल क्वार्टस II पैकेज में संभव है।

एक स्थिर या एक सरणी का उपयोग करके मेमोरी की सामग्री का निर्धारण करना।

इस विकल्प का उपयोग करते समय, आपको पहले एक प्रकार घोषित करना होगा जो मेमोरी ब्लॉक के आकार से मेल खाएगा। फिर इस प्रकार का एक स्थिरांक घोषित किया जाता है और सरणी के सभी कक्षों की सामग्री निर्धारित की जाती है।

उदाहरण के लिए, नए प्रकार की ROM घोषित करें, जो कि 8 कोशिकाओं की एक सरणी है, जिनमें से प्रत्येक का आकार 8 बिट्स है। फिर हम टाइप रॉम के कंटेंट कंटेंट को परिभाषित करते हैं।

type ROM is array (0 to 7) of std_logic_vector (7 downto 0); constant Content: ROM := ( 0 => "00000001", 1 => "00000010", 2 => "00000011", 3 => "00000100", 4 => "00000101", 5 => "00000110", 6 => "00000111", 7 => "00001000", );

ऐसे स्थिरांक का उपयोग करने के लिए, आपको बस पता लाइनों से इनपुट का उपयोग करके सरणी में आवश्यक सेल को संबोधित करना होगा। स्रोत डेटा पोर्ट उसी प्रकार का होना चाहिए जो मेमोरी ब्लॉक के सेल प्रकार का होता है। उपरोक्त उदाहरण के लिए, स्रोत

Data_out पोर्ट

std_logic_vector (7 downto 0) प्रकार का होना चाहिए। मेमोरी की सामग्री तक पहुंच इस तरह होगी:

Data_out <= Content (Addr);

उदाहरण 1. एक स्थिर का उपयोग करके मेमोरी ब्लॉक के पूर्ण विवरण का एक उदाहरण पर विचार करें। इस विवरण से मिलने वाला मेमोरी ब्लॉक चित्र 1 में दिखाया गया है।

चित्र 1 - उदाहरण 1 में वर्णित मेमोरी ब्लॉक

लाइन्स 13 और 14 एक सरणी प्रकार की 32 कोशिकाओं की घोषणा करते हैं, जिनमें से प्रत्येक में 8 बिट्स होते हैं।

23 के माध्यम से लाइनें 15 सरणी में कोशिकाओं के मूल्य को निर्दिष्ट करती हैं। अलग-अलग, मान केवल पहले 16 कोशिकाओं के लिए निर्धारित किए जाते हैं - रेखाएँ 16 22 के माध्यम से। अन्य सभी कोशिकाएँ समान मूल्य "1111 1111" से भरी होती हैं, जो अन्य शब्द - 23 लाइन का उपयोग करती हैं।

मेमोरी मॉड्यूल के संचालन को प्रक्रिया ऑपरेटर का उपयोग करके वर्णित किया गया है, जिनमें से प्रारंभिक सूची में क्रमशः संकेत

clk ,

cs - घड़ी और क्रिस्टल चयन शामिल हैं। यदि सिग्नल

cs एकता के बराबर है, तो प्रारंभिक रॉम लाइनें जेड-स्टेट (लाइनें 27 और 28) में जाती हैं। यदि सिग्नल

cs शून्य के बराबर है, तो आउटपुट कार्यशील स्थिति में जाते हैं और माइक्रोकिरिट काम करता है।

क्लॉक सिग्नल

clk के प्रमुख किनारे के लिए लाइन 29 चेक।

लाइनें 30-35 रॉम से पढ़ने की जानकारी की प्रक्रिया का वर्णन करती हैं। यदि सिग्नल

rd एक के बराबर है, तो जानकारी को पढ़ने की अनुमति है, यदि यह शून्य के बराबर है, तो प्रारंभिक लाइनें जेड-राज्य (लाइन 32) में जाती हैं। मेमोरी मॉड्यूल में एक विशिष्ट सेल तक पहुंचने के लिए, लाइन 30 का उपयोग किया जाता है। कंटेंट स्थिरांक

std_logic_vector सेल डेटा प्रकार का होता है, जो मूल

data_out सिग्नल के प्रकार से मेल खाता है। मेमोरी मॉड्यूल में एड्रेस सिग्नल भी

std_logic_vector प्रकार का होता है, इसलिए, सामग्री सरणी में एक सेल को संबोधित करने के लिए, आवश्यक रूपांतरण

std_logic_vector प्रकार से

integer प्रकार का होता है, जो इस निर्माण में

to_integer (unsigned (address) निर्माण का उपयोग करके किया जाता है। इस निर्माण में

std_logic_vector सिग्नल पहले प्रकार का होता है। तब

integer प्रकार के लिए, और अधिक स्पष्ट रूप से

यहाँ रूपांतरण के बारे में।

1 library ieee; 2 use ieee.std_logic_1164.all; 3 use ieee.numeric_std.all; 4 entity ROM is 5 port (clk : in std_logic; 6 cs : in std_logic; 7 rd : in std_logic; 8 address : in std_logic_vector(4 downto 0); 9 data_out: out std_logic_vector(7 downto 0)); 10 end ROM; 11 architecture behav of ROM is 12 type ROM_array is array (0 to 31) 13 of std_logic_vector(7 downto 0); 14 constant content: ROM_array := ( 15 0 => "00000001", 16 1 => "00000010", 17 2 => "00000011", 18 . . . 19 12 => "00001101", 20 13 => "00001110", 21 14 => "00001111", 22 others => "11111111"); 23 begin 24 process(clk, cs) 25 begin 26 if(cs = '1' ) then 27 data_out <= "ZZZZZZZZ"; 28 elsif (clk'event and clk = '1') then 29 if rd = '1' then 30 data_out <= content(to_integer (unsigned (address))); 31 else 32 data_out <= "ZZZZZZZZ"; 33 end if; 34 end if; 35 end process; 36 end behav;

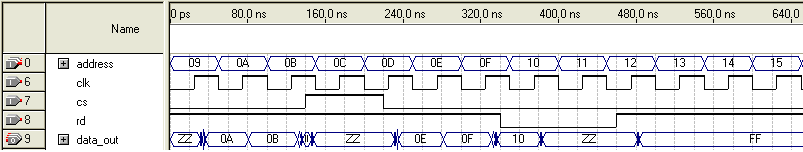

सिमुलेशन परिणाम चित्र 2 में दिखाए गए हैं।

चित्र 2 - मेमोरी ब्लॉक के सिमुलेशन के परिणाम

case का उपयोग करके मेमोरी की सामग्री का निर्धारण करना।

केस स्टेटमेंट का उपयोग करते समय, आपको पोर्ट घोषित करना चाहिए, और मेमोरी की सामग्री का निर्धारण आर्किटेक्चरल बॉडी में होता है। प्रत्येक पता मान इस मेमोरी सेल की सामग्री से मेल खाता है। डिजाइन इस तरह दिखेगा:

when => _ <= _;

उदाहरण 2. एक उदाहरण के रूप में, एक 256 × 6 मेमोरी मॉड्यूल के विवरण पर विचार करें। पता टाइप

std_logic आठ-बिट वेक्टर द्वारा वर्णित किया जाता

std_logic , डेटा आउटपुट को

std_logic छह-बिट वेक्टर द्वारा वर्णित किया जाता

std_logic । केस ऑपरेटर का उपयोग करते हुए, मेमोरी ब्लॉक की पहली दस कोशिकाओं की सामग्री को अलग-अलग निर्धारित किया जाता है,

when others स्टेटमेंट्स के साथ सभी अन्य को एक साथ परिभाषित किया जाता है।

library ieee; use ieee.std_logic_1164.all; entity mem is port ( clock : in std_logic; address : in std_logic_vector (7 downto 0); data_out : out std_logic_vector (5 downto 0)); end mem; architecture rtl of mem is begin process (clock) begin if rising_edge (clock) then case address is when "00000000" => data_out <= "000111"; when "00000001" => data_out <= "000110"; when "00000010" => data_out <= "000010"; when "00000011" => data_out <= "100000"; when "00000100" => data_out <= "100010"; when "00000101" => data_out <= "001110"; when "00000110" => data_out <= "111100"; when "00000111" => data_out <= "110111"; when "00001000" => data_out <= "111000"; when "00001001" => data_out <= "100110"; when others => data_out <= "101111"; end case; end if; end process; end rtl;

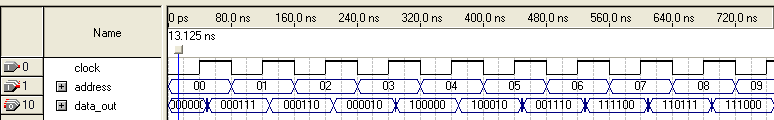

उदाहरण 2 से मेमोरी ब्लॉक के सिमुलेशन परिणाम चित्र 3 में दिखाए गए हैं।

चित्र 3 - उदाहरण 2 से मेमोरी ब्लॉक को मॉडलिंग करना

एक मिफ़ फ़ाइल का उपयोग करके मेमोरी की सामग्री का निर्धारण करना।

स्मृति की सामग्री को निर्धारित करने का यह विकल्प केवल एल्टर उत्पादों के साथ काम करता है, लेकिन यह आपको मेमोरी की सामग्री को बहुत तेज़ी से बदलने की भी अनुमति देता है। वर्णन करने के लिए, आपको Altera

altera_syn_attributes सिंथेसिस विशेषता लाइब्रेरी से कनेक्ट करना होगा और

ram_init_file विशेषता का उपयोग करना

ram_init_file । डिफ़ॉल्ट रूप से, लाइब्रेरी

_quartus\libraries\vhdl\altera फ़ोल्डर में स्थित है। यह विशेषता एक मिफ़ फ़ाइल निर्दिष्ट करती है जिसमें मेमोरी की सामग्री के बारे में जानकारी होती है।

इस विशेषता का उपयोग करने के लिए, आपको संश्लेषण विशेषता को एक स्ट्रिंग प्रकार के रूप में घोषित करना होगा:

attribute ram_init_file : string;

स्मृति ब्लॉक का वर्णन करने वाले संकेत के लिए

ram_init_file विशेषता को लिंक करें। विशेषता मान * .mif फ़ाइल के नाम से मेल खाना चाहिए:

attribute ram_init_file of rom : signal is "mem.mif";

उदाहरण 3. उदाहरण में 256 × 8 मेमोरी ब्लॉक का वर्णन है। लाइन्स 1-4 इन पुस्तकालयों के पुस्तकालयों और मॉड्यूल का वर्णन करते हैं। यह देखा जा सकता है कि लाइनें 1 और 4 संश्लेषण विशेषताओं के पुस्तकालय का वर्णन करती हैं।

लाइन्स 5-9 मॉड्यूल के इंटरफ़ेस भाग का वर्णन करते हैं।

लाइनें 11 और 12 इस प्रकार के

mem_t और सिग्नल

rom परिचय देती हैं, जो मेमोरी मॉड्यूल का वर्णन करते हैं।

पंक्ति 13 में, स्ट्रिंग प्रकार का

ram_init_file विशेषता सेट किया गया है, और 14 लाइन में यह विशेषता

rom सिग्नल के साथ जुड़ती है और एक लिंक मेम फ़ाइल में बनाई जाती है, जिसमें मेमोरी मॉड्यूल की सामग्री सूचीबद्ध होती है।

मेमोरी मॉड्यूल का उपयोग लाइन 19 में वर्णित है और सेल की सामग्री के स्रोत पोर्ट के लिए केवल आउटपुट का प्रतिनिधित्व करता है, जो पता सिग्नल द्वारा निर्धारित किया जाता है।

1 library ieee, altera; 2 use ieee.std_logic_1164.all; 3 use ieee.numeric_std.all; 4 use altera.altera_syn_attributes.all; 5 entity mem is 6 port (clk: in std_logic; 7 addr: in natural range 0 to 255; 8 q: out std_logic_vector (7 downto 0)); 9 end entity; 10 architecture rtl of mem is 11 type mem_t is array (255 downto 0) of std_logic_vector(7 downto 0); 12 signal rom: mem_t; 13 attribute ram_init_file: string; 14 attribute ram_init_file of rom: signal is "mem.mif"; 15 begin 16 process(clk) 17 begin 18 if(rising_edge(clk)) then 19 q <= rom(addr); 20 end if; 21 end process; 22 end rtl;

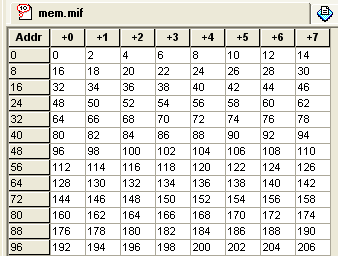

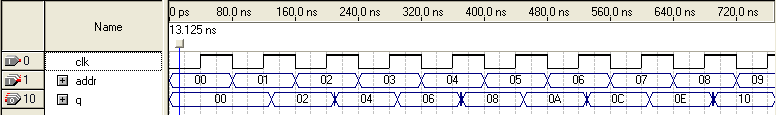

Mif फ़ाइल की सामग्री mif फ़ाइल संपादक का उपयोग करके निर्धारित की जाती है। दिए गए उदाहरण के लिए, मेमोरी की सामग्री के साथ विंडो को चित्र 4 में दिखाया गया है, और मॉड्यूलेशन के परिणाम चित्र 5 में दिखाए गए हैं।

चित्रा 4 - मेमोरी मॉड्यूल की सामग्री

चित्र 5 - उदाहरण 3 से मेमोरी मॉड्यूल के समय आरेख

रैंडम एक्सेस मेमोरी का विवरण

रैंडम एक्सेस मेमोरी (RAM) का वर्णन रीड-ओनली मेमोरी के विवरण से अलग है कि रैम में रिकॉर्ड करना संभव है।

एक उदाहरण के रूप में, समकालिक रैम पर विचार करें। उनका काम निम्नलिखित तालिका में वर्णित है:

| Wn_R | CSN | करो [3..0] | संचालन का तरीका |

|---|

| 0 | 0 | ZZZZ | अभिलेख |

| 1 | 0 | स्रोत डेटा | पढ़ना |

| × | 1 | ZZZZ | जानकारी सहेजना |

स्मृति के साथ काम करने के लिए पिछले उदाहरणों में, हम एक नए प्रकार को एक सरणी के रूप में परिभाषित करते हैं, जिसमें आवश्यक मेमोरी मॉड्यूल के आयाम हैं।

library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.numeric_std.all; entity mem is port (clk : in std_logic; Wn_R : in std_logic; CSn : in std_logic; addr : in std_logic_vector(4 downto 0); Di : in std_logic_vector(3 downto 0); Do : out std_logic_vector(3 downto 0)); end mem; architecture syn of mem is type ram_type is array (31 downto 0) of std_logic_vector (3 downto 0); signal RAM : ram_type; begin process (clk, CSn) begin if CSn = '0' then if (clk'event and clk = '1') then if (Wn_R = '0') then RAM(to_integer(unsigned(addr))) <= Di; Do <= "ZZZZ"; else Do <= RAM(to_integer(unsigned(addr))); end if; end if; else Do <= "ZZZZ"; end if; end process; end syn;

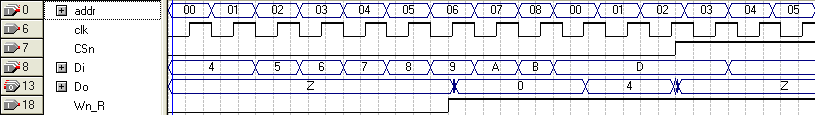

मेमोरी मॉड्यूल के उत्तेजक ऑपरेशन के परिणाम चित्रा 6 में दिखाए गए हैं। यहां इस तथ्य पर ध्यान देना आवश्यक है कि सभी मेमोरी कोशिकाओं की प्रारंभिक सामग्री शून्य है। 6-8 नंबर वाली कोशिकाओं को पढ़ने पर यह दिखाई देता है।

चित्र 6 - रैम के आरेख

किसी भी संस्करण के क्वार्ट्स II हैडबुक में अधिक जानकारी।

उदाहरण के लिए, वर्तमान एक 13 है । धारा 6 - अनुशंसित एचडीएल कोडिंग स्टाइल।