यह लेख कॉर्टेक्स-एम कोर माइक्रोकंट्रोलर प्रोग्रामिंग चक्र की निरंतरता है।

पहला लेख यहाँ पढ़ा जा सकता है:

STM32 के साथ कोर्टेक्स-एम के साथ शुरुआत करनालेखों का उद्देश्य एमके प्रोग्रामिंग करते समय आने वाली सुविधाओं का विस्तृत विवरण है। सामग्री उन लोगों के लिए अभिप्रेत नहीं है जो 10 मिनट में एक निमिष एलईडी का उदाहरण चलाना चाहते हैं। मैं विस्तार से वर्णन करने की कोशिश करूंगा कि अक्सर शुरुआती लोगों से क्या छिपा होता है ताकि उन्हें डराने के लिए नहीं।

मैं वास्तव में मानक पुस्तकालयों, टेम्पलेट्स, उदाहरणों आदि का उपयोग करके प्रोग्रामर चाहता हूं। समझें कि यह कैसे काम करता है। और इन अति पुस्तकालयों और उदाहरणों की अनुपस्थिति में, वे स्वतंत्र रूप से अपनी समस्या को हल कर सकते थे।

मुख्य जोर कोर्टेक्स-एम कोर के लिए प्रलेखन और एक विशेष नियंत्रक के लिए प्रलेखन का अध्ययन करने पर है।

इस बार हम रुकावटों के बारे में बात करेंगे, साथ ही साथ स्मृति वास्तुकला और एमके फर्मवेयर संरचना के कुछ मुद्दों को छुआ जाएगा।

एआरएम प्रलेखन के बारे में कुछ शब्द

मेरे लिए पूरी तरह से स्पष्ट नहीं होने वाले कारणों के लिए, आप

ARM वेबसाइट पर नहीं जा सकते और Cortex-M4 कोर के लिए पूर्ण प्रलेखन डाउनलोड कर सकते हैं। और कोर्टेक्स-एम 3 पर भी असंभव है।

कुछ दस्तावेज पढ़ने होंगे।

1. लर्निंग को

कोर्टेक्स ™ -एम 3 टेक्नीकल रेफरेंस मैनुअल रिवीजन के साथ शुरू करना होगा

: आर 1 पी 1 - कॉर्टेक्स-एम 3 कोर के लिए तकनीकी विनिर्देश का पहला संशोधन

2.

कॉर्टेक्स ™ -M4 टेक्नीकल रेफरेंस मैनुअल के सभी और संशोधन और विवरण केवल सामान्य डेटा और पिछले दस्तावेज़ के सापेक्ष परिवर्तन का वर्णन करते हैं।

तो कृपया किसी अन्य कर्नेल के विनिर्देशों के लिंक पर आश्चर्य न करें।

बाधा और घटनाएँ

सबसे पहले, आपको यह समझने की आवश्यकता है कि क्या व्यवधान हैं।

कोर्टेक्स-एम एमके की दो अवधारणाएं हैं जो अक्सर

इंटरप्ट और

इवेंट को भ्रमित करती हैं।

इवेंट एक इवेंट (हार्डवेयर या सॉफ्टवेयर) है जिसे कोर या पेरीफेरल यूनिट्स जवाब दे सकती हैं। प्रतिक्रिया विकल्पों में से एक रुकावट हो सकती है।

इंटरप्ट एक प्रोग्राम का रुकावट है और इंटरप्ट हैंडलर के एक विशेष सेक्शन पर नियंत्रण का स्थानांतरण है।

इवेंट और

इंटरप्ट के बीच संबंध इस प्रकार है:

प्रत्येक इंटरप्ट को ईवेंट द्वारा कहा जाता है, लेकिन प्रत्येक ईवेंट को इंटरप्ट नहीं कहा जाता है।इंटरप्ट के अलावा, इवेंट अन्य एमके सुविधाओं को सक्रिय कर सकते हैं।

NVIC

व्यवधानों का प्रबंधन और संचालन

एनवीआईसी (नेस्टेड वेक्टरड इंटरप्रेन्योर कंट्रोलर) द्वारा किया

जाता है । बाधा नियंत्रक कॉर्टेक्स-एम कोर का हिस्सा है। इस नियंत्रक के लिए दस्तावेज़ीकरण

Cortex ™ -M3 TechnicalReference मैनुअल संशोधन के साथ अध्ययन शुरू किया जाना चाहिए

: r1p1जब एक निश्चित घटना होती है, तो बाधा नियंत्रक स्वचालित रूप से मुख्य कार्यक्रम के निष्पादन को बाधित करता है और प्रसंस्करण के लिए संबंधित फ़ंक्शन को कॉल करता है। इंटरप्ट हैंडलर के फंक्शन से बाहर निकलने के बाद, प्रोग्राम उस जगह से निष्पादन जारी रखता है, जहां इंटरप्ट हुआ था। सब कुछ स्वचालित रूप से होता है (एनवीआईसी के सही कॉन्फ़िगरेशन के साथ, लेकिन उस पर अधिक)।

नाम से ही पता चलता है कि एनवीआईसी कंट्रोलर इंटरेस्ट नेस्टिंग और प्राथमिकताओं का समर्थन करता है। एनवीआईसी की स्थापना करते समय प्रत्येक बाधा को प्राथमिकता दी जाती है। यदि उच्च-प्राथमिकता वाले व्यवधान को कम-प्राथमिकता वाले व्यवधान के प्रसंस्करण के दौरान होता है, तो यह बदले में, कम-प्राथमिकता वाले बाधा हैंडलर को बाधित करेगा।

यह कैसे काम करता है?

यह पोस्ट पूर्ण होने का दावा नहीं करता है, मेरा सुझाव है कि आप

कोर्टेक्स ™ -M3 तकनीकी संदर्भ नियमावली में व्यवधान अनुभाग का अध्ययन करें। चूंकि कर्नेल का यह हिस्सा नहीं बदला है, इसका विवरण कोर्टेक्स-एम 3 कोर को r1p1 के पहले संशोधन में दिया गया है।

एक बाधा में प्रवेश करना और बाहर निकलना

जब कोई अवरोध उत्पन्न होता है, तो NVIC कर्नेल को प्रसंस्करण मोड में बाधित करता है। इंटरप्ट प्रोसेसिंग मोड में जाने के बाद, कर्नेल रजिस्टरों को स्टैक पर धकेल दिया जाता है। स्टैक के लिए रजिस्टर मानों के लेखन के दौरान, अंतःक्रियात्मक प्रसंस्करण फ़ंक्शन का प्रारंभिक पता प्राप्त होता है।

प्रोग्राम स्टेटस रजिस्टर (

प्रोग्राम स्टेटस रजिस्टर (पीएसआर) ), प्रोग्राम काउंटर (

प्रोग्राम काउंटर (पीसी) ) और संचार रजिस्टर (

लिंक रजिस्टर (एलआर) ) स्टैक पर ले जाया जाता है।

कॉर्टेक्स-एम 4 जेनेरिक यूजर गाइड में कर्नेल रजिस्टर विवरण दिए गए हैं। इसके कारण, जिस राज्य में कर्नेल को बाधित प्रसंस्करण मोड में प्रवेश करने से पहले याद किया गया था।

रजिस्टरों R0 - R3 और R12 भी सहेजे गए हैं। इन रजिस्टरों का उपयोग मापदंडों को पारित करने के निर्देशों में किया जाता है, इसलिए, उन्हें स्टैक पर रखने से उन्हें रुकावट फ़ंक्शन में उपयोग करना संभव हो जाता है, और आर 12 अक्सर कार्यक्रम के कार्य रजिस्टर के रूप में कार्य करता है।

व्यवधान प्रसंस्करण के पूरा होने पर, सभी कार्यों को रिवर्स ऑर्डर में किया जाएगा: स्टैक की सामग्री को पुनर्प्राप्त किया जाता है और, इसके साथ समानांतर में, वापसी पता का नमूना लिया जाता है।

जब तक हैंडलर के पहले निर्देश को निष्पादित नहीं किया जाता है, तब तक बीच में रुकावट शुरू हो जाती है, यह अवरोध 12 घड़ी चक्र से गुजरता है, बीच में पूरा होने के बाद मुख्य कार्यक्रम को फिर से शुरू करने के लिए उसी समय की आवश्यकता होती है।

बाधा डालने वाला

जैसा कि ऊपर उल्लेख किया गया है, एनवीआईसी विभिन्न प्राथमिकताओं के साथ व्यवधान का समर्थन करता है जो एक दूसरे को बाधित कर सकते हैं। इस मामले में, विभिन्न परिस्थितियां उत्पन्न हो सकती हैं, जिनमें से प्रसंस्करण को अलग तरीके से अनुकूलित किया जाता है।

1. कम प्राथमिकता रुकावटइस स्थिति में, कम प्राथमिकता वाले बाधा प्रसंस्करण को समाप्त कर दिया जाता है। अगले 12 चक्र, नए डेटा सेट को स्टैक पर सहेजा जाता है और उच्च-प्राथमिकता वाले व्यवधान की प्रक्रिया शुरू होती है। इसके प्रसंस्करण के बाद, स्टैक की सामग्री को स्वचालित रूप से निकाला जाता है और कम-प्राथमिकता वाले व्यवधान के प्रसंस्करण को फिर से शुरू किया जाता है।

मुख्य कार्यक्रम के व्यवधान से कोई बड़ा अंतर नहीं है।

2. निरंतर व्यवधान से निपटनेयह स्थिति दो मामलों में हो सकती है: यदि एक उच्च-प्राथमिकता के प्रसंस्करण के दौरान दो प्राथमिकताएं एक ही प्राथमिकता होती हैं और एक साथ होती हैं, तो निम्न-प्राथमिकता बाधा उत्पन्न होती है।

इस स्थिति में, स्टैक पर मध्यवर्ती कार्रवाई नहीं की जाती हैं। केवल कम-प्राथमिकता वाले बाधा हैंडलर का पता लोड किया जाता है और इसके निष्पादन के लिए संक्रमण होता है। स्टैक संचालन से बचने से 6 घड़ी चक्र बचते हैं। अगली रुकावट के लिए संक्रमण 12 चक्रों में नहीं, बल्कि केवल 6 में होता है।

3. उच्च प्राथमिकता वाले व्यवधान में देरीयदि निम्न-प्राथमिकता वाले प्रसंस्करण के लिए उच्च प्राथमिकता वाली बाधा उत्पन्न होती है (उन 12 घड़ी चक्रों के लिए)। इस स्थिति में, उच्च-प्राथमिकता वाले व्यवधान में होने वाले क्षण से कम से कम 6 चक्र होंगे (बाधा हैंडलर के पते को लोड करने और उस पर जाने के लिए आवश्यक समय)। निम्न प्राथमिकता पर वापस पहले से ही ऊपर वर्णित है।

बाधा प्रधानता

केवल व्यवधानों की प्राथमिकता निर्धारित करने के अलावा, NVIC समूह प्राथमिकताओं की क्षमता को लागू करता है।

एक उच्च प्राथमिकता वाले समूह में रुकावट एक कम प्राथमिकता वाले समूह में बाधा संचालकों को बाधित कर सकती है। एक ही समूह से व्यवधान, लेकिन समूह के भीतर विभिन्न प्राथमिकताओं के साथ, एक दूसरे को बाधित नहीं कर सकते। समूह के भीतर प्राथमिकता केवल उसी क्रम को निर्धारित करती है जिसमें हैंडलर को बुलाया जाता है जब दोनों घटनाओं को सक्रिय किया गया हो।

इंटरप्रिट प्रायोरिटी रजिस्टरों (

कोर्टेक्स-एम 4 जेनेरिक यूजर गाइड देखें ) में व्यवधान प्राथमिकता मान निर्धारित है। उसी समय, बिट्स का हिस्सा उस समूह की प्राथमिकता के लिए जिम्मेदार होता है जिसमें व्यवधान स्थित होता है, और भाग समूह के भीतर प्राथमिकता के लिए होता है।

समूह प्राथमिकता या प्राथमिकता के लिए बिट्स के वितरण को समूह के भीतर सेट करना

एप्लिकेशन इंटरप्ट और रीसेट कंट्रोल रजिस्टर (एटेंटेशन !!!

कॉर्टेक्स-एम 4 जेनेरिक यूजर गाइड देखें ) का उपयोग करके किया जाता है।

जैसा कि आपने शायद देखा है,

कॉर्टेक्स-एम 4 जेनेरिक यूजर गाइड का कहना है कि प्राथमिकताएं निर्धारित करना और प्राथमिकताएं

निर्धारित करना एक विशेष रूप से

लागू कार्यान्वयन पर निर्भर करता है।

लेकिन आगे यह बहुत सुखद बात नहीं है। STM32F407 MK के

संदर्भ मैनुअल में , NVIC के बारे में लगभग कोई जानकारी नहीं है। लेकिन एक अलग दस्तावेज़ के लिए एक लिंक है। STM32 में NVIC के कार्यान्वयन से निपटने के लिए, आपको एक और दस्तावेज़ -

STM32F3xxx और STM32F4xxx Cortex-M4 प्रोग्रामिंग मैनुअल पढ़ना होगा। सामान्यतया, मैं आपको अन्य सभी मुद्दों पर इस दस्तावेज़ का सावधानीपूर्वक अध्ययन करने की सलाह देता हूँ, कर्नेल कार्य को एआरएम के प्रलेखन की तुलना में इसमें अधिक विस्तार से वर्णित किया गया है।

इसमें, आप पहले से ही पा सकते हैं:

प्रत्येक रुकावट के लिए 0-15 का एक प्रोग्राम योग्य प्राथमिकता स्तर। एक उच्च स्तर एक से मेल खाता है

निम्न प्राथमिकता, इसलिए स्तर 0 उच्चतम रुकावट प्राथमिकता है

प्राथमिकता के संभावित 8 बिट्स में से केवल 4 का उपयोग किया जाता है। लेकिन अधिकांश कार्यों के लिए यह काफी पर्याप्त है।

मास्किंग में रुकावट आती है

मान लें कि लाल बटन दबाकर लॉन्च वाहन को लॉन्च करने का काम हमारे पास है, लेकिन केवल अगर कुंजी चालू हो।

यह कुंजी को चालू करने के लिए एक बाधा उत्पन्न करने के लिए बिल्कुल कोई मतलब नहीं है। लेकिन लाल खुदाई को दबाने से रुकावट हमें चाहिए। विभिन्न रुकावट वाले वैक्टरों को सक्षम / अक्षम करने के लिए, इंटरप्ट का मास्किंग है।

इंटरप्ट मास्किंग को

इंटरप्ट सेट-सक्षम रजिस्टर का उपयोग करके किया जाता है।

यदि बाधा नकाबपोश है, तो इसका मतलब यह नहीं है कि परिधीय घटनाओं को पैदा नहीं कर रहे हैं! यह सिर्फ इतना है कि एनवीआईसी इस घटना के लिए किसी हैंडलर को नहीं बुलाता है।

बाधित वेक्टर तालिका

एनवीआईसी द्वारा समर्थित सभी संभावित रुकावटों को बाधित वेक्टर टेबल पर लिखा जाता है। संक्षेप में, रुकावट वेक्टर तालिका रुकावट संचालकों के फ़ंक्शन पतों की सूची से अधिक कुछ नहीं है। सूची में संख्या बाधा संख्या से मेल खाती है।

जैसा कि

कॉर्टेक्स-एम 4 जेनेरिक यूजर गाइड में लिखा गया है, एनवीआईसी 240 विभिन्न इंटरप्ट वैक्टर का समर्थन करता है। लेकिन कार्यान्वयन पहले से ही विशिष्ट निर्माता पर निर्भर करता है।

कर्नेल विवरण में, केवल कर्नेल अपवाद व्यवधान को मानकीकृत किया गया है (देखें खंड

2.3.2 कोर्टेक्स-एम 4 जेनेरिक उपयोगकर्ता गाइड में

अपवाद प्रकार ):

- रीसेट

- एनएमआई

- HardFault

- MemManage

- BusFault

- UsageFault

- SVCall

- PendSV

- SysTick

मेरा सुझाव है कि आप इन अपवादों के विवरण से खुद को परिचित करें। इनमें से कुछ को भविष्य के लेखों में संबोधित किया जाएगा।

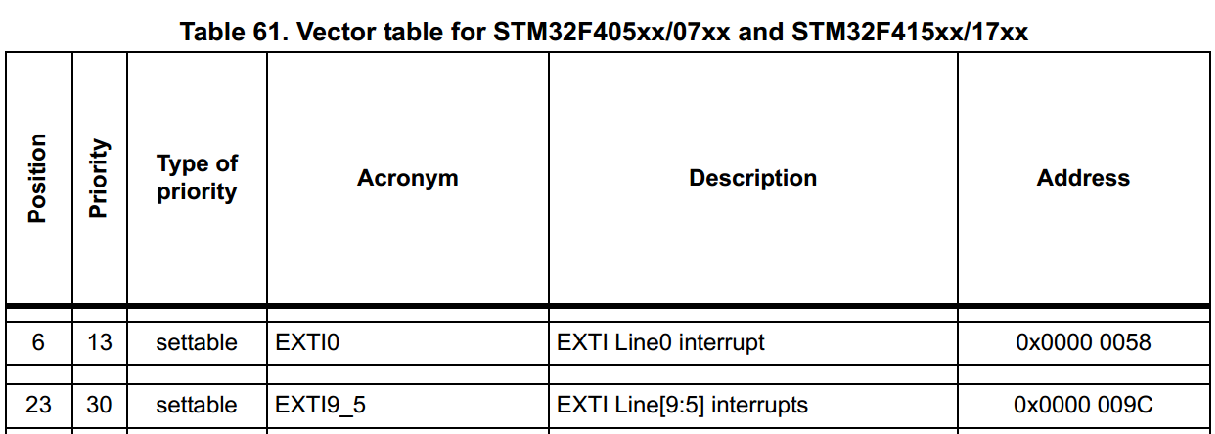

शेष रुकावटें एमके के लिए अद्वितीय हैं। आप संबंधित

संदर्भ पुस्तिका में अपने MK की वेक्टर तालिका का विवरण पा सकते हैं (STM32F405xx / 07xx और STM32F415xx / 17xx के लिए वेक्टर तालिका देखें)। STM32F4xx नियंत्रक 81 इंटरप्ट वैक्टर का समर्थन करते हैं। आप देख सकते हैं कि इस तालिका में सभी परिधीय ब्लॉक सूचीबद्ध हैं (और कुछ से अधिक बार)।

लगभग सभी परिधीय इकाइयाँ व्यवधान उत्पन्न करती हैं ताकि कर्नेल को किसी महत्वपूर्ण घटना के घटित होने पर (उदाहरण के लिए, UART के माध्यम से डेटा प्राप्त करना) उसके साथ काम करने के लिए विचलित हो।

बाधित वैक्टर और लोडिंग एमके की व्यवस्था

कोर्टेक्स-एम में रुकावट ऑपरेशन के सिद्धांतों को समझने के बाद, यह केवल यह समझने के लिए बना हुआ है कि रुकावट तालिका कहाँ संग्रहीत है।

इसके लिए, यह बूट प्रक्रिया और नियंत्रक फर्मवेयर संरचना पर विचार करने के लायक है। इस बार हम केवल अंतर्निहित फ्लैश मेमोरी से लोड करने पर विचार करेंगे।

पता स्थान की शुरुआत में वेक्टर टेबल में, फ्लैश मेमोरी कम से कम होनी चाहिए (

कॉर्टेक्स-एम 3 तकनीकी संदर्भ मैनुअल देखें :

• स्टैक शीर्ष पता

• नियमित स्थान रीसेट करें

• NMI ISR स्थान

• हार्ड फॉल्ट ISR स्थान।

फ्लैश मेमोरी की शुरुआत से, कर्नेल एसपी (स्टैक टॉप ऐड्रेस) और पीसी (रीसेट रूटीन लोकेशन) का मूल्य पढ़ता है। इस प्रकार, फ़ंक्शन स्वचालित रूप से शुरू होता है, पीसी रजिस्टर में पढ़े गए पते के साथ। यह हो सकता है, उदाहरण के लिए, मुख्य।

आवश्यक चार घटकों के बाद, बाधित वैक्टर की एक और तालिका हो सकती है। मुख्य बात आदेश रखना है।

यदि आप चाहें, तो आप एक अन्य मेमोरी क्षेत्र में इंटरप्ट वैक्टर की तालिका रख सकते हैं, लेकिन फिर, आपको एनवीआईसी को बताना होगा कि हमने टेबल को कहां स्थानांतरित किया है।

वेक्टर टेबल ऑफ़सेट रजिस्टर वेक्टर टेबल के इस विस्थापन के लिए ज़िम्मेदार है (

Cortex-M4 तकनीकी संदर्भ मैनुअल देखें । यह नए सॉफ़्टवेयर (बूटलोडर) के लिए अंतर्निहित बूटलोडर लिखने के लिए आवश्यक हो सकता है, लेकिन इसके बारे में कुछ अन्य समय के लिए।

सिद्धांत से अभ्यास तक

दूसरी परियोजना के टीओआर

एक उदाहरण

STM32F4Discovery डिबग बोर्ड के लिए बनाया गया है।

जब बटन दबाया जाता है, तो LED3 को प्रकाश करना चाहिए। जब PC6 और GND संपर्क बंद हो जाते हैं, LED5 लाइट्स बंद हो जाती हैं।

प्रोग्रामिंग प्रक्रिया में, हम रुकावट की प्राथमिकताओं के साथ खेलते हैं और देखते हैं कि इससे क्या होगा।

लोहे का हिस्सा

बोर्ड के लिए प्रलेखन में बटन और एलईडी खोजें:

जब बटन दबाया नहीं जाता है, तो पिन PA0 एक तार्किक शून्य होगा, जब आप बटन दबाते हैं, तो बटन तार्किक 1 (3.3V) प्रदर्शित करेगा।

LED3 PD13 पिन से जुड़ा है।

LED5 PD14 पिन से जुड़ा है।

PC6 पिन के साथ सबसे दिलचस्प बात यह है कि यह सीधे पिन कनेक्टर से जुड़ा होता है। हमें यह सुनिश्चित करने की आवश्यकता होगी कि तार्किक 1 तब लॉग किया जाता है जब वह जीएनडी पिन के लिए छोटा नहीं होता है। यह कैसे करें नीचे चर्चा की जाएगी।

GPIO सेटअप

हमारे कार्य के लिए, एक सप्ताहांत के रूप में पिन पीडी 13 और पीडी 14 को कॉन्फ़िगर करना आवश्यक है। आप

पिछले लेख में ऐसा करने के बारे में पढ़ सकते हैं।

PA0 पिन सेट करना भी काफी सरल है - आपको इसे इनपुट के लिए कॉन्फ़िगर करना होगा। इस तथ्य के बावजूद कि एमके की गिनती के बाद लगभग सभी पिन इनपुट के लिए कॉन्फ़िगर किए गए हैं, यह प्रारंभिक रूप से इस प्रारंभ को पंजीकृत करने के लिए अत्यधिक उचित है।

PC7 पिन के साथ, सब कुछ कुछ और दिलचस्प है। चूंकि वह "हवा में लटका हुआ है", उसकी स्थिति परिभाषित नहीं है। हमें यह सुनिश्चित करने की आवश्यकता है कि उसकी स्थिति हमेशा "1" हो। ऐसा करने के लिए, GPIO ब्लॉक में पुल-अप को सक्रिय करें। हमारे मामले में, आपको सत्ता में एक पुल-अप की आवश्यकता है - पूर्ण उत्तर प्रदेश।

GPIO पोर्ट पुल-अप / पुल-डाउन रजिस्टर का उपयोग करके ट्रिमिंग को सक्रिय किया

जाता है ।

EXTI में बाधा

इंटरप्ट का उपयोग करते हुए हमारे "टीके" को करने के लिए, हमें उन अवरोधों को कॉन्फ़िगर करने की आवश्यकता होती है जो तब ट्रिगर हो जाएंगे जब संपर्क PA0 राज्य "0" से राज्य "1" में बदल जाता है, और तब होता है जब पीसी 6 से संपर्क राज्य "1" से राज्य "0" में बदल जाता है।

STM32F4xx MK में, इस उद्देश्य के लिए एक

EXTI (बाहरी व्यवधान / घटना नियंत्रक) नियंत्रक का उपयोग किया जाता है। मैं अत्यधिक अनुशंसा करता हूं कि आप

संदर्भ मैनुअल में इसकी कार्यक्षमता से खुद को परिचित करें। हमें वर्णित के रूप में करने की आवश्यकता है:

हार्डवेयर व्यवधान चयन

23 लाइनों को बीच के स्रोत के रूप में कॉन्फ़िगर करने के लिए, निम्नलिखित प्रक्रिया का उपयोग करें:

• 23 इंटरप्ट लाइन्स (EXTI_IMR) के मास्क बिट्स को कॉन्फ़िगर करें

• बाधा लाइनों के ट्रिगर चयन बिट्स को कॉन्फ़िगर करें (EXTI_RTSR और EXTI_FTSR)

• बाहरी अवरोध नियंत्रक (EXTI) के लिए मैप किए गए NVIC IRQ चैनल को नियंत्रित करने वाले सक्षम और मुखौटा बिट्स को कॉन्फ़िगर करें ताकि 23 लाइनों में से एक से आने वाली एक बाधा को सही ढंग से स्वीकार किया जा सके।

हमें 0 और 6 EXTI लाइनों की आवश्यकता होगी। संबंधित इंटरप्ट लाइन्स को मास्क करने के लिए, EXTI_IMR रजिस्टर पर 0x9 लिखें।

पंक्ति PA0 के लिए, "0" से राज्य में "1" - एक बढ़ते हुए किनारे पर संक्रमण पर एक बाधा घटना उत्पन्न करना आवश्यक है। यही है, EXTI_RTSR रजिस्टर के शून्य बिट पर 1 लिखना आवश्यक है।

PC6 लाइन के लिए, इसके विपरीत, राज्य "1" से राज्य में "0" - गिरने वाले किनारे पर संक्रमण पर एक बाधा घटना उत्पन्न करना आवश्यक है। यही है, EXTI_FTSR रजिस्टर के छठे बिट में 1 लिखना आवश्यक है।

यह EXTI ब्लॉक के कॉन्फ़िगरेशन को पूरा करता है। अंतिम आइटम एनवीआईसी टिंचर के साथ लागू किया जाएगा।

इसके अलावा, यह निर्धारित करना आवश्यक है कि किस पोर्ट से कौन सा पोर्ट एक विशिष्ट EXTI लाइन से जुड़ा है। यह

SYSCFG रजिस्ट्रार

एक्सटर्नल इंटरफिगरेशन रजिस्टर (

संदर्भ मैनुअल ) का उपयोग करके किया जाता है। ये रजिस्टर

सिस्टम कॉन्फ़िगरेशन कंट्रोलर में स्थित हैं, जो मुझे बहुत तार्किक नहीं लगता (ईएक्सटीआई में इस सेटिंग को शामिल क्यों नहीं किया गया?), लेकिन अब इस तथ्य को एसटी के विवेक पर छोड़ दें।

एनवीआईसी सेटअप

इंटरप्ट सेट-सक्षम रजिस्टर (NVIC_ISERx) रजिस्टरों का उपयोग करके एक निश्चित इंटरप्ट वेक्टर का प्रसंस्करण सक्रिय होता है।

कॉर्टेक्स-एम 4 जेनेरिक यूजर गाइड में रजिस्टर विवरण दिए गए हैं। हमारे एमके के लिए बाधा वैक्टर की तालिका

संदर्भ पुस्तिका में दी गई है (तालिका 61 देखें)।

तालिका से आप देख सकते हैं कि लाइन 0 के लिए एक अलग अवरोध है, लेकिन 9 के माध्यम से 5 लाइनें सभी के लिए एक बाधा उत्पन्न करती हैं।

इसके अलावा, तालिका से हमने उन वैक्टरों की संख्या सीखी जिन्हें हमें हस्तक्षेप की आवश्यकता है। अब आपको 6 बिट्स (लाइन इंटरप्ट 0 EXTI की सक्रियता) रजिस्टर NVIC_ISER0 (पता 0xE000E100) और 23 बिट्स एक ही रजिस्टर (लाइन इंटरप्ट 5-9 की सक्रियता) में "1" लिखना होगा।

प्राथमिकता सेटिंग

रुकावट प्राथमिकताओं में लिप्त होने के लिए, हम प्राथमिकता समूहों को कॉन्फ़िगर करेंगे ताकि 2 बिट्स समूह के भीतर प्राथमिकता के लिए जिम्मेदार हों, और 2 बिट्स समूह की प्राथमिकता के लिए हैं। ऐसा करने के लिए, मान को 0x05FA0500 पर

एप्लिकेशन इंटरप्ट और रीसेट कंट्रोल रजिस्टर (

STM32F3xxx और STM32F4xxx Cortex-M4 प्रोग्रामिंग मैनुअल )

लिखें ।

प्रायोरिटी सेटिंग

इंटरप्रिट प्रायोरिटी रजिस्टर्स (

STM32F3xxx और STM32F4xxx Cortex-M4 प्रोग्रामिंग मैनुअल ) रजिस्टरों का उपयोग करके की जाती है। हम इंटरेस्ट प्रायोरिटी रजिस्टर 2 (0xE000E4008) और इंटरप्रिट प्रायोरिटी रजिस्टर 5 (0xE000E401C) रजिस्टर में रुचि रखेंगे।

हम अभी प्राथमिकताएं नहीं बदलेंगे। दोनों को बीच में आने के लिए समान होने दें।

बाधा से निपटने

कार्य में बाधा हैंडलर सी भाषा के कार्यों से अधिक कुछ नहीं हैं, जो न तो प्राप्त करते हैं और न ही कुछ लौटाते हैं (और सही तरीके से, किसी से भी नहीं और किससे नहीं)।

मुख्य नियम यह है कि बाधा से निपटने को जितनी जल्दी हो सके किया जाना चाहिए !!! अन्यथा, कम प्राथमिकता वाले व्यवधान बहुत लंबा इंतजार कर सकते हैं।

व्यवधान प्रसंस्करण की समाप्ति के बाद, उस घटना की गतिविधि को रीसेट करना आवश्यक है जो रुकावट का कारण बना - "रुकावट को साफ़ करें"। EXTI_PR रजिस्टर का उपयोग करके EXTI का रुकावट साफ हो गया है। नोट: रिकॉर्ड "1" रुकावट को साफ करता है, रिकॉर्ड "0" का कोई प्रभाव नहीं पड़ता है।

यदि लाइन इंटरप्ट 0 EXTI के प्रसंस्करण के साथ सब कुछ काफी सरल है, तो 5-9 लाइनों के समूह के साथ सवाल उठता है - यह कैसे निर्धारित किया जाए कि किस लाइन ने रुकावट का कारण बना। आप पेंडिंग रजिस्टर (EXTI_PR) -

संदर्भ पुस्तिका के रजिस्टर बिट की जाँच करके पता कर सकते हैं।

वैक्टर की एक तालिका बनाएं और इसे सही जगह पर रखें

एमके फ्लैश मेमोरी की शुरुआत में बाधित हैंडलर फ़ंक्शंस के सही पते के साथ वेक्टर तालिका के लिए प्रोजेक्ट में स्टार्टअपसी फ़ाइल बनाएं और कनेक्ट करें।

के उपयोग

@ ".intvec"

लिंकर फ़ाइल में घोषित अनुभाग की शुरुआत में __vector_table की स्थिति। फ़ाइल को यहाँ देखा जा सकता है:

रॉम मेमोरी की शुरुआत में ही सेक्शन सेट होता है। यहां पते पाए जा सकते

हैं (एक दस्तावेज जो STM32 फ्लैश मेमोरी के पते का वर्णन करता है):

IAR के निर्देश और IAR के विशेष कार्य का संयोजन:

#pragma segment="CSTACK" __sfe( "CSTACK" )

फ्लैश की शुरुआत में स्टैक के शीर्ष पर एक सूचक लिखता है।

तालिका स्वयं उन कार्यों के पते से भरी हुई है जो एक शाश्वत चक्र को लागू करते हैं। हमारे लिए केवल ब्याज के कार्यों के लिए एक अपवाद बनाया गया है:

extern void EXTI_Line0_IntHandler(void); extern void EXTI_Line6_IntHandler(void);

स्टार्टअप में कहा जाने वाला फंक्शन बस जंप करता है

extern void __iar_program_start(void);

यह फ़ंक्शन मुख्य है ()। यदि इच्छा उठती है तो प्रतीक को फिर से परिभाषित किया जा सकता है:

मुख्य फ़ाइल पर जाएं

सबसे पहले, उन सभी पतों और बिट फ़ील्ड्स को लिखें और पुनः परिभाषित करें जिनकी हमें आवश्यकता है।

कृपया ध्यान दें कि एमके के विशेष रजिस्टरों के मूल्यों को

अस्थिर घोषित किया गया है। यह आवश्यक है ताकि कंपाइलर उन तक पहुंचने के संचालन को अनुकूलित करने का प्रयास न करे, क्योंकि ये सिर्फ स्मृति के खंड नहीं हैं और कर्नेल की भागीदारी के बिना उनके मान बदल सकते हैं।

प्राथमिकता समूह बनाना

सबसे पहले, यह रुकावट प्राथमिकताओं के समूह को स्थापित करने के लायक है:

SCB_AIRCR = SCB_AIRCR_GROUP22;

.यह कार्रवाई केवल एक बार की जानी चाहिए। तीसरे पक्ष के पुस्तकालयों का उपयोग करते हुए जटिल परियोजनाओं में, यह इस तथ्य की जांच करने के लायक है। प्राथमिकता समूहन को बदलने से फर्मवेयर का गलत संचालन हो सकता है।

प्रयुक्त परिधीय की क्लॉकिंग सक्षम करना

आपको याद दिला दूं कि इससे पहले कि आप परिधीय इकाइयों के साथ काम करना शुरू करें, आपको उनका समय सक्षम करने की आवश्यकता है:

आप SYSCFG के साथ तुरंत काम नहीं कर सकते, आपको कुछ उपायों की प्रतीक्षा करने की आवश्यकता है। लेकिन हम नहीं करेंगे। चलिए GPIO को आरंभ करने के साथ आरंभ करते हैं।

GPIO प्रारंभिक

पिछली बार की तरह ही एल ई डी को इनिशियलाइज़ किया जाता है:

PA0 बटन और PC7 पिन को इनपुट के रूप में आरंभीकृत किया गया है:

बस पीसी 6 से संपर्क करने के लिए आपको पावर पुल चालू करना होगा। GPIOC_PUPDR रजिस्टर का उपयोग करके सक्रियण निलंबित किया जाता है:

EXTI सेटअप

और इसलिए, आपको निम्नलिखित मापदंडों को कॉन्फ़िगर करने की आवश्यकता है - पंक्ति 0 और 6 के लिए इंटरप्ट को सक्षम करें, एक बढ़ते किनारे पर लाइन 0 इंटरप्ट के लिए, लाइन 6 के लिए - गिरने वाले किनारे पर रुकावट

यह उन पोर्ट को कॉन्फ़िगर करने के लिए रहता है, जो पोर्ट EXTI लाइन से जुड़े हैं (एक अजीब समाधान, उदाहरण के लिए, स्टेलारिस एमके पिन के किसी भी संयोजन के लिए एक बाधा उत्पन्न कर सकते हैं, STM32 के लिए यह अधिक कठिन है):

एनवीआईसी सेटअप

यह बाधित प्राथमिकताओं को कॉन्फ़िगर करने और प्रसंस्करण शुरू करने के लिए उन्हें मुखौटा बना रहता है। ध्यान दें कि

एनवीआईसी_आईपीआर रजिस्टर बाइट एक्सेस के लिए उपलब्ध

हैं , जो केवल व्यक्तिगत इंटरप्ट वैक्टर के आवश्यक प्राथमिकता बाइट्स तक पहुंच को सरल करता है। यह रुकावट वेक्टर संख्या (परिभाषाओं की सूची देखें) के मूल्य से सिर्फ बदलाव के लिए पर्याप्त है। आपको एक बार फिर याद दिला दें कि EXTI लाइन 0 की वेक्टर टेबल में नंबर 6 है, और EXTI लाइन 5_9 की संख्या 23 है। STM32 के लिए, प्राथमिकता के केवल सबसे महत्वपूर्ण 4 बिट्स का मूल्य है:

प्रदर्शित करने के लिए, प्राथमिकताएं अलग-अलग निर्धारित की जाती हैं।

अब आप इंटरप्ट को सक्षम कर सकते हैं:

अब से, बटन दबाने और PC6 और GND को छोटा करने के लिए क्रमशः हैंडलर फ़ंक्शन EXTI_Line0_IntHandler और EXTI_Line6_IntHandler कहा जाएगा।

बाधा से निपटने

इंटरप्ट हैंडलिंग फ़ंक्शंस में, पहले रुकावट को साफ़ करना आवश्यक है, जिसके बाद आप एलईडी को प्रकाश में ला सकते हैं। व्यवधान प्राथमिकताओं को प्रदर्शित करने के लिए, हैंडलर में से एक में एक शाश्वत लूप जोड़ा गया है। यदि एक अनन्त लूप के साथ एक बाधा की प्राथमिकता दूसरी की प्राथमिकता से कम है, तो इसे नहीं कहा जा सकता है। अन्यथा, यह पहले बाधित करने में सक्षम होगा। मेरा सुझाव है कि आप अपने आप ही अवरोध प्राथमिकताओं के विभिन्न मूल्यों की कोशिश करें और नेत्रहीन देखें कि इससे क्या होता है (

ध्यान - बाधा समूहों के बारे में मत भूलना! )।

void EXTI_Line0_IntHandler(void) {

एक निष्कर्ष के बजाय

बस, मैं परिणामी कार्यक्रम की पूरी सूची दूंगा।

बीच की प्राथमिकताओं और व्यवधान की प्राथमिकताओं के प्रभाव की जांच करने के लिए, प्राथमिकताओं को बदलने की कोशिश करें और देखें कि क्या होता है (दो बिट्स - समूह के भीतर प्राथमिकता, 2 बिट्स - समूह की प्राथमिकता)।