यह आलेख भाषा के संश्लेषित सबसेट के लिए वेरिलॉग -2001 की तुलना में डेटा संगठन के क्षेत्र में SystemVerilog के कुछ नवाचारों को दर्शाता है।

SystemVerilog का इतिहास लंबाई और धूमिल है। वेरिलोग -95 मानक को अपनाने के साथ शुरू हुआ, इसका समापन वेरिलोग-2001 में हुआ। हालांकि, भाषा सत्यापन के लिए बहुत उपयुक्त नहीं थी, "ई" परिवार की भाषाओं का उपयोग करने वाले इंजीनियर - वीईआरए, टेस्टब्यूडर। अपने आधुनिक रूप में, SystemVerilog 2005 के बाद दिखाई दिया। अब संश्लेषण उपकरण और मॉडलिंग जैसे कि क्वार्टस II, ISE, ModelSim / QuestaSim आत्मविश्वास से SystemVililog का समर्थन करते हैं। मानक को IEEE 1800-2012 कहा जाता है।

लगभग। यह लेख लंबे समय से लिखा गया है लेकिन प्रकाशित नहीं हुआ है। मुझे उम्मीद है कि यह शुरुआती लोगों के लिए उपयोगी होगा।SystemVerilog वेरिलॉग दुनिया के लिए कई नए दिलचस्प डिजाइन लेकर आया है:

- सी-लिल सिंटैक्स

- PLO

- संरचनाएं, कतारें, गतिशील सरणियाँ, गणना

- टाइप कास्ट करें

- फ़ॉर्च, वापसी, ब्रेक, जारी, आदि के साथ कार्यक्रम व्यवहार को नियंत्रित करना।

- सेमाफोर, मेलबॉक्स।

- इंटरफेस

- इस प्रकार के दावे

यूनिवर्सल प्रकार का तर्क।

अब रेग और तार के बीच चयन करने की आवश्यकता नहीं है, हर जगह तर्क का उपयोग किया जाता है। सिंथेसाइज़र तय करेगा कि क्या किया जाना चाहिए (VHDL से उच्च संकेत)।

इनिशियलाइज़ेशन टाइप करें

SystemVerilog बेहतर प्रकार की आरंभिक क्षमताएं प्रदान करता है। अब लिखने की जरूरत नहीं

reg [63:0] data = 64'hFFFFFFFFFFFFFFFF;

आप यह कर सकते हैं:

reg [63:0] data = '1;

डेटा लिखना = '0 जीरो के साथ वेक्टर को इनिशियलाइज़ करें, और डेटा =' bz थर्ड स्टेट के साथ

प्रगणित प्रकार।

अंत में, राज्य मशीन को इस तरह वर्णित किया जा सकता है

enum {WAITE, LOAD, STORE} State, NextState; always_ff @(posedge clock, negedge resetN) if (!resetN) State <= WAITE; else State <= NextState; always_comb begin case (State) WAITE: NextState = LOAD; LOAD: NextState = STORE; STORE: NextState = WAITE; endcase end

इसके अलावा, आप एक एन्यूमरेटेड प्रकार के लिए मान प्रदान कर सकते हैं:

enum {ONE = 1,FIVE = 5,TEN = 10 } state;

डिफ़ॉल्ट रूप से, एक एन्यूमरेटेड प्रकार को एक अंतर मान दिया जाता है। हालाँकि, आप इस तरह लिख सकते हैं

// 1 बिट की चौड़ाई के साथ प्रगणित प्रकार।

// केवल दो राज्यों को स्वीकार कर सकता है

enum bit {TRUE, FALSE} Boolean; // 2 . // enum logic [1:0] {WAITE, LOAD, READY} state;

निम्नलिखित निर्माण का उपयोग एन्यूमरेटेड प्रकार के नाम के मूल्य को प्रिंट करने के लिए किया जाता है:

$display("\nCurrent state is %s (%b)", State.name);

Strukruty

निम्नलिखित तरीके से संरचनाओं की घोषणा करें:

struct { int a, b; // 32-bit variables opcode_t opcode; // user-defined type logic [23:0] address; // 24-bit variable bit error; // 1-bit 2-state var. } Instruction_Word;

संरचनाओं के लिए टंकण की घोषणा का समर्थन किया

typedef struct { // structure definition logic [31:0] a, b; logic [ 7:0] opcode; logic [23:0] address; } instruction_word_t; instruction_word_t IW; // structure allocation

डिफ़ॉल्ट रूप से, संरचना अनपैक्ड के रूप में प्रकट होती है। पैक्ड कीवर्ड संरचना को पैक करने की अनुमति देता है।

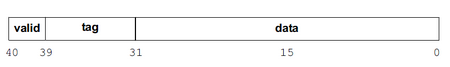

struct packed { logic valid; logic [ 7:0] tag; logic [31:0] data; } data_word;

इस रूप में, इसे एक वेक्टर के रूप में दर्शाया गया है। इसलिए, ऐसे निर्माण संभव हैं।

data_word.tag = 8'hf0; data_word[39:32] = 8'hf0; //

संघ संघ

एक संघ एक मेमोरी मूल्य है जो विभिन्न प्रकार के डेटा को संग्रहीत कर सकता है, लेकिन एक समय में केवल एक।

वाक्य विन्यास पूरी तरह से सी-लाइक है।

union { int i; int unsigned u; } data; ... data.i = -5; $display("data is %d", data.i); data.u = -5; $display("now data is %d", data.u);

सबसे बड़ी व्यावहारिक रुचि यूनियनों से भरी हुई है। वे विभिन्न प्रकारों का प्रतिनिधित्व करने के लिए निश्चित संख्या में बिट्स का उपयोग करते हैं।

एक प्रकार के माध्यम से दर्ज की गई जानकारी को दूसरे रूप (दूसरे प्रकार) में पढ़ा जा सकता है। उदाहरण के लिए:

typedef struct packed { logic [15:0] source_address; logic [15:0] destination_address; logic [23:0] data; logic [ 7:0] opcode; } data_packet_t; union packed { data_packet_t packet; // packed structure logic [7:0][7:0] bytes; // packed array } dreg;

चूंकि संघ पैक किया गया है, जानकारी संरेखित है, इसलिए तर्क के माध्यम से दर्ज किए गए डेटा [7: 0] को data_etett.t के माध्यम से पढ़ा जा सकता है

initial begin logic [15:0] src, dst; for (i = 0; i <= N; i = i + 1) begin dreg.bytes[i] <= byte_in; //store as bytes end src = dreg.source_address; dst = dreg.destination_address; end

पैक की गई सरणी

SystemVerilog आपको बहुआयामी पैक्ड सरणियाँ बनाने की अनुमति देता है

logic [3:0][7:0] data; // 2-D packed array logic [1:0][3:0][7:0] data; // 3-D packed array

IEEE मानक परिभाषित करता है कि इन तत्वों को मेमोरी में कैसे संग्रहीत किया जाना चाहिए। उदाहरण के लिए, वर्णन करने के लिए

logic [3:0][7:0] data; // 2-D packed array

चूंकि सरणी को वेक्टर के रूप में मेमोरी में संग्रहीत किया जाता है, इसलिए वैक्टर पर सभी समान संचालन का उपयोग करने की अनुमति है

logic [3:0][15:0] a, b, result; // packed arrays result = (a << 1) + b;

वेक्टर तक पहुंच या तो तत्व-वार हो सकती है, या संपूर्ण आयाम (ओं) सहित हो सकती है। तथाकथित टुकड़ा सरणी।

logic [1:0][1:0][7:0] a; // 3-D packed array a[1][1][0] = 1'b0; // a = 32'hF1A3C5E7; // a[1][0][3:0] = 4'hF; // a[0] = 16'hFACE; //

एक सरणी की सामग्री को दूसरे में कॉपी करने के लिए आप डायरेक्ट एक्सेस या स्लाइस का उपयोग कर सकते हैं

bit [1:0][15:0] a; //32 , bit 0 1 logic [3:0][7:0] b; //32 , logic O,1,Z,X logic [15:0] c; // 16 logic [39:0] d; // 40 b = a; // 32 32 c = a; // 16 d = a; // 8

संदर्भ

1.

www.asic-world.com/systemverilog2. स्टुअर्ट सदरलैंड द्वारा "SystemVerilog For Design Second Edition"