最近、モスクワ工科大学のコンピュータースタンドが大幅に更新されました。インテルは、「

砂からプロセッサーまで 」と呼ばれるスタンドを設置しました。 これからは、このスタンドは修学旅行の不可欠な部分になりますが、大人でさえも5年以上施設を訪れることを延期しないことをお勧めします。

このイベントに合わせて、同名の3部構成の講義サイクルが行われました。 すでに2つの講義が終了しています。その内容はすぐにわかります。 さて、もしあなたがこれらすべてに興味があるなら、あなたはまだ第三回の講義に参加する時間があります。それについての情報は投稿の最後にあります。

このテキストのほとんどが、ロシアのインテルの研究開発分野の外部プロジェクトのディレクターである

ニコライ・スーチンが開催した最初の講義の概要であることを認めることを恥じません。 ほとんどの場合、それは現代の半導体技術とそれらが直面する問題についてでした。

おもしろい読みを始めることを提案します。そして、非常に基本的なことから始めます。

CPU

技術的には、最新のマイクロプロセッサは、数十億個の要素で構成される1つの超大規模集積回路の形で作られています。これは、人間が作成した最も複雑な構造の1つです。 マイクロプロセッサの重要な要素は、ディスクリートスイッチ-トランジスタです。 電流を遮断および通過させる(オン/オフ)ことにより、コンピューターロジック回路を2つの状態、つまりバイナリシステムで動作させることができます。 トランジスタのサイズはナノメートルで測定されます。 1ナノメートル(nm)は、メートルの10億分の1(10–9)部分です。

| 45 nmの製造技術を使用して作成された2000個を超えるトランジスタゲートを、1本の人間の毛髪の一部に配置できます。 ナノテクノロジーについてさらに詳しく説明すると、2008年には、発行された半導体チップの2,270億ドル以上が「ナノ」市場のほぼ全体を占め、磁気ディスク、オプトエレクトロニクスなどは まだ15%以下です。 |

プロセッサを作成する際の作業の主な部分は、人間ではなくロボットメカニズムによって行われます。シリコンウェーハを前後にドラッグするのは彼らです。 各プレートの生産サイクルは、2〜3か月に達することがあります。

プロセッサの生産技術の詳細(および明確)については、さらに詳しく説明しますが、今のところは簡単に説明します。

プレートは本当に砂でできています-地球の地殻の有病率の観点から、シリコンは酸素に次いで2位になります。 化学反応により、酸化ケイ素(SiO

2 )は完全に洗浄され、きれいになってから汚れます。 マイクロエレクトロニクスの場合、単結晶シリコンが必要です-それは溶融物から得られます。 それはすべて小さな結晶から始まり(これは融液の中に下げられます)、後に人から成長する特別な単結晶「雄牛」に変わります。 次に、主な欠陥を取り除き、特殊な電球(ダイヤモンドパウダーを含む)をディスクにカットします。各ディスクは、完全に滑らかで滑らかな(原子レベルで)表面に注意深く加工されます。 各プレートの厚さは約1 mmです-単に壊れたり曲がったりしないようにするため、つまり快適に作業できるようにするためです。

各プレートの直径は正確に300 mmです。数百または数千のプロセッサーがこの領域で「成長」します。 ちなみに、Intel、Samsung、東芝、TSMCは、450mmプレートで動作可能な機器を開発していることを既に発表しています(より多くのプロセッサがより広い領域に収まるため、それぞれの価格が低くなります)-それらへの移行はすでに計画されています2012年。

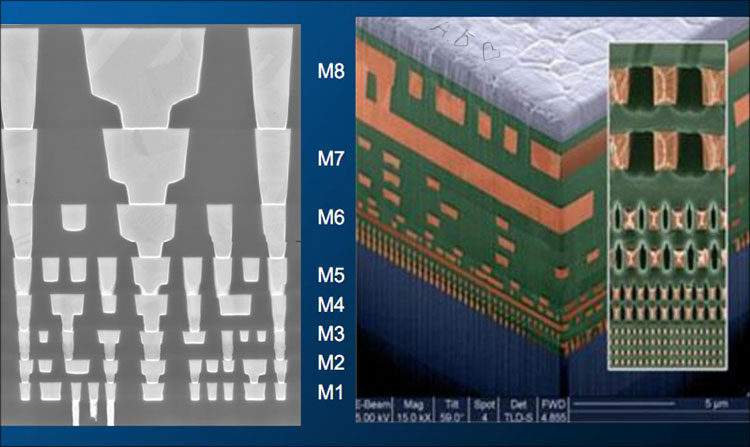

プロセッサの断面画像は次のとおりです。

上部に保護用の金属カバーがあり、保護機能に加えて、熱分配器としても機能します-クーラーを取り付けるときに熱伝導グリースをたっぷり塗ります。 熱分配器の下には、すべてのユーザータスクを実行するシリコンがあります。 さらに低いのは、プロセッサをマザーボードのソケットに取り付けることができるように、配線接点(および「脚」の面積を増やす)に必要な特別な基板です。

チップ自体はシリコンで構成され、その上には最大9層のメタライゼーション(銅製)があります-特定の法律に従って、シリコン表面にあるトランジスタを接続することができるのと同じくらい多くのレベルが必要です(これを同じレベルで行うことは単に不可能です)。 実際、これらの層は接続ワイヤとして機能しますが、スケールははるかに小さいです。 「ワイヤ」が互いに短絡しないように、それらは酸化物の層(低誘電率)によって分離されています。

上で書いたように、プロセッサの単位セルは電界効果トランジスタです。 最初の半導体製品はドイツ製で、最初のトランジスタはドイツ製でした。 しかし、電界効果トランジスタが作られ始めるとすぐに(ゲートの下に特別な絶縁層があります-トランジスタの「オン」と「オフ」を制御する薄い誘電体膜)、ゲルマニウムはすぐに「消滅」し、シリコンに変わります。 過去40年にわたり、二酸化シリコン(SiO

2 )がゲート誘電体の主材料として使用されてきました。これは、その製造可能性と、サイズが小さくなるにつれてトランジスタの特性を体系的に改善する可能性があるためです。

スケーリングのルールは単純です-トランジスタのサイズを小さくすると、誘電体の厚さが比例して減少します。 したがって、たとえば、65 nmの技術的プロセスを備えたチップでは、SiO

2のゲート誘電体層の厚さは約1.2 nmであり、これは5原子層に相当します。 実際、これはこの材料の物理的限界です。トランジスタ自体のさらなる減少の結果として(したがって二酸化シリコン層の減少)、ゲート誘電体を通るリーク電流が大幅に増加し、それが大幅な電流損失と過度の発熱につながるためです。 この場合、二酸化シリコン層は電子の量子トンネリングの障害になりません。そのため、トランジスタの状態の保証された制御の可能性はなくなります。 したがって、すべてのトランジスタ(最新のプロセッサでは数十億に達する)の完全な製造でも、少なくとも1つのトランジスタの誤動作はプロセッサロジック全体の誤動作を意味し、マイクロプロセッサが実際に動作を制御することを考えると、災害に容易につながる可能性がありますすべてのデジタルデバイス(最新の携帯電話から自動車の燃料システムまで)。

トランジスタの小型化のプロセスは物理学の法則に反することはありませんでしたが、コンピューターの進歩は止まりませんでした。 これは、誘電体の問題が何らかの形で解決されたことを意味します。 そして、彼らは本当に決断しました-45nmに切り替えると、Intelは新しい材料、いわゆるhigh-k誘電体の使用を開始しました。 高誘電率k(high-k)のハフニウムの希土類酸化物に基づく層(SiO

2の場合は20対4)が厚くなっていますが、これにより漏れ電流は10倍以上減少し、正確かつ安定した制御能力が維持されていますトランジスタの動作。 新しい誘電体はポリシリコンで作られたゲートとの互換性が低いことが判明しましたが、これは障害になりませんでした-新しいトランジスタのゲートは動作速度を上げるために金属で作られました。

このように、Intelはハフニウムを使用したマイクロプロセッサの大量生産に切り替える世界初の企業になりました。 さらに、企業はまだ手のひらに属している-誰もまだこの技術を再現することはできません。 誘電体膜は原子堆積によって作成され、材料はたった1原子の厚さで連続した層に堆積されます。

ハフニウム (lat。ハフニウム、Hf)-1923年にオープンした、周期系の72元素である耐火性の銀白色の重金属。 世界では、年間平均約70トンのハフニウムが採掘されています。

金属は希土類であり、採掘されるのは比較的少ないという事実にもかかわらず、心配する必要はありません。 第一に、酸化物が使用され、第二に、酸化膜の厚さが時間とともに減少するだけです。 そして第三に、1立方センチメートルのハフニウムを取り、チップに使用されるそのような厚さの層で表面全体に分布させると、10フットボールフィールドに相当する領域がハフニウムのフィルムで覆われます。 そのようなもの:)

|

興味深いことに、これらのパラグラフを読んだ後、何十億ものトランジスタがこのような小さな領域にどのように設計、構築、および適合されるのかというアイデアを得ましたか? そして、最終的にどのように機能し、同時に非常に合理的なお金がかかりますか? 私はとても思いやりがありましたが、これがすべて明白だと思う前に、私は考える良心さえ持っていました

。 1つのプロセッサのみ! ":)

1965年、インテルコーポレーションの創立者の1人であるゴードンムーアは、後に彼の名前の有名な法律となった経験的観察を記録しました。 メモリチップのパフォーマンスの増加のグラフを提示して、彼は奇妙なパターンを発見しました:チップの新しいモデルは、前任者が登場してから約18-24か月後に定期的に開発されましたが、チップの容量は毎回約2倍に増加しました。

後に、Gordon Mooreはこのパターンを予測し、マイクロプロセッサーのトランジスタ数は2年ごとに2倍になることを示唆しました。

トランジスタの数は増え続けていますが、「出力」プロセッサのサイズは比較的変化していません。 繰り返しになりますが、秘密はありません。次の関係を見ると明らかになります。

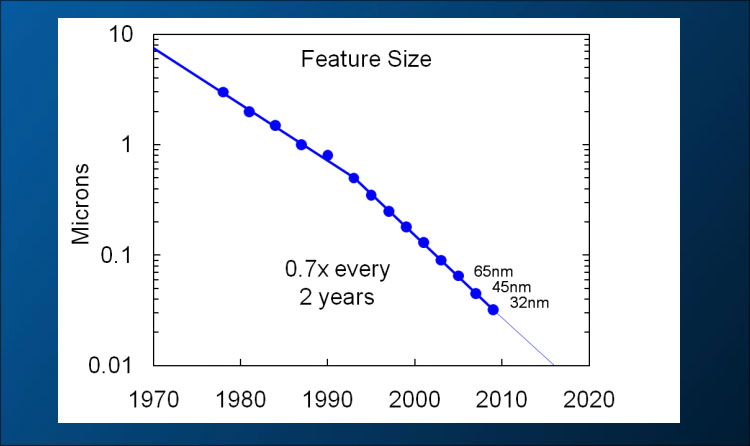

ご覧のとおり、2年に1回、トポロジの次元が0.7倍減少しています。 トランジスタのサイズを小さくした結果、スイッチング速度が速くなり、価格が下がり、電力消費が少なくなります。

現在、Intelは32nmテクノロジーを使用したプロセッサーをリリースしています。 45nmテクノロジーとの主な技術的違い:

-9つのメタライゼーションレベルが使用されます

-新世代のHigh-k誘電体が使用されます(酸化ハフニウムですが、特別な添加物が含まれています-結果の層は0.9 nmの酸化ケイ素と同等です)

メタルゲートを作成するための新しい技術プロセスの作成により、すべてのトランジスタのパフォーマンスが45%に比べて22%向上し、最高の電流密度を必要とする要素の密度も最高になりました。

生産

インテルは、米国、イスラエル、アイルランドの3か国でプロセッサを製造しています。 現時点では、32nmテクノロジーを使用したプロセッサの量産用に4つの工場があります。 これらは、オレゴンの

D1Dと

D1C 、アリゾナの

Fab 32 、ニューメキシコの

Fab 11Xです。 これらの工場の設計とその作業には多くの興味深いことがありますが、次回はこれについてお話します。

このようなプラントのコストは約50億ドルであり、一度に複数のプラントを作成すると、投資額を安全に増やすことができます。 技術の変更は2年に1回行われることを考えると、工場は50億ドルを投じて利益を上げるためにちょうど4年を費やしていることがわかります。 そこから明らかな結論が示唆されます-経済は技術進歩の発展を非常に支配します...しかし、これらすべての巨大な数字にもかかわらず、単一トランジスタの製造コストは下がり続けています-今では10億ドル未満です。

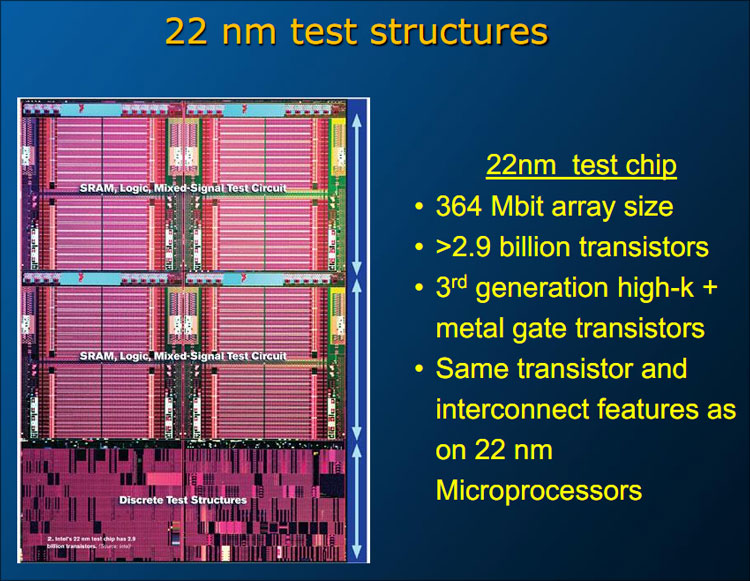

いくつかの工場が32nmに移行すると、この技術プロセスに従ってすべてが突然実行され始めると考える必要はありません-同じチップセットと他の周辺回路はそれを必要としません-ほとんどの場合45nmを使用します。 22nmの境界は、来年には早くも完全に取得される予定であり、2013年までに16nmになる見込みです。 少なくとも今年、テストプレート(22nm)がすでに作成されており、その上でプロセッサが動作するために必要なすべての要素のパフォーマンスが実証されています。

* nE0による UPD * ゲート誘電体の厚さを減らす必要性は、フラットコンデンサの単純な公式によって決まります。

* nE0による UPD * ゲート誘電体の厚さを減らす必要性は、フラットコンデンサの単純な公式によって決まります。 トランジスタのゲート面積が減少し、トランジスタの動作のために、ゲート誘電体の容量を維持する必要があります。

トランジスタのゲート面積が減少し、トランジスタの動作のために、ゲート誘電体の容量を維持する必要があります。

そのため、その厚さを減らす必要があり、より高い誘電率を持つ材料を見つけることが不可能になったとき。シリコン時代はいつ終わりますか? 正確な日付はまだ不明ですが、間違いなくそう遠くありません。 22nmテクノロジーでは、間違いなく「戦う」ことになり、おそらく16nmのままになります...しかし、楽しい部分が始まります。 原則として、周期表は十分に大きく、そこから選択するものがたくさんあります)しかし、ほとんどの場合、すべては化学だけではありません。 トポロジの寸法を小さくするか(現在実行中)、またはキャリア移動度の高い他の化合物を使用することにより、プロセッサの効率を高めることができます-ガリウムヒ素、おそらく「センセーショナル」で有望なグラフェン(ところで、移動度は数百倍です)シリコンよりも高い)。 しかし、問題があります。 現在、この技術は直径300 mmのプレートを処理するように設計されています-そのようなプレートに必要なヒ化ガリウムの量は単に自然ではなく、このサイズのグラフェン(言葉は「デカンタ」を書くことを強く主張します)はまだ非常に困難です-彼らはそれを行う方法を学びましたが、多くの欠陥、問題があります複製、合金化など

おそらく、次のステップはシリコン上に単結晶ヒ化ガリウムを堆積させ、次にグラフェンを堆積させることです。 そして、おそらく、マイクロエレクトロニクスの開発は、技術の改善の道筋だけでなく、根本的に新しいロジックの開発の道筋にも沿って進むだろう-これもまた否定できない。 賭けましょう、紳士? ;)

一般的に、現在、技術と高いモビリティのための闘争があります。 しかし、1つ明らかなことがあります。進行を停止する理由はありません。

ティックタック

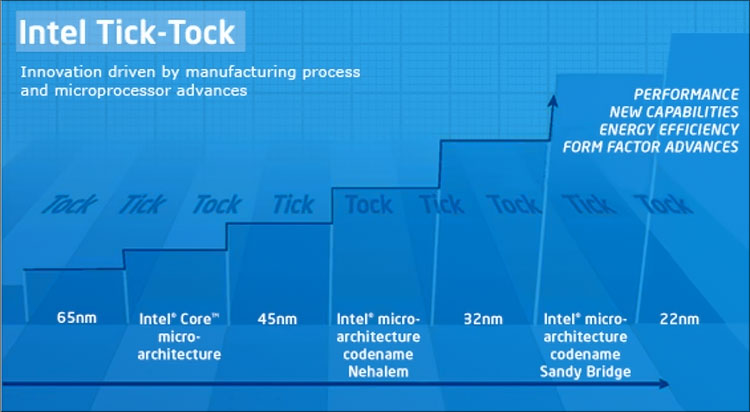

プロセッサの製造プロセスは、2つの大きな「パーツ」で構成されています。 最初は製造技術そのものが必要であり、2番目は何をどのように作成するか、つまりアーキテクチャ(トランジスタがどのように接続されているか)を理解する必要があります。 新しいアーキテクチャと新しいテクノロジーの両方が作成された場合、障害が発生した場合に「犯人」を見つけるのは困難になります。「建築家」のせいだと言う人もいれば、技術者のせいだという人もいます。 一般に、このような戦略に従うことは非常に近視眼的です。

インテルでは、新しいテクノロジーとアーキテクチャの導入が時を経て広がります-テクノロジーは1年で導入されます(そして、既に開発されたアーキテクチャは新しいテクノロジーを使用して生産されます-何かがうまくいかない場合、技術者が責任を負います); そして、新しいテクノロジーが完成すると、アーキテクトはそのための新しいアーキテクチャを作成します。実績のあるテクノロジーで何かがうまくいかない場合、アーキテクトは責任を負います。 この戦略は「Tick-Tack」と呼ばれていました。

| Tick- tockは、2006年9月にIntel Developer ForumでIntelによって発表された広範なマイクロプロセッサ開発戦略です。開発サイクルは2つの段階に分けられます-tickとそうです。 「ティック」とは、プロセスの小型化とマイクロアーキテクチャの比較的小さな改善を意味します。 「そう」とは、新しいマイクロアーキテクチャを備えたプロセッサのリリースを意味しますが、既存のプロセスを使用します。 Intelの計画によると、サイクルの各部分には約1年かかります。 |

より明確に:

技術開発の現在のペースでは、研究開発への膨大な投資が必要です-インテルは毎年このビジネスに40億から500億ドルを投資しています。 仕事の一部は社内で行われますが、多くは社外にあります。 会社の研究所全体を

ベル研究所 (ノーベル賞受賞者の偽造)のように保つことはほとんど不可能です。

原則として、最初のアイデアは大学に置かれています-大学が取り組むべき理にかなっていること(需要のある技術と関連するもの)を知るため、すべての「半導体企業」はコンソーシアムで結ばれました。 その後、彼らは一種のロードマップを提供します-それは半導体産業が今後3-5-7年に直面するすべての問題について話します。 理論的には、どの企業も文字通り大学に行き、何らかの革新的な開発を「活用」する権利を持っていますが、開発者大学は原則としてその権利を保持しています。このアプローチは「オープンイノベーション」と呼ばれます。 インテルも例外ではなく、定期的に学生のアイデアに耳を傾けます。保護、エンジニアリングレベルでの選択、実際の条件でのテストの後、アイデアは新しいテクノロジーになる可能性がすべてあります。

以下は、インテルが提携している世界中の研究センターのリストです(大学を除く)。

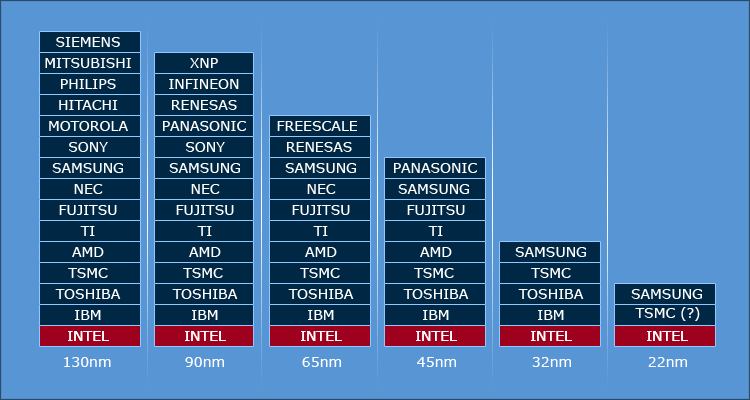

生産性の向上は、より高価な工場につながり、これが自然選択につながります。 そのため、たとえば、4年以内に回収するために、各Intel工場は1時間あたり少なくとも100枚の作業プレートを生産する必要があります。 各プレートには数千個のチップがあります...そして特定の計算を行うと、Intelが世界のプロセッサ市場の80%を持っていなかった場合、会社は単純にコストを回収できなかったことが明らかになります。 結論-私たちの時代に私たち自身の「デザイン」と私たち自身の生産の両方を行うことは非常に不採算です-少なくともあなたは巨大な市場を持っている必要があります。 自然選択の結果を以下に示します-ご覧のとおり、その「設計」と生産により、技術の進歩に追いつく企業はますます少なくなっています。 他の人はすべて、ファブレスモードに切り替える必要がありました。たとえば、Apple、NVIDIA、AMDのいずれにも独自の工場がなく、他社のサービスを使用する必要があります。

Intelに加えて、世界で22nmテクノロジーに対応できる可能性のある企業は、サムスンとTSMCの2社だけです。昨年、自社工場に10億ドル以上を投資しました。 さらに、TSMCには独自のデザインユニット(ファウンドリのみ)がありません。実際、他社からの注文を受け付けるハイテクフォージであり、多くの場合、それが何を偽造するかさえ知らないのです。

ご覧のように、自然選択はわずか3年で非常に速く通過しました。 これから2つの結論を引き出すことができます。 1つ目は、工場がなければ業界のリーダーになる可能性は低いということです。 第二-実際、あなたはあなたの植物なしで成功することができます。 概して、優れたコンピューター、頭脳、および「描く」能力で十分です-市場参入のしきい値が大幅に低下しているため、多くの「スタートアップ」が登場しています。 誰かが存在するか、特定の市場が人為的に作成された特定のスキームを思い付く-初心者メーカーが上昇しています...利益! しかし、ファウンドリ市場へのしきい値は劇的に上昇し、成長し続けるだけです...

近年、他に何が変わったのですか? 2004年まで、「プロセッサの周波数が高いほど良い」という声明はかなり公平でした。 2004年から2005年にかけて、プロセッサの周波数はほとんど成長しなくなりました。これは、一種の物理的な限界に達することに関連しています。 マルチコアのパフォーマンスによりタスクを並行して実行できるため、生産性を向上できます。 しかし、1つのチップ上で多くのコアを作成することは大きな問題ではありません。負荷で正しく動作させることははるかに困難です。 結果として、この瞬間からソフトウェアの役割は劇的に増加し、「プログラマー」という職業の重要性は近い将来にのみ勢いを増すでしょう。

一般的に、上記を要約すると :

-ムーアの法則が引き続き適用されます

-新しい技術と材料の開発コストの増加、および工場の維持コストの増加

-生産性も向上しています。 450mmプレートに切り替えるとジャンプが予想されます

その結果 :

-企業を「ファブレス」と「ファウンドリ」に分離

-コアR&Dのアウトソース

-ソフトウェアの開発による差別化

終わり

読むのは面白かったですか? そう願っています。 少なくとも、このすべてを書くことは私にとって面白かったし、それを聞くことはさらに面白かった...最初は「この講義で何を語るのか」と思ったが。

先週、モスクワ工科大学で、インテルフェローアカデミ

シャンのボリスババヤンが2回目の講義を行いました。 講義はロシアのマイクロプロセッサ開発の歴史に捧げられました-残念ながら、私は2回目の講義で同様の記事を書く時間がありません。 したがって、来られなかった人のために、私はこの講義の録音のみを提供することができます。

今週の水曜日(2010年11月24日、同じ場所で)は、「砂からプロセッサへ」というサイクルの最終講義となります。ロシアのIntel Labsの責任者であるOleg Semenovが実施します。 入場は無料です。

じゃあね!

じゃあね!