超小型回路の内部に関する以前の記事(

1、2 )の後、多くの人が写真は確かに興味深いと書きましたが、何が何であるかを知りたいと思います。

今日、この自然な関心を満足させる機会がついに現れました。

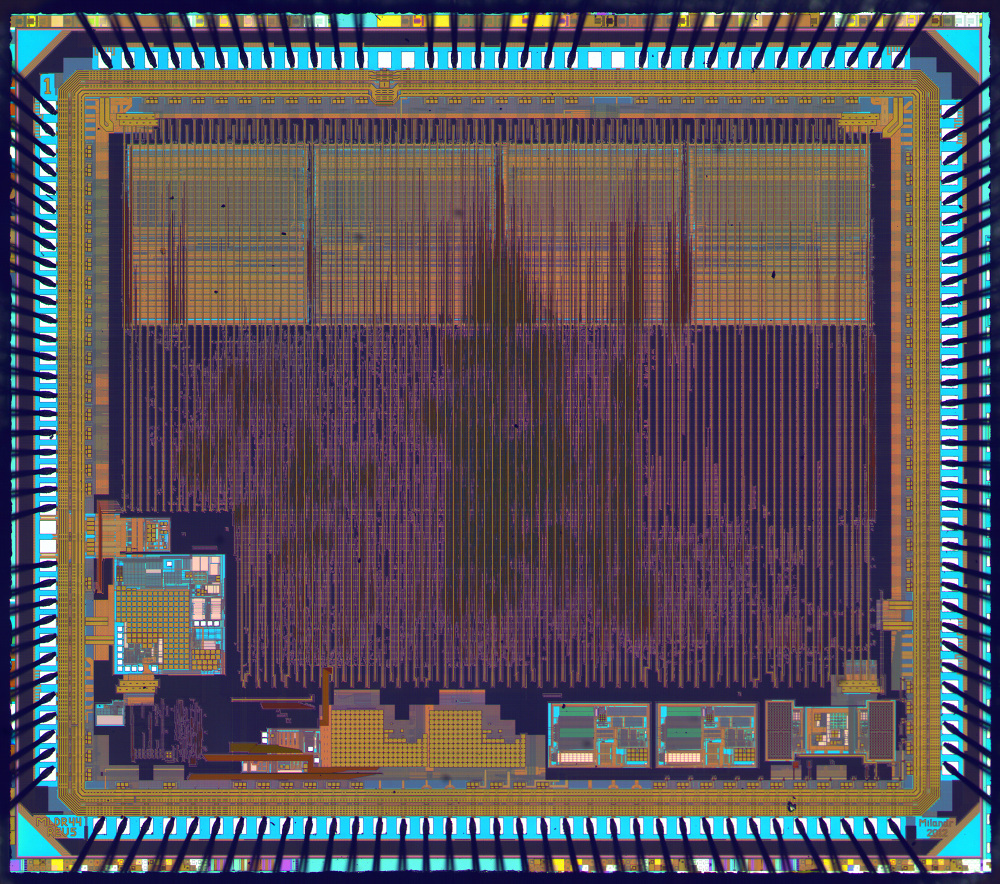

1986VE91Tを

選択します。これは、ARM Cortex-M3コア(公式ライセンス)に基づくMilanderマイクロコントローラーです。 内側-128 KiBのフラッシュメモリ、32 KiBのスタティックメモリ、ハードウェアUSB、および80 nmコア、180 nmテクノロジーを使用して作成。

見て

超小型回路上の端子とパッドを接続するワイヤは残りました。ケーシングは金属セラミックであり、エッチングする必要はありませんでした。 すべての詰め物は、アルミニウム化合物のいくつかの層に私たちの目から隠されています。 クリスタルのサイズは6.54x5.9mmです。

私たちはメタライゼーションを毒します...彼らはほとんど底に達しました:

そして、ここにトランジスタとポリシリコン層(接続の最初のレベルとトランジスタゲート)の最下層があります:

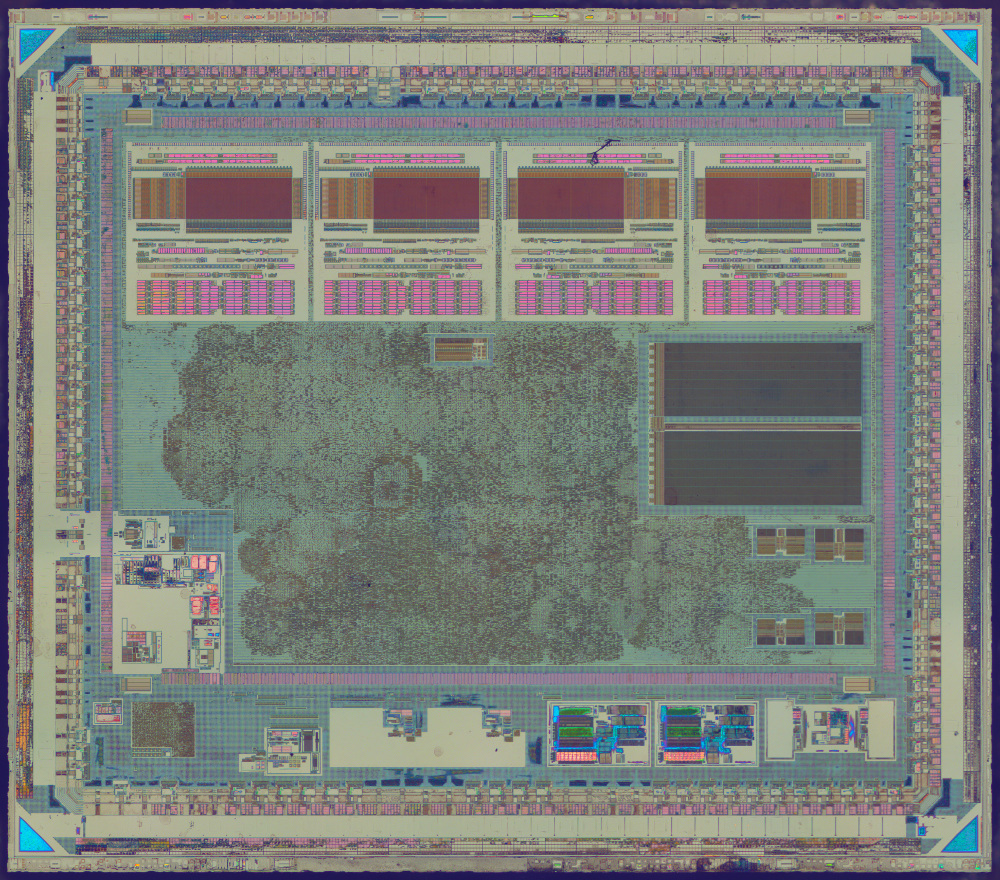

クリスタルブロック抽象

IOセルとボンディングパッド

IOセルとボンディングパッド -微細回路の各足を制御し、静電気からの保護要素を含み、入出力モードに切り替えることができる回路の標準部品。 パッド直下にトランジスタはありません- ワイヤを溶接すると、損傷する場合があります。

4x32KiBフラッシュ -フラッシュメモリの4つの標準ブロック。 なぜ大きなものではないのですか? フラッシュコンパイラは、32ビットより広いバスでメモリを生成できませんでした。パフォーマンス上の理由から、128が必要でした。

32KiB SRAMは、電源を切っても状態が保持されない高速の静的メモリです。

256x32B ROM-ブートメモリ。 工場で「ジャンパー」でプログラムされており、変更できません。

USB PHY -USBプロトコルの物理インターフェース。 シグナルレシーバー/トランスミッターのみがあり、USBコントローラーのデジタル部分は、クリスタルの中央にある合成された「混乱」の中にあります。

内部リニアレギュレータ(1.8V) -電源電圧を1.8Vに下げるための内部回路。 1.8Vトランジスタは、動作中に3.3Vよりも大幅に少ないエネルギーを消費するため、これが必要です。

バッテリードメイン -超低消費電力用に設計されたバッテリー駆動回路。 これは、リアルタイムタイマー、数バイトのメモリ、外部32kHzクオーツのジェネレーターです。

RCオシレーター -内部RCオシレーター(低周波数および高周波数)。クォーツなしでマイクロコントローラーを使用できます。

システム/ USB PLL-システムおよびUSBの周波数逓倍スキーム。 たとえば、10 MHzの水晶から80 MHzのシステム周波数、USBの48 MHzを取得できます。

2xDAC-デジタルからアナログへのコンバーター。

2xADC-アナログ-デジタルコンバーター。 空の場所-これらはおそらくコンデンサーでした。

2xCAN SRAM-静的メモリの小さなブロック。 これらはおそらく2つのCANコントローラーなどのバッファーです。

上記のブロックのほとんどはゼロから開発する必要はありませんが、工場でライセンスを取得するか、IPを開発および販売する企業から購入できます。 ただし、この場合-すべてのデジタルブロック(タイマー、CAN、USB、RAM / ROMコントローラー、外部バスなど)、アナログADC、DAC、ジェネレーター、PLL、ビルトインLDO、および独自のI / Oパッドでさえ、購入しただけですコア、DMA、UART、SPI。

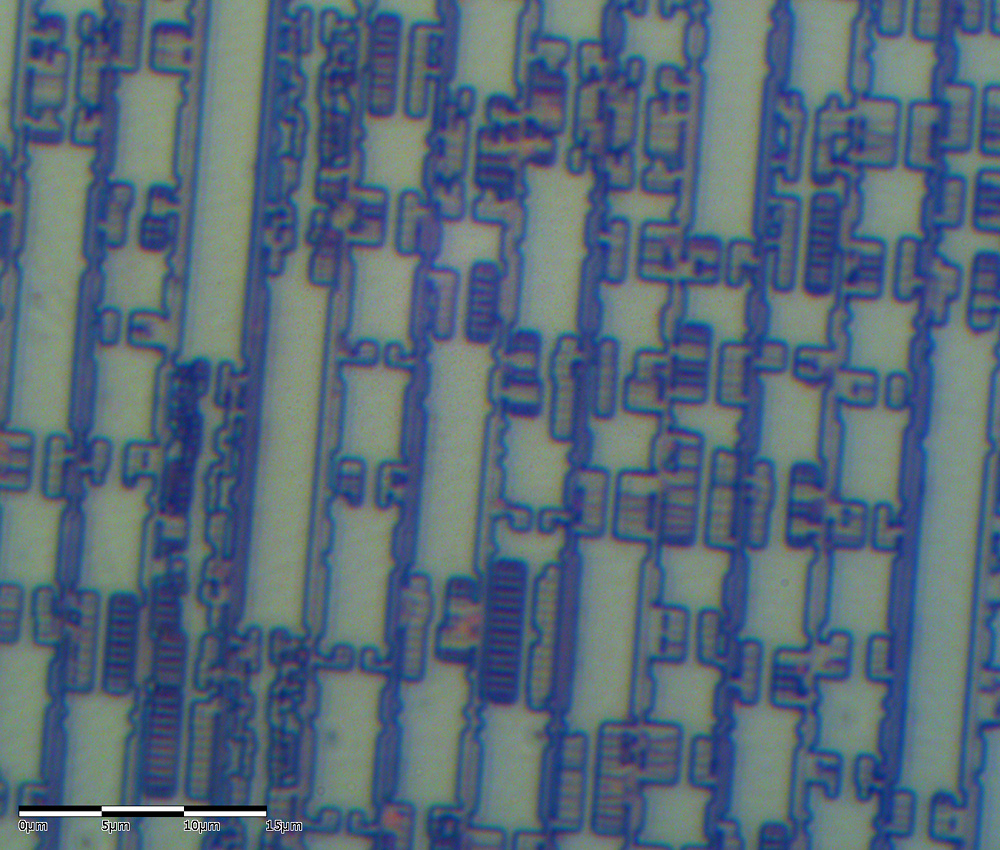

セルベースの合成ロジックは、

Verilog記述から自動的に合成された回路です。 ここでは、プロセッサコア自体と周辺コントローラの両方。 回路はトランジスタから直接合成されるのではなく、固定高の標準セルから合成されます。AND、OR、トリガーなどのさまざまな機能を実装します。

個々の要素を詳しく見てみましょう。

ブートROM必要に応じて、コンテンツを「読み取る」ことができます。 しかし、もちろん、この場合は必須ではありません。 ブートROMは、デバッガーを通して表示されます。

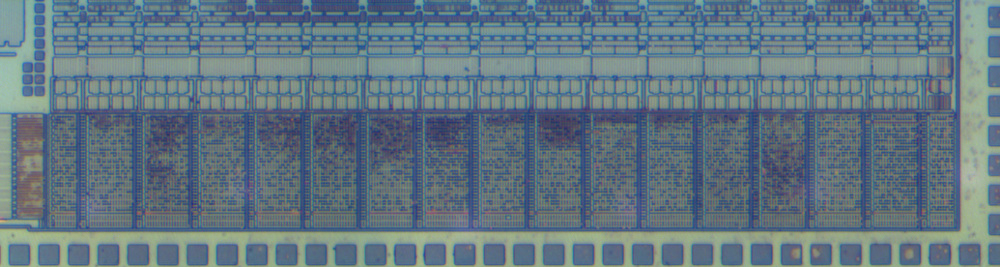

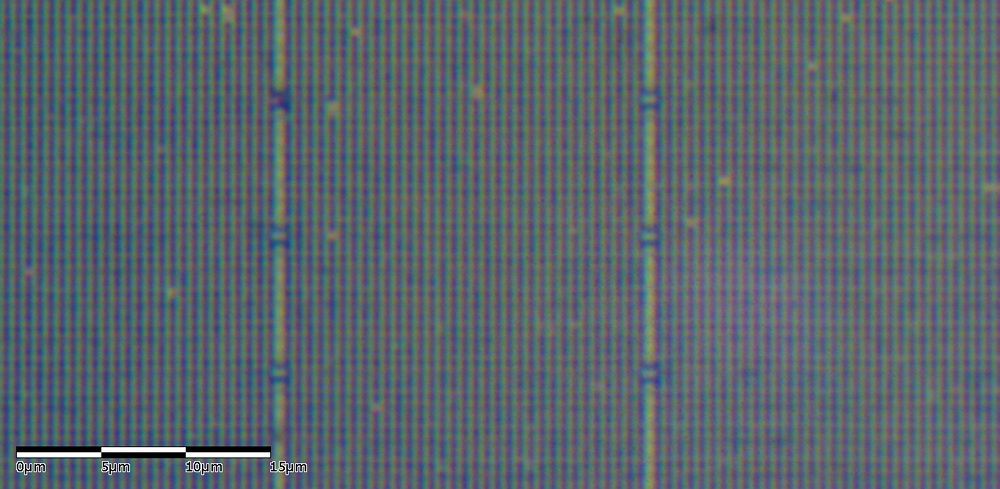

SRAM

SRAM9.14μm2のセル面積は、180-250nmの技術に対応します。

フラッシュ

フラッシュフラッシュがマイクロコントローラーに大量に押し込まれた理由をすぐに見ることができます-セルは非常に小さな領域を占有します(ビットごとに1つのトランジスタ、時にはトランジスタの半分しか必要ないため):

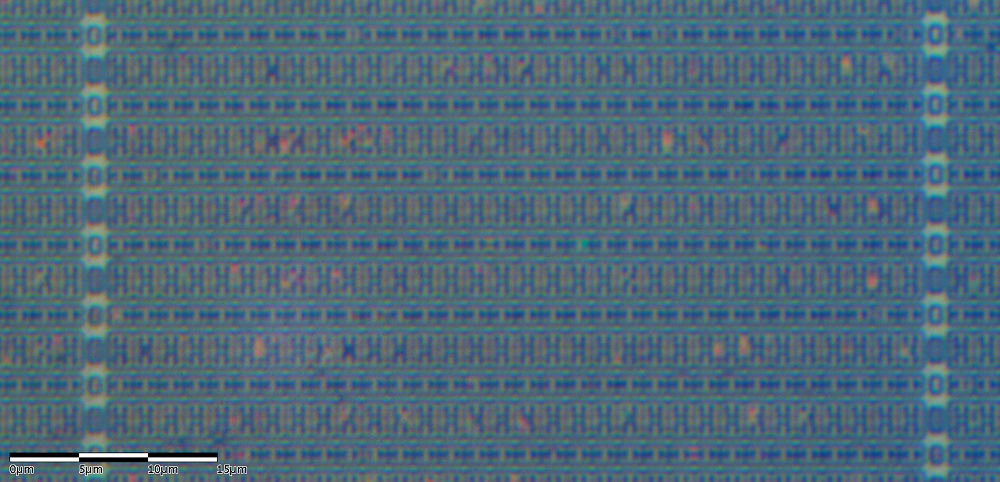

合成ロジック

合成ロジックそしてここに、メインのデジタルミンチチップであるスタンダードセルの列があります。 もちろん、ここでセルが実行する特定の機能を把握することはできません。 金属を見なければなりません。

これですべてです。私の話が面白かったと思います。 まあ、将来的には-私はすでに個々のトランジスタのレベルで、より簡単な方法でマイクロ回路の内部を解析しようとします。