この記事では、言語の合成されたサブセットのVerilog-2001と比較した、データ編成の分野におけるSystemVerilogの革新のいくつかを示します。

SystemVerilogの歴史は、長さと霧のコンテンツです。 Verilog-95標準の採用に始まり、Verilog-2001で頂点に達しました。 ただし、この言語は検証にあまり適していませんでした。「E」ファミリーの言語を使用するエンジニア-VERA、Testbuider。 SystemVerilogは、2005年以降、最新の形で登場しました。 現在、Quartus II、ISE、ModelSim / QuestaSimなどの合成ツールとモデリングがSystemVerilogを自信を持ってサポートしています。 標準はIEEE 1800-2012と呼ばれます。

ご注意 この記事は長い間書かれていますが、公開されていません。 初心者に役立つことを願っています。SystemVerilogは、多くの新しい興味深いデザインをVerilogの世界にもたらしました。

- C-lile構文

- OOP

- 構造、キュー、動的配列、列挙

- 型キャスト

- foreach、return、break、continueなどでプログラムの動作を制御する

- セマフォ、メールボックス。

- インターフェース

- アサーション

ユニバーサル型ロジック。

現在、regとwireを選択する必要はありません。ロジックはどこでも使用されています。 シンセサイザーが何をする必要があるかを決定します(VHDLからのhi信号)。

タイプの初期化

SystemVerilogは、改善された型初期化機能を提供します。 今書く必要はありません

reg [63:0] data = 64'hFFFFFFFFFFFFFFFF;

これだけができます:

reg [63:0] data = '1;

data = '0を書き込むと、ベクトルはゼロで初期化され、data =' bzは3番目の状態で初期化されます

列挙型。

最後に、ステートマシンは次のように記述できます。

enum {WAITE, LOAD, STORE} State, NextState; always_ff @(posedge clock, negedge resetN) if (!resetN) State <= WAITE; else State <= NextState; always_comb begin case (State) WAITE: NextState = LOAD; LOAD: NextState = STORE; STORE: NextState = WAITE; endcase end

さらに、列挙型に値を割り当てることができます。

enum {ONE = 1,FIVE = 5,TEN = 10 } state;

デフォルトでは、列挙型にはint値が割り当てられます。 ただし、このように書くことができます

//幅が1ビットの列挙型。

// 2つの状態のみを受け入れることができます

enum bit {TRUE, FALSE} Boolean; // 2 . // enum logic [1:0] {WAITE, LOAD, READY} state;

列挙型の名前の値を出力するには、次の構成が使用されます。

$display("\nCurrent state is %s (%b)", State.name);

構造

次の方法で構造を宣言します。

struct { int a, b; // 32-bit variables opcode_t opcode; // user-defined type logic [23:0] address; // 24-bit variable bit error; // 1-bit 2-state var. } Instruction_Word;

構造体でサポートされるTypedef宣言

typedef struct { // structure definition logic [31:0] a, b; logic [ 7:0] opcode; logic [23:0] address; } instruction_word_t; instruction_word_t IW; // structure allocation

デフォルトでは、構造は展開された状態で表示されます。 packキーワードを使用すると、構造をパックできます。

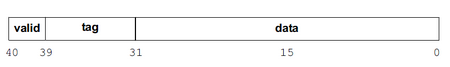

struct packed { logic valid; logic [ 7:0] tag; logic [31:0] data; } data_word;

この形式では、ベクトルとして表されます。 したがって、そのような構成が可能です。

data_word.tag = 8'hf0; data_word[39:32] = 8'hf0; //

連合

ユニオンは、さまざまな種類のデータを格納できるメモリ値ですが、一度に1つだけです。

構文は完全にCに似ています。

union { int i; int unsigned u; } data; ... data.i = -5; $display("data is %d", data.i); data.u = -5; $display("now data is %d", data.u);

実用的な最大の関心事は、パックドユニオンです。 固定タイプのビットを使用して、さまざまなタイプを表します。

あるタイプで記録された情報は、別のフォーム(別のタイプ)で読み取ることができます。 例:

typedef struct packed { logic [15:0] source_address; logic [15:0] destination_address; logic [23:0] data; logic [ 7:0] opcode; } data_packet_t; union packed { data_packet_t packet; // packed structure logic [7:0][7:0] bytes; // packed array } dreg;

ユニオンはパッケージ化されているため、情報は調整され、ロジック[7:0]を介して記録されたデータはdata_packet_tを介して読み取ることができます。

initial begin logic [15:0] src, dst; for (i = 0; i <= N; i = i + 1) begin dreg.bytes[i] <= byte_in; //store as bytes end src = dreg.source_address; dst = dreg.destination_address; end

パックドアレイ

SystemVerilogを使用すると、多次元パック配列を作成できます

logic [3:0][7:0] data; // 2-D packed array logic [1:0][3:0][7:0] data; // 3-D packed array

IEEE標準では、これらの要素をメモリに保存する方法を定義しています。 たとえば、

logic [3:0][7:0] data; // 2-D packed array

配列はベクトルとしてメモリに保存されるため、ベクトルと同じ操作をすべて使用できます

logic [3:0][15:0] a, b, result; // packed arrays result = (a << 1) + b;

ベクターへのアクセスは、要素単位で行うことも、次元全体を含めることもできます。 いわゆるスライス配列。

logic [1:0][1:0][7:0] a; // 3-D packed array a[1][1][0] = 1'b0; // a = 32'hF1A3C5E7; // a[1][0][3:0] = 4'hF; // a[0] = 16'hFACE; //

直接アクセスまたはスライスを使用して、ある配列の内容を別の配列にコピーできます

bit [1:0][15:0] a; //32 , bit 0 1 logic [3:0][7:0] b; //32 , logic O,1,Z,X logic [15:0] c; // 16 logic [39:0] d; // 40 b = a; // 32 32 c = a; // 16 d = a; // 8

参照資料

1.www.asic-world.com/systemverilog2. Stuart Sutherlandによる「SystemVerilog For Design Second Edition」