みなさんこんにちは!

多くの専門家は、トップエンドのネットワーク機器が特別なチップを使用してトラフィックを処理することを知っています。 私はそのような脱穀機の開発に参加し、そのような高性能デバイス(10/40 / 100Gイーサネットインターフェイス)を作成した経験を共有したいと思います。

新しいチャネルを作成するために、ネットワーク担当者はほとんどの場合、光ファイバ、SFP +モジュールのペアをデバイスに挿入します。ライトが喜んで点灯し、パケットが到着し始めます。チップは受信者に送信し始めます。 しかし、チップはどのようにして伝送媒体からパケットを受信しますか? 興味があれば、猫へようこそ。

IEEE 802.3

イーサネットは、IEEEで採用されている標準です。 802.3標準は、イーサネットのあらゆるバリエーション(10Mから100Gまで)をカバーしています。 物理層の特定の実装に焦点を当てます:10GBASE-R(「通常の」10G、フリルなし)。

この図は、OSIモデルのレイヤーと、それらがイーサネットプロトコルのサブレイヤーにマップされる方法を示しています。

サブレベル:

- PHYは物理サブレベルです。

- MACは、メディアアクセス制御のサブレイヤーです。

PHYは次の部分に分かれています。

- PMD-物理インターフェイスで個々のビットの送受信を提供します。

- PMA-データのシリアル化/逆シリアル化、およびシリアルデータからのシュレッドの割り当て(受信時)を提供します

- PCS-スクランブル/デスクランブル、およびデータブロックのエンコード/デコード(64b / 66b)を提供

- XGXS -XGMIIエクスパンダー:PHYとMACが互いに離れている場合に使用(オプション)。

- RECONCILIATIONは、XGMIIをMAC信号に変換するサブレイヤーです。

条件:

- 中 -伝送媒体。

- MDIはメディア依存のインターフェイスです。

- XGMII -10Gメディアに依存しないインターフェース。 XGMIIの目標は、PHYとMACの間にシンプルで安価な接続を提供することです。

- XAUI-トランシーバーに接続するための10Gインターフェイス。

物理層のタイプごとに、個別のPHYサブレベルの独自の実装を行うことができます。異なるコーディング、異なる伝送周波数(波長)が使用されますが、レベルへの明確な区分はどこでも追跡できます。 環境に依存しないインターフェイス(XGMII)の存在により、チップアプリケーションロジックの開発が簡素化されます。 どんな接続でも、開発者はXGMIIをどこかで入手します。 XGMIIについては後で説明します。

PMD

PMDサブレベルは環境に最も近い場所にあります。ネットワークスペシャリストによく知られている特別なモジュールがその問題を解決します。

| モジュールタイプ | インターフェース |

|---|

| ゼンパック | シャウイ |

| X2 | シャウイ |

| XFP | Xfi |

| SFP + | Sfi |

この表には、おなじみの略語XAUIが既にあります。 記事の途中でXENPAK / X2のレビューを残して、最も一般的なモジュールであるXFPとSFP +を見てみましょう。

XFI / SFI

XFIとSFIは、実際には同じインターフェース、つまり9.95〜11.10ギガバイトの速度で動作する差動ペアを表します。 速度セットは、いくつかの標準がこのインターフェースを使用できるという事実によって決定されます:10GBASE-W WANから10GBASE-R over G.709まで。 速度が10.3125ギガバイトの10GBASE-R LANに関心があります。 1つのdiffparaは受信に使用され、もう1つのdiffparaは送信に使用されます。

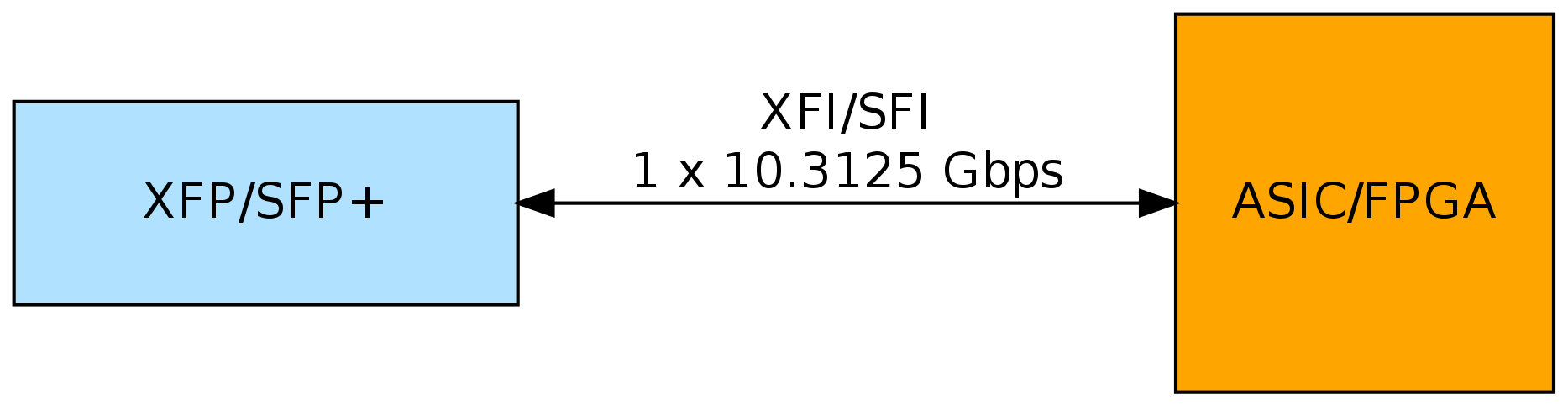

XFI / SFIはASIC / FPGAに直接接続します

PMAおよびPCSサブレベルのタスクは、チップ上で解決できます。そこで、XGMIIからイーサネットパケットを抽出した後、イーサネットパケットのさらなる処理を実行します。 PMAサブレベルでは、受信時にクロック周波数を選択し、入力信号を逆シリアル化する必要があることを思い出させてください。 このような作業は、他のタスクに使用できない特別なハードウェアユニットで実行できます。 これらのブロックはトランシーバーと呼ばれます。 詳細な記事で詳細な説明を見ることができます。興味がある人は誰でもアルテラFPGAトランシーバーのブロック図を見ることができます。

デシリアライズ後、データはPCSサブレイヤーに送られ、そこでデスクランブルとデコード(64b / 66b)が実行され、データはXGMIIの形式でMAC側に送信されます。 逆の手順で実行されます。

PCSは、特殊なハードウェアユニット(ハードPCS)とユーザーが利用できるロジック(ソフトPCS)の両方を使用して実装できます。 もちろん、この声明はFPGAにのみ当てはまります。ASICでは、すべてがハードウェアで行われます。 FPGAメーカーは、標準プロトコル用のハードウェアPCSブロックを配置し、開発者の時間とFPGAリソースを節約します。 そのようなブロックの存在は非常に魅力的です、なぜなら 多くの標準的な経験

プロトコルがそのまま

使用でき、それらのほとんどについては、FPGAメーカーがコードを無料で提供しています。

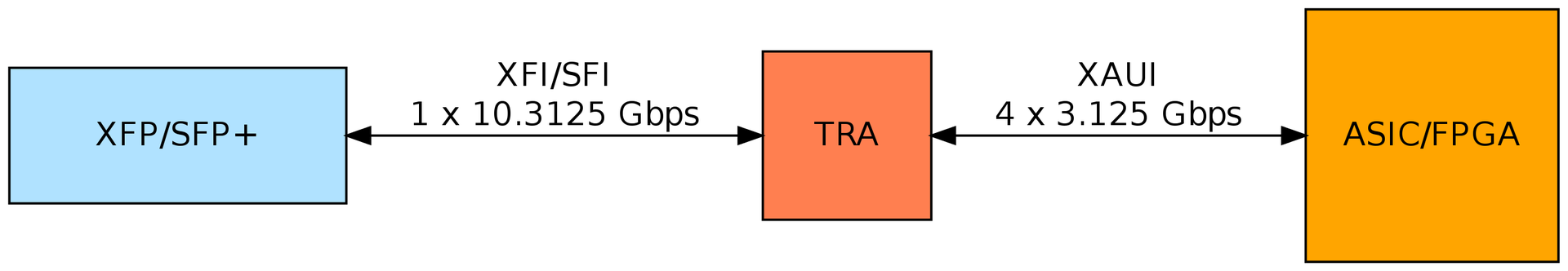

外部チップトランシーバーを介した接続

FPGAのトランシーバーは高価であり、数十個のトランシーバーを追加するとチップの価格が大幅に上昇します。 安価なチップがあり、トランシーバーは低速で動作します(低周波数でデータをシリアル化/逆シリアル化できます)。 802.3規格のセクション4で定義されているもう1つの高周波インターフェースは、XAUIです。伝送速度が3.125ギガバイトの4つの差動ペア(1本の伝送ライン)。

XAUIを使用すると、オプションのXGXSレベルが発生します。これにより、PHYとMACをある距離だけ離すことができます。 たとえば、異なるチップで実行します。

このような接続でのPMAとPCSのタスクは、特別な10Gトランシーバーで実行できます(FPGAで「トランシーバー」が少し前にポップアップし、今ではこの用語が表示されるため、混乱が生じる可能性があります。 )

10Gトランシーバーの例:

このトランシーバーは、XFP / SFP +モジュールとイーサネットパケットを処理する「当社」チップの間に配置された別個のチップです。 実際、PMAおよびPCSブロックを使用するこのようなトランシーバーは、XFI / SFIをXGMIに変換し、XGMIIはXAUIに変換されます。

XAUIはASIC / FPGAに供給され、以前に検討されていたものと同様のトランシーバーを使用しますが、速度は3.125Gです。 トランシーバーの動作は、10Gモードとは異なります。

- 4つのトランシーバー(4つのハードウェアユニット)が必要です。 このインターフェイスには4つのdiffpairsが使用されます。

- XAUI PCSは8b / 10bエンコードを使用します。 10G PCSは64b / 66bを使用します。

XAUI PCSはXGMIIインターフェイスを出力します。

一部のPHYトランシーバーはすぐにピンにXGMIIインターフェイスを発行できるため、ASIC / FPGAのトランシーバーを使用する必要はありません。

この接続方法には重大な欠点があります。

- ピン消費量が多い:XGMIIバリアントでは、XAUIバリアントでは16であるのに対して、1つのチップは最低78レッグを使用します。

- パラレルインターフェイスでは、ボード上のトラックの位置合わせが必要になる場合がありますが、これは重要な場合があります。

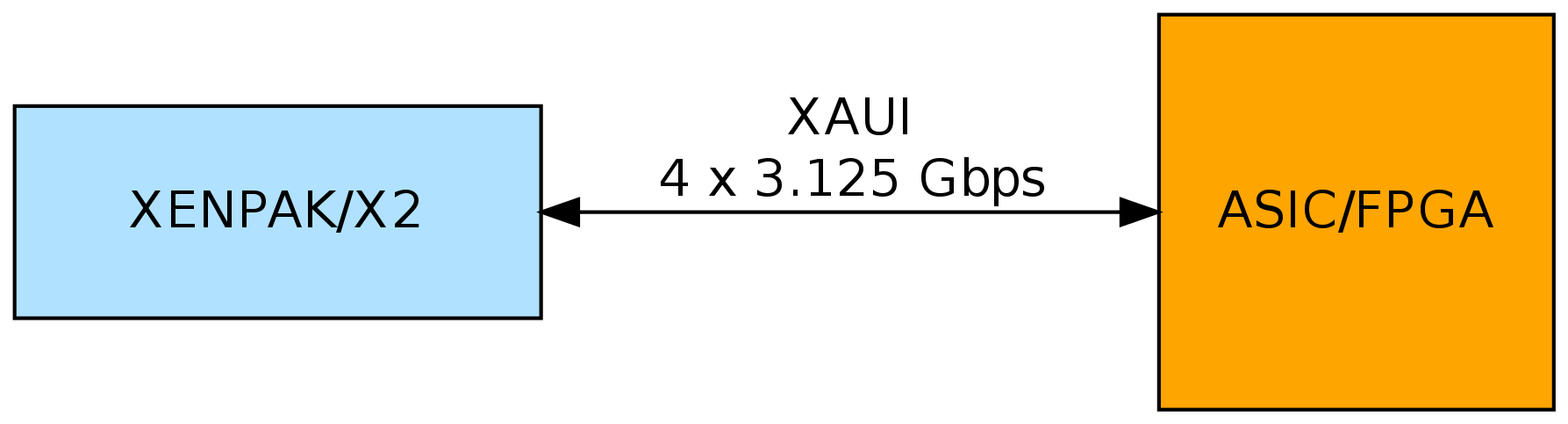

XENPAK / X2接続

私が約束したように、これらのタイプのモジュールに到達しました。 外部トランシーバチップを使用しない場合にのみ、接続が2番目のオプションに減ることがわかります。 モジュールは、PMD、PMA、およびPCSサブレベルのタスクを引き継ぎます。

XGMII

XGMIIは、802.3標準の46節で定義されています。 このインターフェイスは、独立した受信と送信で構成されます。 各方向には、32ビットのデータバス(RXD / TXD [31:0])、4つの制御信号(RXC / TXC [3:0])、および方向が機能するブロック(RX_CLK / TX_CLK)があります。 この規格では、データバスとパイロットバスがブロックの各エッジ(DDR)で分析されることを定義しています。 パケット自体がデータバスを通過し、制御信号が開始を決定し、パケットの開始と終了を「強調」し、事故を報告します。

RX_CLK / TX_CLKの値は156.25 MHzです。 156.25 * 10 ^ 6 * 32 * 2を掛けると、正確に10ギガビット/秒になります。 ほとんどの場合、シュレッドの両端でのスナップがなくなり、データの頻度または幅が増加します。

- 312.5 MHzの周波数のバス36ビット(32 + 4)。

- 156.25 MHzの周波数のバス72ビット(32 * 2 + 4 * 2)。

周波数が低いほど、このデータの処理が容易になり、より多くの予算のチップを使用できます。 最高300 MHzの周波数で動作できるのは、トップエンド(読み取り、高価)FPGAのみです。

XGMIIからパッケージを「取得」するために、特別なMACカーネルが使用されます。

- 専有。 このようなIPコアのライセンスを購入すると、(ほとんどの場合)暗号化されたソースを(変更の可能性なしに)受信し、このコアを使用できるチップの数に特に制限はありません。 例 。

- オープンソース。 このようなカーネルは、初心者にとって非常に便利です。 コードは開いており、どのように機能するかを理解できます。 使用ライセンスは別途決定されます。 例 。

- サモピスノエ。

もちろん、このカーネルには送信部分があり、パッケージはXGMIIインターフェイスに「変換」します。

ほとんどの場合、このようなカーネルは、カスタムタスクで使用可能なロジックに実装されています。 ただし、ハードウェアにMACコアを実装し、ユーザーリソースを節約するFPGAの

メーカーがあります。

XGMIIからパケットを選択し、チップの内部メモリにパケットを配置したMACコアは、パケットの制御をチップアプリケーションロジック(パーサー、フィルター、スイッチングシステムなど)に「転送」します。たとえば、チップがネットワークカード上にあり、決定が行われた場合パケットはホストに送信する必要があるため、PCIeを使用してCPUに接続されたRAMに送信できます。

個人的な経験

L1では、デバイス用のボードを繁殖させる回路エンジニアに対処する必要があります。 FPGAプログラマーは、ハードウェアアップグレードの開始時にのみこれを使用します。XGMIIが動作を開始し、すべてのトランシーバーがテストに合格したとき、トラフィック処理の方法に集中します。 1つのデバイスでは、最初のオプションに従って接続が行われました。SFIはFPGAに直接入ります。 第2の実施形態の他の2つ(トランシーバーとXAUIを使用)。 また、SFIへの直接接続とXAUIを介した接続の両方を備えたデバイスがありますが、トランシーバはありません(FPGAは別のチップに接続します)。

外部トランシーバー(そして実際、ほとんどの専用チップ)を使用するには、NDAに署名する必要があります。 これにより、特別な問題はほとんど発生しません。 NDAとともに、たとえばチップレジスタ設定など、さまざまなドックが発行されます。 2つの異なるメーカーのトランシーバーを使用した経験から、最初のバッチでアイロンを上げると、比較的迅速に解決されるトランシーバーの調整にいくつかの問題があることに注意してください:トランシーバーは多機能であり、必要な動作モードの設定にそれらをtrickす必要がある場合があります。 チップのドキュメントが非常に悪い場合があり、異なるオプションを並べ替える必要があり、技術サポートは応答しないか、これらのチップのサポートを提供しないと公然と宣言します。

トランシーバーチップを使用する利点の1つは、ドキュメントと共に、特定のタイプのモジュールをインストールするときにトランシーバーにロードする必要がある一連のファームウェア設定を配布できることです。 私が理解している限り、これらのファームウェアはトリッキーなイコライザー設定を行います。これがないと、特定のタイプのモジュールがビットエラーで動作します。 これらのSFP +モジュールの1つ(制限アンプ付き)は、この方法で処理されました。 トランシーバーなしで接続する場合、ASIC / FPGAのためにそのような設定を自分で準備する必要があります。これは簡単な作業ではありません。

伝送媒体に依存しないインターフェースの存在により、次のように寿命が大幅に簡素化されます。 コード(アプリケーションロジック:パーサー、ジェネレーター、アナライザー、フィルターなど)は、古いプロジェクトから新しいプロジェクトに非常に簡単に移植できます。 使用された接続のタイプに関係なく。

40G / 100GをASIC / FPGAに接続(および処理)することは10Gに似ていますが、独自のニュアンスがあります。 興味深い場合は、別の記事をこれに当てることもできますが、それほど大きくはありません。

こんにちはhabr!

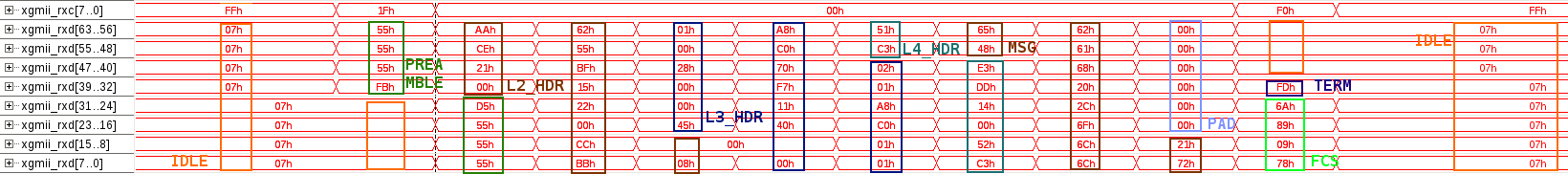

「Hello、habr!」という行を含む通常のUDPパケットを取得し、XGMIIでどのように見えるかを確認するためにデバイスに送信します。

私のテーブルには分解された

デバイスがあり、その上で新しい機能のテストが最も頻繁に行われます。明確な例のためにそれを使用します。 これを行うには、特別なファームウェアを準備し、デバッガーを接続してチップ内の信号を確認します。 10G接続は2番目のオプションに従って行われます。外部トランシーバーを使用して、XAUIを介してFPGAの側にデータを送信します。 このトランシーバは2チャネルです。2つのSFP +で動作します。

XGMII(およびパッケージ)がFPGA内でどのように見えるか:

FPGA内のこのデバイスは、周波数156.25 MHzのポジティブエッジで動作する72ビットXGMIIバスを使用します。

凡例:

- xgmii_rxc-制御信号のセット。

- xgmii_rxd-データ信号のセット(便宜上、バイトで区切られています)。

- IDLE-パケット送信がないことのシグナル。

- PREAMBLE-プリアンブル。パケットの送信の開始を示します。

- L2_HDR-レイヤー2ヘッダー:イーサネット。

- L3_HDR-レイヤー3ヘッダー:IP。

- L4_HDR-レイヤー4ヘッダー:UDP。

- MSGは私たちの投稿です( "Hello、habr!")。

- PAD-パディング。 元のペイロードの長さが60バイト未満の場合、パケットに存在します。

- FCSはパケットのチェックサムです。 転送中にパケットが破損したかどうかを判断するために使用できます。

- TERM-パケットの送信を終了する信号。

イーサネットパケットを受信する

余地がほとんどないことに気付くかもしれません。その開始と終了を(制御文字によって)見つけ、余分な

IDLE 、

PREAMBLE 、

TERMを 切り取ります。

ご清聴ありがとうございました! 質問がある場合は、間違いなく質問してください。

PSdes333と

pauligの同僚の建設的な批判とアドバイスに感謝します。