この設計は、アルテラ(Cyclone-IIファミリ)のデバッグボードEP2C20F484C7のトレーニングのある段階で利用可能になったことに促されました。

FPGAには、デジタルロジック機能を備えた集積回路に変換できる機能があります。 設計では、プログラム可能な要素(ジャンパーまたはメモリセル)を特定し、必要な機能を実行するために必要な接続のみを回路構造に残します。 実際には、最新のFPGAには平均数万個のジャンパーが含まれているため、このタスクは非常に困難です。 したがって、設計には、コンピューター支援設計システム(CAD FPGA)を使用する必要があります。

どのような場合にFPGAを使用することをお勧めしますか?

オリジナル機器を開発する場合、および中小規模の集積度の従来の電子回路を置き換える場合。 同時に、デバイスのサイズが大幅に削減され、消費電力が削減され、信頼性が向上します。 非標準の回路ソリューションを必要とする製品でのFPGAの最も効果的な使用。 FPGAでデジタルクロックを設計すると、デバッグにかかる時間が短縮されます。 使用される要素、集積回路、およびメモリブロックの数。

時計を作成するプロセス全体は、次の段落に短縮されます。1. FPGAモデルの選択。

2. VHDL言語ツールを使用してFPGA制御プログラムを作成します。

3.デバッグスタンドでプログラムをデバッグします。

4.バッテリーと表示の概念の作成。

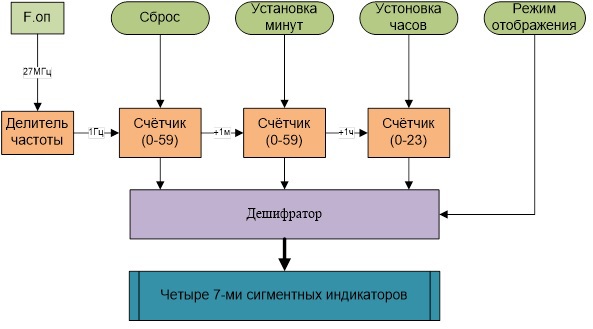

機能図時計の機能部分を図1に示します。「その他」ボタンの状態に応じて、4つの7つのセグメントインジケーターに時間と分または分と秒が表示されます。

「リセット」ボタンは、その値に応じて秒カウンタをリセットするように設計されています。30秒を超えると1分が追加され、秒がリセットされると、秒がリセットされます。 「時間」ボタンと「最小」ボタンを使用して、時計を設定します(押すことにより)。

また、時計を実装するには、高い温度と時間の安定性、低い位相ノイズ、約(10-5-10-12)の周波数安定性を備えた固定周波数を取得するように設計されたクォーツジェネレーターが必要です。

時計の構造図とその動作の説明

図2の構造図を作成するとき、ユーザーは秒をリセットし、時間と分を設定し、2つのオプションの時間/分または分/秒の表示モードを設定できる必要があることを考慮します。

設計時に、27 MHzの周波数のクォーツパルスジェネレーターを使用することが決定されました。 現在の頻度は、秒のカウントの高精度を保証するためです。

クォーツから信号がディバイダーブロックに送信され、ディバイダーブロックが周波数27 MHzの信号を周波数1 Hzの蛇行型のクロック信号に変換します。 これは、1秒で1周期の振動が通過することを意味します。

次に、分周器からの信号は、リセットコマンドを受信する最初のカウンター(2番目のカウンター)に供給されます。カウンターは入力を分析し、0〜59をカウントします。各サイクル、デコーダーにステータスを送信します。 59(カウントの最大値)に達するか、アカウントステータスが30以上のときに「リセット」が押された場合、蛇行タイプのクロックパルスをトラッキングカウンターに送信します。

2番目のカウンター(分カウンター)は、入力信号が「リセット」ではなく「最小」(分を設定)であることを除いて、最初と同様に機能します。 この結果、現在のアカウントの状態に1が追加され、アカウントの増加に貢献します。

3番目のカウンター(時間カウンター)は、先頭のカウンターと「時間」(クロックの設定)から信号を受信し、0から23までカウントします。各カウンターはカウンター値をデコーダーに送信します。

「その他」ボタンからの信号を処理するデコーダー(表示モード)は、必要な入力信号を選択します。min/ secには第1および第2カウンターの値を選択し、時間/ minには第2および第3カウンターの値を選択します。 4つの7セグメントインジケータのブロックに時間数を表示するために必要な暗号化を解除してから信号に暗号化します。

プロジェクト開発、VHDLでの時間

VHDLでプログラムを開発する際、コンポーネントを使用した構造を使用することが決定されました。 これにより、構造図の各ブロックを個別に実行するプログラムを作成できます。また、複数のブロックを1つのコンポーネントに結合することもできます。 ボタンの押された位置は「0」であり、押された「1」であることに注意してください。

timeMSと呼ばれるコンポーネントを考えてみましょう。これは普遍的なコンポーネントであり、数秒から数分使用されているようです。

ライブラリieee;

ieee.std_logic_1164.allを使用します。

ieee.std_logic_unsigned.allを使用します。

ieee.std_logic_arith.allを使用します。

エンティティtimeMSは

港

(

C:in std_logic; -+1分

R:in std_logic; -秒のためにリセットします

clk:std_logic内; -クロック信号1秒

M:out std_logic; -+1を渡す

hex:out std_logic_vector(0 to 5)-7ビットインジケーターでの出力

);

終了時間MS;

timeMSのアーキテクチャの動作は

信号cl:std_logic;

始める

プロセス(clk、R、C)

変数nex:0〜59の整数範囲。

始める

cl <= clkかどうか。

R = '0'の場合

nex> 29の場合

M <= '1';

nex:= 0;

他に

M <= '0';

nex:= 0;

終了する場合;

他に

if(cl'event and cl = '1')then

nex = 59の場合

nex:= 0;

M <= '1';

他に

nex:= nex + 1;

M <= '0';

終了する場合;

終了する場合;

終了する場合;

hex <= conv_std_logic_vector(nex、6);

終了プロセス;

終了動作;

まず、必要なパッケージ、使用するパッケージの説明を宣言します。 次に、ポートの説明に進みます。 すでに前述したように、このプログラムは2つのカウンターを組み合わせており、その結果、分カウンターと秒カウンターの両方の入力ポートがあります。

プログラムの入力ポート:

-ポート「C」-2つの値(「0」および「1」)を取り、分を設定するために使用されます。

-ポート「R」-2つの値(「0」および「1」)を取り、秒をリセットするように設計されています。

-ポート「clk」-分周器からの秒数の蛇行タイプのクロック信号(アドオンデリテルを参照)、分数の場合は先行カウンター秒からの信号。

プログラムの入力ポート:

-ポート「M」-2つの値(「0」および「1」)を取り、最大カウントに達するとクロック信号を次のカウンターに送信します。

-「hex」ポート-カウンターの状態をデコーダーに送信するための6ビットのベクトル(hexMSコンポーネントについては、追加を参照)。

このプロセスは、信号の変更(clk、C、R)に「敏感」です。また、秒の場合は非同期リセット、分の場合はアカウントに+1を非同期的に追加するプロセスです。 0〜59のタイプnexの整数変数が計算に使用されます。

プロセスの開始時に、クロック信号と「最小」ボタンからの信号が追加され、チェックされます。

「リセット」=「0」条件がチェックされ、現在のアカウント値が29を超えている場合は29を超えていない場合はゼロ、それ以外の場合はゼロでポートMに「1」を送信します。

"Reset" = '1'は、クロックパルスのリーディングエッジが到着したかどうかを確認します。 次に、カウンターを埋めるための条件を確認し、+ 1を記録します。

プログラムの最後に、nex変数の値が変換され、16進ポートに送信されます。