最近、それにもかかわらず、FPGAに向けての最初の一歩を踏み出し、

あなたに電話をかけました 。 FPGAに対する私の熱狂的な情熱と、FPGAはデバイスを作成するのに最適なプラットフォームであるという考えが信心深くなりました。 私のセクトFPGAは、マイクロコントローラーの完全な拒絶を説き、特に極端な分岐は、

ソフトウェアプロセッサーだけでなく、一般的にシーケンシャルコンピューティングの拒絶を説きます!

いつものように、真実の理解は実際の問題を解決することによって助けられました。 今日の説教では、若いFPGAの多くに当てはまる試験についてお話したいと思います。 試練を乗り越えて、真実を理解します。 しかし、答えが見つからなかった質問があります。 そのため、経験を積んだハブロフスク兄弟のFPGAが議論に参加し、弟たちに援助の手を貸してくれることをとても望んでいます。

この記事は初心者向けです。 その中で、トレーニングの最初に現れる可能性のある典型的な問題、質問、誤解、エラーについて説明します(それらは私に現れたため)。 ただし、この記事のコンテキストは、

Verilogの Quartusの

アルテラの FPGAで開発が行われているという事実によって制限されています。

何もせずに生きることは難しいですが、私たちは困難を恐れていません!

多くの人が現在Verilogを学習し始めていない理由の1つは、実際のFPGAがないことです。 高価であるため注文できない人、何をすべきかわからないため注文する人(選択については

前の記事で説明しました)。 誰かのFPGAがまだ郵送されています。

しかし、私の開発では、「ハードウェアで」プロジェクトをテストする必要がある場合、開発の最終段階ですでに実際のFPGAが必要であるという結論に達しました。 問題は、ほとんどの時間をシミュレータを使用してコードをデバッグすることに費やしていることです。

したがって、私のアドバイス:

FPGAがないことは、非アクティブなままでいる理由ではありません。 シミュレーターでFPGAモジュールを作成およびデバッグします!Verilogのシミュレーター

それでは、退屈な長い労働日(もしそうなら)で何が楽しいのでしょうか? もちろん、FPGAをマスターしています! しかし、アルテラの開発環境全体がインターネットの3か月の作業制限の重さの場合、どのように機能させることができますか? フラッシュドライブに持っていくことができます! ただし、研究対象がVerilogの場合は、メモ帳、IcarusVerilogコンパイラに限定して、GTK Waveで結果を確認できます。

今すぐお試しくださいWindowsで開始するには、リンク

http://bleyer.org/icarus/ [11.2MB]から

iverilog-20130827_setup.exeインストールファイル

(開発スナップショット)をダウンロードするだけ

です。問題のインストールは発生しません。 では、少し先に進んでみましょう。プロジェクト用のフォルダーを作成し、その中にまだ明確でない内容のファイルをいくつか作成します。

モジュールテストコードを含むモジュールファイル-bench.v`timescale 1ns / 100 ps module testbench(); reg clk; initial begin $display(); $dumpfile(); $dumpvars(0,testbench); clk <= 0; repeat (100) begin #10; clk <= 1; #10; clk <= 0; end $display(); end

テストベンチテストモジュールはbench.vファイルに記述されており、テスト信号ソースclk(蛇行)が作成されます。 他のモジュールは別のファイルで作成されます。または、このモジュールで最初にロジックをテストしてから、別のモジュールに移動できます。 次に、これらのモジュールのインスタンスがテストベンチモジュールに追加され、入力にテスト信号を送信して、結果を取得します。 階層を構築できるモジュールから、誰にでも明らかだと思います。

BAT現在のフォルダーから他のモジュールを追加することにより、メインモジュールをコンパイルおよびシミュレートするファイル-makev.bat iverilog -o test -I./ -y./ bench.v vvp test pause

このファイルを開始すると、$ display(これはデバッグ出力です)で指定されたテキストが画面に表示されます。信号と回路レジスタの値はtest.vcdファイルにあります。 ファイルをクリックして、表示するプログラム-GTKWave(私の場合はD:\ iverilog \ gtkwave \ bin \ gtkwave.exe)を選択します。 数回クリックするだけで、clkが表示されます。

実際には、メモ帳で新しいモジュールをそれぞれ作成し、IcarusVerilogをデバッグします。 このようなデバッグ後の次のステップは、Quartusのモジュールをチェックすることです。 Quartusには独自のシミュレータもありますが、私はあまり使用しません。 その理由は、コードの更新とIcarusVerilogでの結果の表示の単純さです。変更をファイルに保存し、BATを起動し、GTKWaveの「更新」ボタンをクリックしました。 ModelSimでは、これにはもう少し移動が必要ですが、特に複雑な構造のデータでは、悪くはありません。

シミュレーションの後、Quartusを起動します。 しかし、ファームウェアをFPGAにアップロードするには時期尚早です。 神のコンピューターがどのような回路を取得したいかを正しく理解していることを確認する必要があります。Verilogの形式で考えを述べます。

シミュレーションと実際のハードウェアでの作業の違い

最初は、盲目の子猫のように、私は横棒に頭を打ちました。 正しいコードがまったく機能しないか、期待どおりに機能しないようです。 またはそれはちょうど働いたが、今では突然停止した!

好奇心itive盛な子猫は、自分の行動と結果の間の関係を探し始めます(

「ピジョン迷信」 )。

最大のドラマ

以下は奇妙なリストですが、最初に私が遭遇した最大のドラマ:

すべてのVerilogコンストラクトが鉄で合成できるわけではありません 。 これは、モジュールに統合されてハードウェアで動作するハードウェアロジックだけでなく、Verilogが記述しているためです。 また、Verilogでは、テスト済みモジュールを組み合わせてテスト信号を入力に送信し、通常はコンピューターでのテスト専用に存在するテストモジュールについても説明しています。 時間の経過に伴う信号値の変更は、Verilogテキストに「#」記号を含む構造によって指定されます。 そのような兆候は時間の遅れを意味します。 上記の例では、これがCLK信号の生成方法です。 そして、実際のFPGA内でも同じ方法で、たとえばRS232を介してメッセージを送信するためのビットシーケンスを生成できるのは罪深いことだと思いました。 結局、50 MHzジェネレーターからの信号はFPGA入力に送られます! 多分彼女はどういうわけか彼に焦点を当てています。 結局のところ、奇跡を望んだのは私だけではありません:1、2、3、4、5。 現実はいつものように厳しいものになっています:FPGAはロジックのセットであり、ジェネレーターから特定の値までクロックサイクルで値が増加するカウンターを使用する場合、または何らかの方法で(ただし常にハードウェアで)時間遅延が発生する可能性があります。

見つかった奇妙なリスト

しかし、本を読んで驚くべきこと[1,2]は、この悪魔に光を当てます。 さらに、恵みが得られます。

regを指定した場合、それが作成されるという事実ではありません

どのようにして問題が発生しましたか? 1つのモジュールがあり、その入力が(パラメーターのタイプごとに)値を送信する必要があるとします。 将来的には、このパラメーターは外部イベントに応じて時間を変更する必要があります。 したがって、値はレジスタ(reg)に格納する必要があります。 ただし、外部イベントを受信する実装はまだ実装されていないため、レジスタを変更せず、単に元の値に設定しますが、将来的には変更されません。

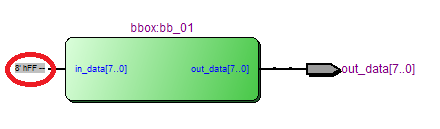

// 8 reg [7:0] val; // initial val <= 8'd0240; //wire wire [7:0] out_data; // , bbox // bb_01 // , in_data out_data // val, wire - out_data bbox bb_01(.in_data(val), .out_data(out_data));

キャッチは何でしょうか? 命令型PLでは、変数を定数として設定することが多く、その後変数を変更することはなく、すべてが機能します。 鉄には何が見えますか?

まず、レジスタが表示されません。 次に、8'd0240ではなく、8'hFFがモジュールの入力に供給されます! そして、これは計画が計画どおりに機能しないことを保証するのに十分です。 レジスタがないという事実は正常です。 Verilogはさまざまな方法でロジックを記述できますが、同時に、シンセサイザーは常にハードウェア実装を最適化します。 alwaysブロックを作成してその中のレジスタを操作しても、出力値は常に入力ブロックによって決定されるため、ここでレジスタを使用する必要はなく、シンセサイザはそれを配置しません。 逆に、入力データの一部の値で出力値が変わらない場合は、レジスタラッチなしで行う方法はなく、シンセサイザはそれを作成します。 (Book 1 pp。88-89)。 これから何が続きますか? たとえば、ボタンの押下に応じて、レジスタの値の変更を開始すると、ジェリスターが既に作成され、すべてが正常に機能します。 ボタンが何も変更しないことが判明した場合、シンセサイザーは再びそれを捨て、再びすべてが壊れます。 定数をどうするか? モジュールの入力に直接送信する必要があります。

bbox bb_01(.in_data(8'd0240), .out_data(out_data));

これで、モジュールの入力で正しい値が得られました。

レジスタを減らすときに、初期値の値がモジュールの入力に置き換えられない理由は謎のままです。

ワイヤの寸法は、自分で設定するのが最適です。

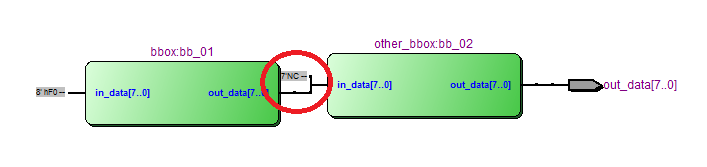

Quartus環境で開発する場合、事前にワイヤラインを設定しないでください。 この場合、それらは自動的に作成されますが、警告が発行されます。 問題は、配線容量が1ビットになり、ポートの容量が1ビットを超える場合、値が送信されないことです。

bbox bb_01(.in_data(8'd0240), .out_data(int_data)); other_bbox bb_02(.in_data(int_data), .out_data(out_data));

警告

Warning (10236): Verilog HDL Implicit Net warning at test.v(15): created implicit net for "int_data"

結果:

ご覧のとおり、1ビットが接続され、残りの7ビットは未接続(NC)で取得されます。 このような問題を回避するには、ワイヤーを自分で作成する必要があります。 IcarusVerilogコンパイラーが警告を出さないことは何もありませんが、ワイヤが事前に指定されていない場合はエラーになります。

wire [7:0] int_data; bbox bb_01(.in_data(8'd0240), .out_data(int_data)); other_bbox bb_02(.in_data(int_data), .out_data(out_data));

コンピューターはモジュールを登りません。ポートのビット深度を確認してください。 さらに、ビット深度は異なる場合があり、すべてのビットがモジュールの入力または出力から取得されるわけではなく、特定のビットが取得されます。

論理関数の出力をクロック信号として使用することはできません

プロジェクトでは、クロック周波数を下げるか、Nクロックサイクルの時間遅延を導入する必要がある場合があります。 初心者は、カウンターとカウンターが特定の値に達したかどうかを判断するための追加のスキーム(比較スキーム)を使用できます。 ただし、比較回路からの出力をクロックとして直接使用すると、問題が発生する可能性があります。 これは、論理回路が安定した出力値を設定するのに時間がかかるためです。 この遅延は、レース、準安定性、非同期性の結果として、クロックに対して論理回路の異なる部分を通過する信号の前をシフトします。 これについて、FPGAに対する批判として「FPGAには常に問題があります-信号の競合」という発言を聞く機会がありました。

少なくとも2、3の記事を読んだ場合:

準安定性とサイクル間同期のトリガーFPGAのパイプラインについて一言FPGAデバイスの開発方法が明らかになります。タスク全体がハードウェアブロックに分割され、それらの間のデータがコンベアに沿って移動し、クロック信号によってレジスタに同期的にラッチされます。 したがって、シンセサイザーは合計クロック周波数を知って、すべての組み合わせ回路の最大周波数を計算し、その速度がサイクル周期に適合するかどうかを判断し、FPGAで回路が機能するかどうかを決定します。 これらはすべて合成段階で発生します。 スキームがパラメーターに適合する場合、FPGAをフラッシュできます。

完全に理解するには、「クロックドメイン」に関するアルテラハンドブックを読むだけでなく、プロジェクトのTimeQuest計算パラメータの設定方法を理解する価値があります。

したがって、FPGAベースのデバイスの開発者にとっては、必要なすべての方法論が作成されており、それらを順守すれば問題はありません。

しかし、システムに反対したい場合はどうなりますか?

回路シンセサイザーの開発順序と動作により、FPGAはハードウェアレベルにあるという結論に至ります。 これらは同期回路です。 したがって、シンセサイザーの目標の1つは、時間間隔内に維持することです。 たとえば、彼は論理式を単純化し、他の回路で使用されず、FPGAの物理的結論に結び付けられていない回路の合成部分から除外します。 非同期ソリューションとアナログトリックは歓迎されません。なぜなら、それらの作業は予測不可能で、あらゆるもの(電圧、温度、製造プロセス、バッチ、FPGA生成)に依存する可能性があり、したがって、保証された、再現性のある、移植可能な結果をもたらさないためです。 しかし、誰もが安定した結果と設計のための一般的なアプローチを必要としています!

しかし、不変のレジスタを捨てて論理回路を短くする必要があるというシンセサイザーの意見に同意しない場合はどうすればよいでしょうか? 非同期ロジックで回路を作りたい場合はどうしますか? 微調整が必要ですか? あるいは、FPGAの低レベルコンポーネント上に回路を組み立てたいと思うかもしれません。 簡単! このような機会と詳細なドキュメントを提供してくれたアルテラの開発者に感謝します!

どうやってやるの? グラフィカルダイアグラムエディタを試すことができます。 Quartusでダイアグラムを描画できると聞いたことがありますか? 自分でビルディングブロックを選択し、それらを接続できます。 しかし、これは解決策ではありません! 描画された回路でさえ、可能であればシンセサイザーによって最適化されます。

その結果、私たちは古い真実に到達します:

何も助けなければ、指示を読んでください 。 つまり、

「Quartus II合成オプション」と呼ばれる

「Altera Handbook」パートです。

まず、特定の方法でVerilogのアーキテクチャを説明すると、特定の結果が得られます。 同期および非同期RSトリガーを取得するためのサンプルコードを次に示します。

// RS module rs(clk, r, s, q); input wire clk, r,s; output reg q; always @(posedge clk) begin if (r) begin q <= 0; end else if (s) begin q <= 1; end end endmodule

この場合、同期トリガーを取得します。

クロック信号を考慮せず、rとsの変更に応じて切り替えると、結果は非同期設定値を持つ要素(ラッチ)になります。

// RS module ModuleTester(clk, r, s, q); input wire clk, r,s; output reg q; always @(r or s) begin if (r) begin q <= 0; end else if (s) begin q <= 1; end end endmodule

しかし、さらに進んで、プリミティブからラッチを自分で作成することもできます(プリミティブは、他のVerilogモジュールと同じように使用できます)。

module ModuleTester(clk, r, s, q); input wire clk, r,s; output reg q; DLATCH lt(.q(q), .clrn(~r), .prn(~s)); endmodule

その結果、シンセサイザーが必要と判断したラッチの入力にある「ボディキット」全体が消え、必要なものが正確に得られます。

既存のプリミティブのリストは

既存のプリミティブのリストは 、アルテラのWebサイトで見つけることができます。

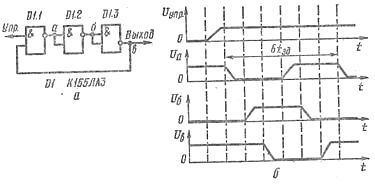

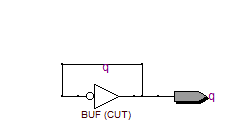

そして今、非同期と削減についての小さな例です。 たとえば、以前は慣習的だったのと同じ原理で、FPGAのみでジェネレーターを作成すると思いました。

しかし、期間を増やすために4つの要素を取りますが、そのうちの1つだけが反転されます。

module ModuleTester(q); output wire q; wire a,b,c,d; assign a = b; assign b = c; assign c = d; assign d = ~a; assign q = a; endmodule

しかし、削減(4つではなく1つの要素)を取得します。 論理的です。 しかし、その後、遅延線を考案しました。

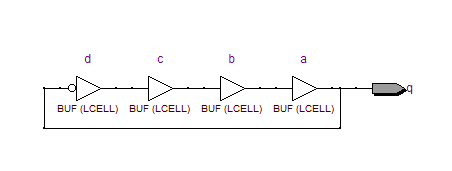

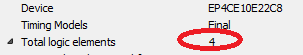

しかし、シンセサイザーを、ラインa、b、c、dが縮小されない条件に設定すると、意図したとおりになります。 シンセサイザーを支援するために

ディレクティブが使用されます。 これを示す1つの方法は、コメント内のテキストです。

module ModuleTester(q); output wire q; wire a,b,c,d ; // ^^^

そして、ここに結果があります-4つの要素のチェーン:

そして、これはすべてとは程遠い! 私はそれを独学の喜びに任せます。ケースと、RAM / ROMまたは論理回路として実装するためのディレクティブを操作します。 内蔵メモリユニット(RAM / ROM)を使用します。 乗算の実装の選択-ハードウェア乗算器または論理回路。

結論

記事を引用して、

「FPGA / FPGAはプロセッサーではない」と言いたいのですが

、FPGA(FPGAの構成メモリーを満たす)をプログラミングして電子回路(ハードウェア)を作成し、プロセッサー(固定ハードウェア)をプログラミングするとスリップします彼には、メモリ(ソフトウェア)に書き込まれた一連の順次プログラム命令 。

」さらに、最初は特定の鉄に強くなりたくなかったように、場合によっては、リソースをより効率的かつ経済的に使用するために、低レベルで作業する必要があります。 多くの場合、これは同期回路を正しく開発することで回避できます。 ただし、これが鉄であることを完全に忘れても機能しません。

私はまた、狂信と最大主義が時間とともに減少したと言いたいです。 FPGAでは許可されているため、最初はすべてのアクションとFPGA計算を1クロックサイクルで実行しようとしました。 ただし、これは必ずしも必要ではありません。 私はまだソフトプロセッサの計算カーネルを使用できませんでしたが、特定のアルゴリズムに従って動作するためのステートマシンの使用が標準になりました。 計算は1サイクルごとではなく、パイプラインの使用による数サイクルの時間遅延が標準です。

本当に助けてくれた本

1. V.V. Soloviev-Verilogデジタル機器設計言語の基礎。 2014

2.アルテラ:Quartus IIハンドブック

3.アルテラ:Advanced Synthesis Cookbook

4.アルテラ:低レベルのプリミティブを使用した設計

関連記事FPGA、アルテラおよびVerilog

FPGA業界ニュース

マイクロソフトは独自のプロセッサに切り替えますインテルは、FPGAを統合したXeonサーバープロセッサをリリースする予定ですIntelはアルテラを購入する予定RBC:インテルは167億ドルでアルテラのチップメーカーを買収FPGAニューラルネットワークを使用して最適化されたBing検索FPGAニューラルネットワークを使用して最適化されたBing検索アルテラFPGAを搭載したIntel Xeonプロセッサ理論

VLSIプログラマブルロジックに基づくデジタルデバイスの開発ハードウェア機能

準安定性とサイクル間同期のトリガー一時的なFPGA分析またはTimequestの習得方法FPGAのパイプラインについて一言Verilog。 RAMラッパーとそれが必要な理由同期回路の設計。 Verilog HDLのクイックスタート例

タイマーまたは最初のFPGAプロジェクトの作成Quartus IIと小さなVerilogを使用したFPGAクロックUSBデバイスの作り方FPGAベースのカラーミュージックFPGAプログラミング。 「連絡先の跳ね返り」の現象とそれを取り除く方法の研究(VHDL!)デジタルIIRフィルターのVerilog実装Verilog。 RAM上のデジタルフィルターFPGAはシンプルまたはDIYアルテラCyclone III FPGA VGAアダプターCPUの研究とその機能シミュレーションNES、FPGAでの実装FPGAビデオ数学関数の生成Verilogハードウェア番号ソーターシンプルなSDR FPGAレシーバーFPGAスタンドアロンSDRレシーバー開発者の10GイーサネットビューシンプルなFM FPGAベースのトランスミッターFPGAでテトリスを作成するFPGAの掃海艇FPGAでIBM PCを作成するPS

この場所を読んでくれたみんなに感謝します。 この記事で、FPGAの動作と使用の原則が少なくとも少し近くなり、より理解しやすくなることを願っています。 そして、実際のプロジェクトでのアプリケーションの例として、

今週リリースする別の記事を準備しています。 プロジェクト

機能DDS FPGAジェネレーター