ニクラウス・ワース教授(退職)

スイス連邦工科大学(ETH)

チューリッヒ、スイス

1988年、Jurg Gutknechtと私は、以前に開発したPascalとModula-2の2つの他の言語の後継であるOberonプログラミング言語[1、2]を完成させ、公開しました。 Oberon言語は、もともとModula-2よりも合理的かつ効果的であるように設計されていたため、学術教育システムの学生がコンピューターサイエンスを習得しやすくなりました。 1990年に、達成されたものにとどまらず、Windowsとワードプロセッシング機能を使用して、ワークステーション用の最新のオペレーティングシステム(OS)Oberonを構築しました。 次に、Oberonコンパイラと同じ名前のOSの両方の詳細を明らかにする本を出版しました。 「Project Oberon」というタイトルの本には、システムのソースコードが含まれていました。

数年後、友人のポールリードは、システムアーキテクチャを研究し、信頼性の高いシステムをゼロから構築したい人に良い出発点を与えることの重要性から、この本の再版を出版することを提案しました。

しかし、深刻な障害が生じました。 元のコンパイラは、すでに市場から姿を消したプロセッサ用に作成されました。 そこで、最新のプロセッサー向けにコンパイラーを書き直すことにしました。 しかし、少しの研究の過程で、明確さ、規則性、単純さの基準を完全に満たすプロセッサーを見つけることができませんでした。 そのため、独自のプロセッサを設計する必要がありました。 このアイデアは、ソフトウェアシステムを作成するのと同じようにハードウェアを作成できる最新のPPVMチップ(ユーザープログラマブルゲートアレイ、FPGA)のおかげで実現しました。 さらに、Xilinx®FPGAを選択したことで、1990年の当初のプロジェクトから大きく逸脱することなく、システムを作り直すことができました。

新しいRISCプロセッサは、1メガバイトのスタティックメモリモジュール(SRAM)を備えた低コストのDigilentSpartan®-3ボードに実装されています。 ハードウェアの改善はすべて、マウスインターフェイスと、古いシステムのハードドライブを置き換えるSDカードに関するものでした。

システム全体の本とソースコードは、

projectoberon.com Webサイトで入手できます[3,4,5]。 別の

S3RISCinstall.zipファイルも利用できます。 これには、命令、SDカードのファイルシステムのイメージ、FPGAのビット構成ファイル(Spartan-3ボードのフラッシュメモリのPROMファイルの形式)、SDカードのハードウェアインターフェイスの設計部品、およびマウスが含まれます。

RISCプロセッサープロセッサはRISC5 Verilogモジュールで表され、算術論理ユニット(ALU)、16個の32ビットレジスタの配列、およびIR命令レジスタとPCプログラムカウンタを備えた制御モジュールで構成されています(

詳細 -およそTransl。を

参照 )。

プロセッサは20の命令を処理します。4つは移動、シフト、回転用、 論理演算用に4つ。 整数演算の場合は4。 浮動小数点計算用に4つ。 2つはメモリアクセス用、2つは分岐用です。

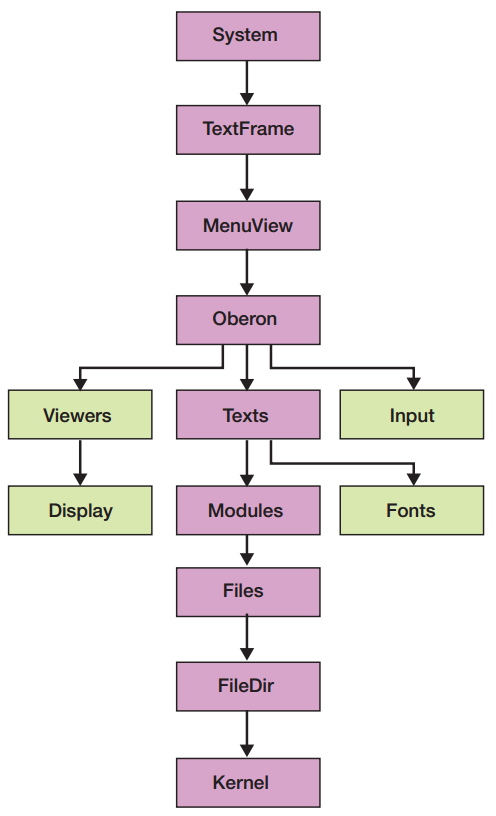

RISC5は、メモリとSRAM(256 MB x 32ビット)にマッピングされたさまざまなデバイスのインターフェイスを含むRISC5Topコンテキストからインポートされます。 システム全体(図1)

図 1. Verilogモジュールのシステム図。

次のVerilogモジュールが含まれます(各モジュールの行数が表示されます)。

| RISC5トップ | 環境 | 194 |

| Risc5 | プロセッサ | 201 |

| 乗数 | 整数演算 | 47 |

| 仕切り | | 24 |

| FPAdder | 浮動小数点演算 | 98 |

| FPMultiplier | | 33 |

| FPDivider | | 35 |

| SPI | SDカードとトランスミッター/レシーバー | 25 |

| Vid | 1024 x 768ビデオコントローラー | 73 |

| PS2 | キーボード | 25 |

| マウス | ねずみ | 95 |

| RS232T | RS232トランスミッタ | 23 |

| RS232R | RS232受信機 | 25 |

白黒VGAディスプレイをメモリにマッピングして、ピクセルあたり1024 x 768 x 1ビット= 98.304バイト(1メガバイトで実質的に使用可能なメモリの10%)を占有するようにしました。 元のシステムの80メガバイトを置き換えたSDカードへのアクセスは、バイトまたは32ビットワードを受け入れてシリアル化する標準SPIインターフェイスを介して実行されます。 キーボードとマウスは、標準のPS-2シリアルインターフェイスを介して接続されます。 さらに、シリアル非同期RS-232ケーブルと多目的8ビットパラレルI / Oインターフェイスがあります。 RISC5Topモジュールには、ミリ秒カウンターも含まれています。

OberonオペレーティングシステムOSソフトウェアには、ガベージコレクターを備えたメモリアロケーター、ブートローダーを備えたファイルシステム、テキストシステム、ビューアーシステム、およびテキストエディターを含むカーネルが含まれています。

「Oberon」と呼ばれるモジュールが中央タスクマネージャーであり、「システム」が基本的なコマンドモジュールです。 アクションは、任意のディスプレイのフォーム「MP」のテキスト上でマウスの中ボタンをクリックすることで呼び出されます。ここで、PはモジュールMで宣言されたプロシージャの名前です。Mが使用できない場合、自動的にロードされます。

ほとんどのテキスト編集コマンドは、通常のマウスクリックで呼び出されます。左ボタンがキャレットになり、テキスト内の現在の位置をマークし、右ボタンがテキストを強調表示します。

カーネルモジュールには、ディスクストア管理とガベージコレクタが含まれています。

ビューアはタイル状に配置され、重なっていません。 標準レイアウトでは、視聴者の数に制限のない2つの垂直トラックが表示されます。 これらを増減したり、タイトルバーにドラッグしたりできます。 図 図2は、キーボードとマウスを使用してSpartan-3ボードに接続されたモニターのユーザーインターフェイスを示しています。

図 2.モニターのユーザーインターフェイスとSpartan-3の右下。

ロードされたシステムは、モジュラースペースで112.640バイト(21パーセント)、ヒープで16.128バイト(3パーセント)を占有します。 図に示す次のモジュール(各行数)で構成されます。 3:

| カーネル | 271(内部コア) |

| Filedir | 352 |

| ファイル | 505 |

| モジュール(ローダー) | 226 |

| 視聴者 | 216(外側コア) |

| テキスト | 532 |

| オベロン | 411 |

| メニュービューア | 208 |

| テキストフレーム | 874 |

| システム | 420 |

| 編集 | 233 |

起動時または再起動時にシステムをロードするのに2秒しかかからないことに注意してください。これには、ガベージコレクションのためのファイルディレクトリのスキャンも含まれます。

Oberonコンパイラーコンパイラはシステムに組み込まれており、単純な再帰的トップダウン解析方法を使用しています。 コンパイラのアクティブ化は、ORP.Compile @コマンドを使用して行われます。 パーサーは、識別子、数字、および特殊文字(BEGIN、END、+など)を処理するスキャナーから文字を受け取ります。 この設計は、多くのアプリケーションでその適合性と優雅さを証明しており、私の著書Compiler Construction [6,7]で説明されています。

パーサーは、コード生成モジュールからプロシージャを呼び出し、コード配列に命令を直接追加します。 分岐命令は、すべてのジャンプポイントが既にわかっているコンパイルの最後にジャンプアドレスによって生成されます。

すべての変数アドレスは、ベースレジスタを基準にして計算されます。 これは、ローカル変数(実行時にプロシージャを入力するときに設定)の場合はR14(スタックポインター)、グローバル変数およびインポートされた変数の場合はR13です。 ベースアドレスは、アドレスがレジスタR12に格納されているグローバルモジュールテーブルからの要求に応じてロードされます。 レジスタR15は、RISCアーキテクチャに基づいてリターンアドレスに使用されます。 残りのレジスターR0-R11は、式の評価と手続きパラメーターの受け渡しに使用できます。

コンパイラー全体は、4つの比較的小さく効率的なモジュールで構成されています(各行の数が示されています)。

| ORP | パーサー | 968 |

| ORG | コードジェネレーター | 1120 |

| オーブ | ベースデフ | 435 |

| ORS | スキャナー | 311 |

コンパイラは、115,912バイト(22パーセント)のモジュラースペースと17,508バイト(4パーセント)のヒープ(コンパイル前)を占有します。 ソースコードのサイズは約65キロバイトです。 コンパイラ自体のコンパイルには、25 MHz RISCプロセッサで数秒しかかかりません[8]。

コンパイラーは、常に配列インデックスとNILポインターのチェックを生成します。 これにより、トラップが生成されます(トラップ、トラップ-およそTransl。)違反の場合。 この手法により、エラーや損傷に対する高度な保護が保証されます。 実際、PUTやCOPYなどのSYSTEM擬似モジュールの操作を使用することによってのみ、システムの整合性が侵害される可能性があります。 これらの操作は、限られた範囲で使用する必要があり、デバイスドライバーモジュールでのみ使用する必要があり、インポートリストのSYSTEMという名前で簡単に見つけることができます。 システム全体は、アセンブラコードを使用せずにOberon自体でプログラムされます。

Digilent Spartan-3ボードを選択した理由は、手頃な価格とシンプルさで、教育機関がクラスのセット全体を取得するのに適しているためです。 また、大きな利点は、ボード上に静的RAMが存在することです。これにより、直接接続(インターフェース接続)できるようになります(バイトを読み取ることも可能)。 残念ながら、最新のボードはダイナミックRAMを使用しています。ダイナミックRAMは、容量は大きいものの接続が難しく、更新と初期化(キャリブレーション)のために追加の回路が必要です。 このような回路は、スタティックRAMを搭載したプロセッサ全体と同じくらい複雑になります。 コントローラーがチップ上に納品されたとしても、制御のためにすべてにアクセスできるようにするという原則に違反しています。

最後に考え40年以上前、C。Hoarは、科学技術のすべての部門で、学生は自分の実験的な経験を得る前に、深刻な構造の多数の例の影響を受けていると指摘しました。 プログラミングおよび設計プログラムはこのパラダイムを強調しています。 学生は、さまざまなパターンを勉強するのではなく、最初からプログラムを作成する必要があります。

この恐ろしい状況の理由は、適格な例のある文献がほとんどなかったからです。 したがって、私は状況を修正することを決定し、1975年に「アルゴリズムとデータ構造」という本を書きました。 将来(J. Gutknechtとともに)、オペレーティングシステムのコースを教える一環として、Oberonシステム(1986〜88年)を設計しました。

しばらくして、システムが劇的に複雑になり、サイズが大きくなったという事実のため、プログラミングの教育は目立った改善を受けませんでした。 オープンソースは認識されましたが、状況を変えることはできませんでした。ほとんどのプログラムはできるだけ早く実行するために作成されたものであり、人がそれらをよりよく理解するためではありません。

私は、すべてのプログラムがコンピューターだけでなく、人間の理解のためにも作成されるべきであるという大胆な仮定を続けています。 それらは利用可能でなければなりません。 このタスクは、たとえ正しくて効率的であっても、実行可能プログラムを作成するよりもはるかに複雑です。 これは、アセンブラーの挿入がないことを意味します。

人的要因を無視した結果、どこにでも慎重に設計されたアプリケーションが存在せず、デバッグによって動作状態になったという事実につながり、時には悲観的な結果をもたらします。 わかりやすさを実現するためには、単純さと秩序を守り、不必要な宝石類を拒否し、口withで鐘を避けて、従来と便利を区別することは価値があります。

このようなシステムのサイズが小さいことは、多くのことを実現できることを示しています。 Oberon OSのサイズは、ファイルシステム、テキストエディター、ウィンドウシステムを含みますが、最新のオペレーティングシステムと比較して途方もなく小さいです。 副作用として、いくつかの単純なルールは、将来の参照のために非常に簡単に習得できます。

そして最後に、簡潔さの利点は、バックドアなどの未知の機能を恐れることなく、このようなシステムを安全に構築できることです。 これは重要な機能であり、システムの整合性に対する攻撃の危険性が高まっていることを考えると、セキュリティの問題にとって重要なシステムにとって非常に重要です。 同様に、システムのハードウェアに隠された部品が含まれていないことが重要です。 全体を理解するのが困難な基盤の上に構築されたシステムについては、誰も保証できません。

感謝の気持ちポール・リードの貴重な貢献に感謝します。 彼は「Project Oberon」という本を編集することを提案し、システム全体をFPGAに再実装することも提案しました。 セックスは尽きることのない励ましの源でした。 ディスクをSDカードに交換することが彼のアイデアであり、SPI、PS-2、VID Verilogインターフェイスも提供していました。

参照資料1.www.inf.ethz.ch/personal/wirth/Oberon/Oberon07.Report.pdf2.

www.inf.ethz.ch/personal/wirth/Oberon/PIO.pdf3.

www.inf.ethz.ch/personal/wirth/ProjectOberon/index.html4.

www.inf.ethz.ch/personal/wirth/Oberon/PIO.pdf5.

www.inf.ethz.ch/personal/wirth/Oberon/Oberon07.Report.pdf6.

www.inf.ethz.ch/personal/wirth/CompilerConstruction/CompilerConstruction1.pdf7.

www.inf.ethz.ch/personal/wirth/CompilerConstruction/CompilerConstruction2.pdf8.

www.inf.ethz.ch/personal/wirth/ProjectOberon/PO.Applications.pdf(12章)

アプリLolaの言語とVerilogでの翻訳

Lolaという名前のハードウェア記述言語(HDL)は、ハードウェア設計の基礎を教えるために1990年に定義されました。 テキスト定義が回路図に置き換わり始め、その時点で最初のFPGAが利用可能になりましたが、まだ産業レベルには達していませんでした。 Lolaの場合、FPGAへのロードに適したビットファイルを生成するコンパイラが作成されました。 ビットファイル形式は、Algotronix、Inc.によって開示されています。 およびConcurrent Logic Inc. どちらの形式でも、自動配線に最適な、非常に単純な構造のセルでの作業が可能になりました。

FPGA用にOberonを作り直すという私のプロジェクトの結果によると、Lolaも復活させるというアイデアが生まれました。 ザイリンクスFPGAセルはより複雑であるため、ザイリンクスがその特許ビットファイル形式を開くことを拒否したという事実にかかわらず、配置と配線を実装する努力を敢行しませんでした。

明白な決定は、独自のビットファイルを生成せず、ザイリンクスが特別なツールを提供する言語への翻訳を許可するようなLolaコンパイラを構築することでした。 Verilogを選択しました。 この解決策は、やや贅沢な回避策を暗示しています。まず、Lolaモジュールを解析してから翻訳し、最終的に再度解析する必要があります。 これらのすべての段階で、Lolaコンパイラに適切なエラー制御機能と型チェック機能があることを確認する必要があります。

Lola-2の開発を推進するには、Lola上のRISC5プロセッサのすべてのモジュールを再定式化する必要がありました。 それが行われました。

舌ローラLolaは、Oberonスタイルの簡潔で簡潔な言語です(

www.inf.ethz.ch/personal/wirth/Lola/Lola2.pdfを参照)。 簡潔にするために、ここではLolaのテキストの一例を示します(図1)。 ソーステキストの単位はモジュールと呼ばれます。 そのヘッダーは、モジュールの名前、入力および出力パラメーターの名前とタイプを定義します。 ヘッダーに続くのは、変数やレジスタなどのローカルオブジェクトの宣言のセクションです。 次は、変数とレジスタの値を決定するセクションです。 BYTEは8ビットの配列を定義します。

MODULE Counter0(IN CLK50M、rstIn:BIT;

swi:BYTE; OUT leds:BYTE);

タイプIBUFG:=モジュール(IN I:ビット; OUT O:ビット)^;

VAR clk、tick0、tick1:BIT;

clkInBuf:IBUFG;

REG(clk)rst:BIT;

cnt0:[16] BIT; (* 0.5ミリ秒*)

cnt1:[10] BIT; (*半秒*)

cnt2:バイト;

BEGIN leds:= swi.7-> swi:swi.0-> cnt1 [9:2]:cnt2;

tick0:=(cnt0 = 49999);

tick1:= tick0&(cnt1 = 499);

rst:=〜rstIn;

cnt0:=〜rst-> 0:tick0-> 0:cnt0 + 1;

cnt1:=〜rst-> 0:tick1-> 0:cnt1 + tick0;

cnt2:=〜rst-> 0:cnt2 + tick1;

clkInBuf(CLK50M、clk)

END Counter0。

図 1. Lolaのソーステキストには、ボードインジケーターに表示される秒とミリ秒のカウンターが表示されます。

Lolaコンパイラコンパイラは、単純な再帰的トップダウン解析方法を使用します。 LSC.Compile @コマンドを使用して、Lolaが選択したソースコードでアクティブにします。 パーサーは、識別子、数字、および特殊文字(BEGIN、END、+など)を処理するスキャナーから文字を受け取ります。 この設計は、多くのアプリケーションでその適合性と優雅さを証明しており、 『Compiler Construction(Part 1 and 2)』で説明されています。

その場で直接Verilogテキストを生成する代わりに、パーサーは最初に演算子ツリーを作成します。これは、さらなる処理に適しています。 このアプローチには、適切なトランスレーターによって任意の出力を簡単に生成できるという利点があります。 これらの1つは、Verilogの翻訳者です。 最初のLSV.Listコマンドoutputfile.v。 別のチームがVHDLに変換するか、単純にツリーを出力できます。 3番目は、スカウトがさらに処理するためのネットリストを生成できます。

したがって、コンパイラ全体は、少なくとも4つの比較的小さく効率的なモジュールで構成されています。

| Lss | スキャナー | 159 |

| LSB | 拠点 | 52 |

| LSC | コンパイラ/パーサー | 503 |

| LSV | Verilogジェネレーター | 215 |

LolaからVerilogへの送信手順については、

www.inf.ethz.ch /

personal /

wirth / Lola /

LolaCompiler.pdfをご覧ください 。

ソフトウェアとハードウェアの「プログラム」の違い過去には、HDL言語を「通常の」プログラミング言語のように見せるために多くの努力が払われてきました。 さらに、HDLには他のPLの中でも「倍」があり、そのスタイルに適応しています。 たとえば、VerilogはCから、VHDLはAdaから、LolaはOberonから来ました。 しかし、これらの2つのクラスの根本的な違い、特に構文の類似性、さらには同一性の存在を確認することが重要であると考えています。 これらの基本的な違いは何ですか?

説明を簡単にするために、分析を同期回路、つまりすべてのレジスタが単一のクロックに結び付けられている回路に限定します。 一般的に、同期回路は優れたアーキテクチャ上のパラダイムであり、可能な場合は従う必要があります。

さらに、回路のすべての要素が同時に、文字通り同時に機能することは明らかです。 各変数と各レジスタは、1つの式(組み合わせ回路)で定義されます。 複数の割り当ては意味がありません。 レジスタと変数への割り当てはサイクルごとに発生するため、各HDLプログラムは大きな無限ループに囲まれていることを簡単に想像できます。

シーケンサーベースのプロセッサアーキテクチャを導入するというJohn von Neumannのアイデアは素晴らしいものでした。 シーケンサには、各サイクルで特定のパターンが選択され、他のパターンが無視される命令のレジスタが含まれています。これにより、ALUのさまざまな部分を巧みに再利用できます。 メジャーまたはステップは本質的にシーケンシャルであるため、プログラム内の特定の場所および命令のシーケンスでプログラムカウンタがどのように値を関連付けるかに応じて、変数に値を再割り当てできます。 シーケンサーのアイデアにより、比較的単純な回路で巨大なプログラムを実行することが可能になりました。

そのため、Lola-2はYP OberonスタイルのHDLです。 ここで紹介するコンパイラは、LolaモジュールをVerilogモジュールに変換します。 Lolaの利点は、言語のシンプルで馴染みのある構造と、型チェックと高度なエラー診断のためのコンパイラの強調です。 Lolaに記載されているRISCプロセッサ用の完全なモジュールセット:

www.inf.ethz.ch/personal/wirth/Lola/index.html