この記事では、WS2812b LED制御について、ロジック回路の合成とマイクロコントローラー内での実装について少し説明します。 小さな余談と2つのボーナスがある記事。 最初のボーナスは、書くとき、同時に読むという事実に基づいています(そうではありませんか?)。 2番目のボーナスは、マイクロコントローラーのプログラミングを開始し、記事に記載されている実装を10分で繰り返すのに役立ちます。

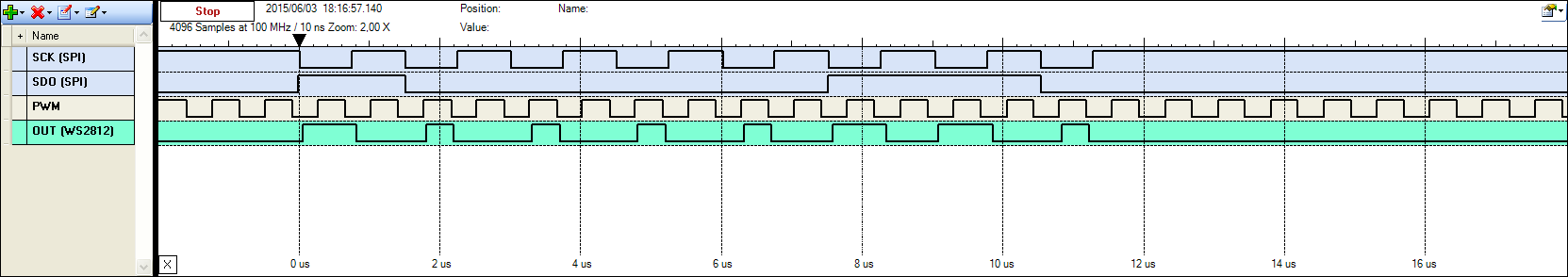

3色の「SPI LED」WS2812b(図1)とその前身であるWS2811 / WS2812は直列に接続され、単線(シリアル)バスを介して制御されます(したがって、この場合、特に「ボーナス#1」 」、SPIインターフェースが重要な役割を果たします)。 各RGBカラービット(24ビット、チャネルあたり8ビット)は、約1.25μsの周期でPWM信号(図2を参照)によってエンコードされます。 WS2812 LEDは、インターフェイスがすばやく簡単にでき、LEDの数を簡単に増やすことができるため、制御されたLEDストリップとスクリーンでよく使用されます。 したがって、たとえば、毎秒25フレームの周波数では、ビデオ画面に(40ms-50µs)/(0.125µs x 24)〜= 1300 RGB LEDの1行を含めることができます。 これはそれほどではありませんが、広告看板の場合、プラカードまたはランニングラインで十分です。

図 1.デジタルシリアルインターフェイスを備えたLEDストリップ

図 1.デジタルシリアルインターフェイスを備えたLEDストリップ 図 2.ビットコーディングパラメータ

図 2.ビットコーディングパラメータこのような短い信号を形成するために安価なマイクロコントローラーを使用すること(図2を参照)は、特定の困難をもたらします。 そのため、たとえば、クロック周波数が16 MHzのPIC16コントローラーの場合、250 nsで1つのコマンドが実行されます。 したがって、WS2812ドライバーをプログラムで制御するには、カーネル速度のほぼ100%を費やす必要があります。

インターフェイス合成

この問題を解決するために、たとえばSPIインターフェースなど、マイクロコントローラーのハードウェア機能を使用することができます。 このようなトリックは、シーケンス「11100000」が「ゼロ」の送信のために送信され、「11111000」が「ユニット」のために送信される場合によく使用されます。 1ビットはエンコードされたバイト(またはニブル)です。

もう1つの方法は、SPIインターフェイスとロジック要素を使用することです。 アプリケーションノート[1]および[2]には、説明した実装が主に基づいている例が含まれています。

したがって、SPIインターフェイスの信号を取得し、SCK信号(同期信号)を反転し、SDO(出力データ)と論理関数ANDを組み合わせると、エンコードされた「ユニット」が得られます(図3)。

図 3.「ユニット」のコーディング

図 3.「ユニット」のコーディング「ゼロ」をエンコードするには、期間の短い別の信号が必要です。 これを行うには、PWMマイクロコントローラーを使用できます。 ゼロは、論理式n(SDO)* n(SCK)* PWM(nは逆数)で記述される信号によってエンコードされます。 このような式は[1]および[2]で与えられますが、最終図(図5)からわかるように、または真理値表とカルノーマップを使用した論理回路の合成中に推定されるように、式はnSCK * PWMとして記述できます。

図 4.「ゼロ」のコーディング

図 4.「ゼロ」のコーディング「ゼロ」と「ユニット」のフローをOR機能と組み合わせて、目的のPWMドライバー制御シーケンスWS2811 / WS2812を取得することは残ります。

図 5.ストリームのコーディング結果

図 5.ストリームのコーディング結果論理式の形式では、制御信号は次のように記述されます。

(nSCK * SDO)+(nSDO * nSCK * PWM) {1}

ブール代数の定理を適用すると(たとえば、素晴らしい教科書[3]を参照)、式{1}が同等の式に変換されることがわかります。

n(SCK + nSDO)+ n(SDO + SCK + nPWM) {2}

(nSCK * PWM)+(nSCK * SDO) {3}

n(SCK + nPWM)+ n(SCK + nSDO) {4}

nSCK *(PWM + SDO) {5}

PIC16F1508、PIC16F1509など、多くのジュニアMicrochipマイクロコントローラーには、構成可能なロジックセル(CLC)が組み込まれています。

構成可能なロジックセルは、コアに依存しない周辺機器であり、マイクロコントローラー周辺機器と外部信号の論理的に接続された動作の実装に役立ちます。 カーネルからの非同期性とプログラムからの独立性により、プログラムでのみ実装するのが難しい機能を実装できます。

CLCの入力信号は、マイクロコントローラー入力、CLC出力、その他の統合された周辺モジュール、および内部ジェネレーターです。 CLC出力はポートに出力し、他のコントローラー周辺機器と共有できます。

上記を考慮すると、SPIインターフェースとCLCの組み合わせは、WS2812 LEDドライバー(WS2811)の制御信号を生成する問題を解決するための理想的なオプションのように見えます。

CLC Designerユーティリティは、CLCの視覚的構成とコード生成を目的としており、マイクロコントローラーの周辺構成は、MPLAB X開発環境へのMplab Code Configurator(MCC)プラグインを介して構成できます。

入力信号のすべての組み合わせが論理セルの入力に存在するわけではありません。 したがって、特定のタスクを実行するために必要な信号とセルの組み合わせを見つける必要があります。 CLCセルでデータをエンコードするには、SCK、SDO、およびPWM信号が必要です。 ロジックセルCLC4の入力にはSCK、SDOからの信号が含まれますが、PWMからの信号は含まれず、CLC2は入力にPWMが含まれます。 CLC2出力はCLC4入力に接続できます。 したがって、CLC2はリピータとして機能し、PWMをCLC4の入力に変換し、CLC4は式{1}、{2}、... {5}の論理機能を実行します。

図6 CLC2はPWMを出力に変換します。 Gate2-4にはlog.1出力があり、最終結果には影響しません

図6 CLC2はPWMを出力に変換します。 Gate2-4にはlog.1出力があり、最終結果には影響しません実際、提示されたフォームの関数{1}は1つのCLCセルに実装できませんが、同等のフォーム{2} ... {5}は簡単です。 (図7を参照)。

図 7. CLC4は、関数n(SCK + SDA + nPWM)+ n(SCK + SDA)を介してSPI信号のPWMエンコードを生成します

図 7. CLC4は、関数n(SCK + SDA + nPWM)+ n(SCK + SDA)を介してSPI信号のPWMエンコードを生成しますこの場合、追加のDトリガーが使用されます。これにより、コントローラーのクロック周波数に対して入力信号の同期が取れなくなり、出力の誤った切り替えが回避されます。 一般に、特定のケースでは、Dトリガーは必要ない場合がありますが、この構成は出力でより予測可能なタイミングを提供します(FOSCクロック周波数からの同期)。

余談#2。 組み合わせ論理回路のスプリアスパルス入力信号の変化が出力のいくつかの変化につながる場合があり、その結果、スプリアスパルス(グリッチ)が形成されます。 これは、変化する入力信号がいくつかの方法で出力に渡され、異なる方法で通過する論理ゲートの数が異なる場合に発生する可能性があります。 次に、各論理要素の遅延、および「最短」パスと「クリティカル」パスに沿った移動時間の差により、スプリアスインパルスが形成される可能性があります。 このプロセスは[3]で詳しく説明されています。

特定の例では、関数{1} ... {5}を実装すると、このような状況は発生しませんが、発生した場合でも、構成されたセルのOR-D構成を使用して問題を解決できます。 次に、図7dの図を図8のように再描画できます。 7(e)。追加のDトリガーが、FOSCコントローラーのクロック信号のエッジに沿った出力で値をキャプチャします。

図 7d 図と同じ機能 7g。、しかし出口ラッチ付き

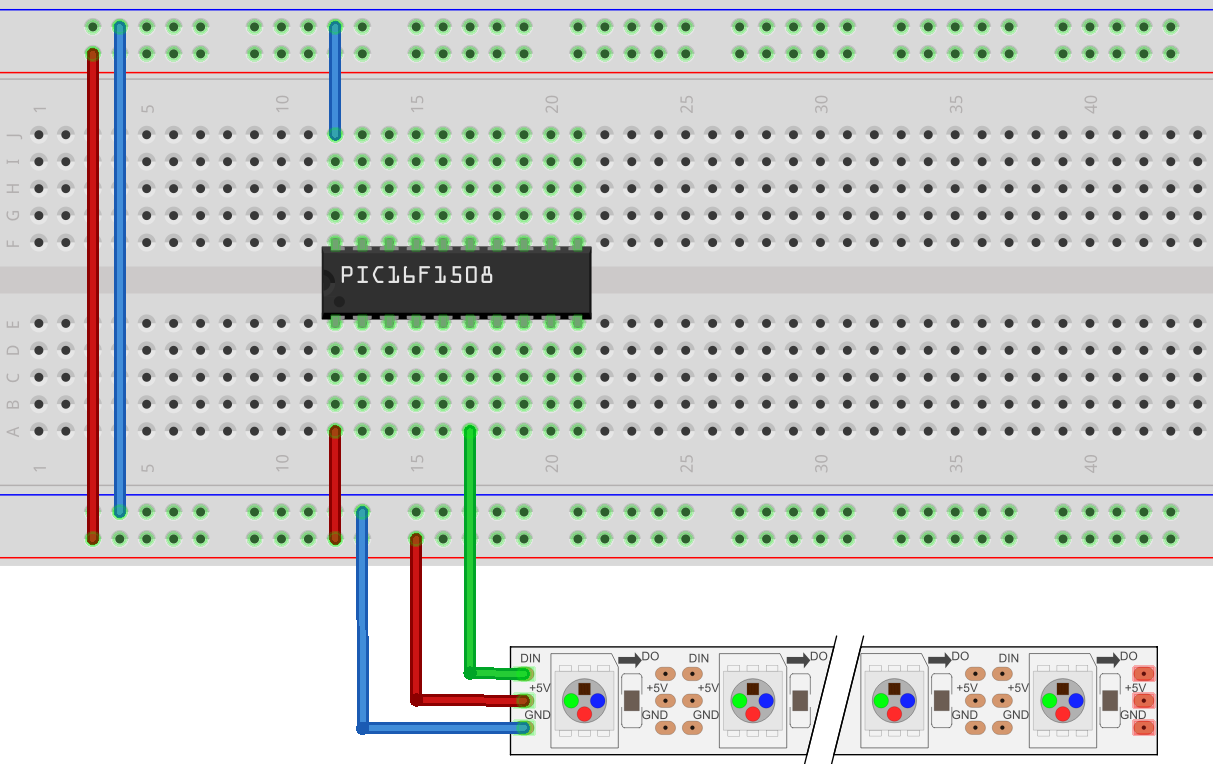

図 7d 図と同じ機能 7g。、しかし出口ラッチ付き したがって、CLC、PWM、およびSPIの構成後、準備部分は終了します。 SSP1BUFレジスタにバイトを書き込むと、CLC4の出力で、WS2812形式に従ってエンコードされたPWM信号を取得します。 SPIモジュールがデータを送信している間、マイクロコントローラーは他のいくつかのタスクを実行できます。 各LEDについて、3バイトを送信する必要があります。 接続図を図に示します。 8。

図 8. WS2812bテープをマイクロコントローラーに接続する

図 8. WS2812bテープをマイクロコントローラーに接続するボーナス#1。 メモリ増加

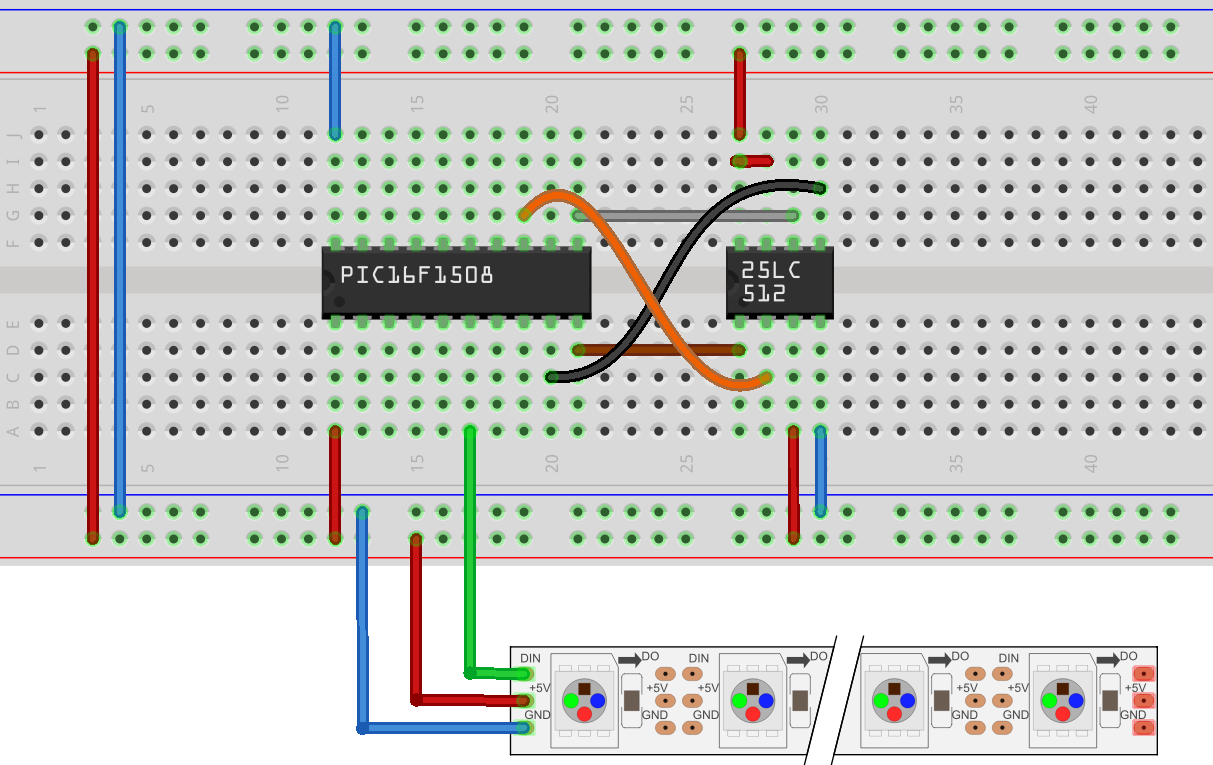

説明した方法では、構成可能なロジックとマイクロコントローラーの周辺との共同作業により、WS2812形式の一時的なプロトコルパラメーターが形成され、プログラムはバイトをSPIバッファーに書き込むだけで済み、構成可能なロジックセルがさらに「魔法」を引き継ぎます。 説明した例では、SPIは記録にのみ使用され、SDI入力ラインは空いているため、LEDの制御だけでなく、外部データの受信にもSPIを使用する絶好の機会が提供されます。 LEDの制御と同時にSPIインターフェースでメモリチップからデータを読み取る方法を考えてみましょう。

マイクロコントローラのSPIポートには、1つのアドレスを持つ2つのシフトレジスタ(送信用、受信用)があります。 SSPBUFへの書き込みはバイト転送を開始し、ビットをSDOラインにシフトしますが、同時にSDI入力ラインからのデータは同じレジスタにシフトされます。 つまり、1バイトをSPI(SDO)に送信すると同時に、SPI(SDI)からデータを受信します。

したがって、WS2812 LEDをマイクロコントローラーのSPIモジュールと、たとえばSPIメモリー(SRAM 23LC512またはEEPROM 25LCxxx)に接続し、外部メモリーからLEDストリップにデータを転送する場合、プログラムはSSPBUFからSSPBUFにデータを転送するだけです。 外部メモリからバイトを読み取り、次のコマンドでデータをSPI(LED)に送り返すと同時に、次のバイトを読み取ります。

図 9.外部メモリの接続

図 9.外部メモリの接続データの配列を外部SPIメモリに書き込む場合、またはメモリから最初のバイトを読み取る場合、LEDに「ガーベッジ」を与えないようにCLC4出力を無効にする必要があります。

LEDの配列を更新する必要がある頻度に応じて、LEDの数は非常に多くなる可能性があります。更新速度と外部メモリのサイズによって制限されます。 LEDのラインから、LEDスクリーンとディスプレイを作成できます。 表示バッファ内のデータは、画像が更新されていない間に変更できます。これにより、表示された画像を作成するために必要な、より複雑な計算、テーブル内の検索などの時間も与えられます。

外部メモリにバッファリングされたイメージが存在するため、読み取りメモリの開始アドレスをシフトすることで動画を表示できます。 SPI EEPROMメモリを使用すると、事前に記録された画像を表示できます。 SPIインターフェースを使用すると、複数のメモリチップを接続できます。たとえば、キャラクタージェネレーター、静止画像を保存するための1つのEEPROMを接続し、2番目のSRAMでLEDスクリーンに表示するためのディスプレイバッファーを作成します。

ボーナス#2。 自分でやる

ソースを調べるには、マイクロチップ社のWebサイトにアクセスできます(

AN1890サンプルのソースコード

はWebサイトで入手できます)しかし、短いビデオをご覧になることをお勧めします。5分で、上記のすべての魔法を自分の手で行う方法を示します。

ソース

1. AN1606。 構成可能ロジックセル(CLC)を使用してPIC16F1509とWS2811をインターフェイスします。 LEDドライバー

www.microchip.com2. AN1890。 大型LEDアレイ用のシンプルなSRAMバッファリング。

www.microchip.com3. D.ハリス、S。ハリス。 「デジタル回路とコンピューターアーキテクチャ」(http://habrahabr.ru/post/259505/)