この記事はトピックシリーズの続きで、

VHDLの Delay要素、VHDLのDelay要素。 FPGAに実装されたVHDL遅延要素の

別の見方 。

特定の応用例に重点が置かれ、誰でもシミュレータまたは実際のハードウェアで実行できます。 このサンプルは、Modelsim SEを使用したザイリンクスISE環境での便利なシミュレーション用に作成されたもので、最小限の変更で本格的なIPコアに実装されています。

問題の声明

コアロジックの周波数と同期していない可能性がある、パルス信号の位相シフトを所定の値で実行します(パルスの持続時間は任意です)。 モジュール/デバイスを再起動またはシャットダウンせずにこれを行います。

ツール

バイナリコードの遅延コードが設定される8ポジションのDIPスイッチ(シフト値)。 ハードリセットまたはソフトリセット-初期リセット、デフォルトパラメータの設定。 基準周波数は100 MHz、つまり10 nsの最小オフセット時間です。

実装

インパルスを論理ユニットと呼びます-1。

一時停止、論理ゼロ-0。

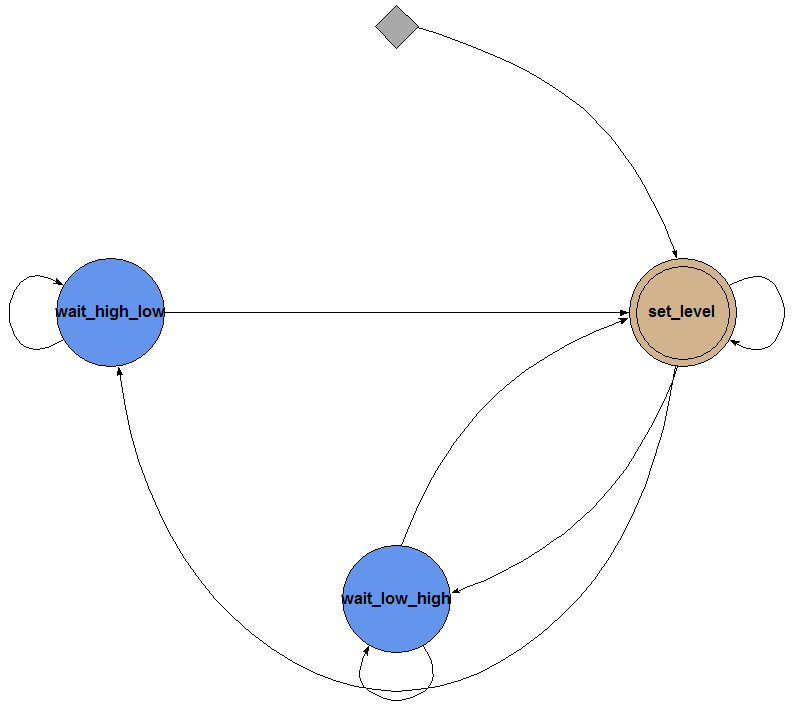

コードはステートマシンとして実装されます。これは、段階的な構造と各ステージに明確な名前を付ける機能のおかげで、非常にシンプルで理解しやすいと思います。

コードに関するコメントに加えて、テストベンチシミュレーションファイルが含まれています。

ステートマシン図:

基本的なロジック。 コードは信号レベルの変化を監視し、その値が設定されたシフトと等しくなるとカウンターが開始し、円でモニターされているのと同じレベルが出力されます。

freq_shift_half_cycle.vhdlibrary ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity freq_shift_half_cycle is Port ( Bus2IP_Clk : in STD_LOGIC;

Modelsimのシミュレーションコード:

testbench_half_cycle.vhd LIBRARY ieee; USE ieee.std_logic_1164.ALL;

経験豊富な電子技術者は、このコードの欠点に気付くことができます。 設定された遅延は以下を超えてはなりません。

-パルス持続時間、パルス持続時間が休止時間より短い場合。

-ポーズの継続時間がパルスの継続時間より短い場合、ポーズの継続時間。

つまり 位相シフトの大きさは、パルス信号の場合、0と1の両方で180°を超えてはなりません。

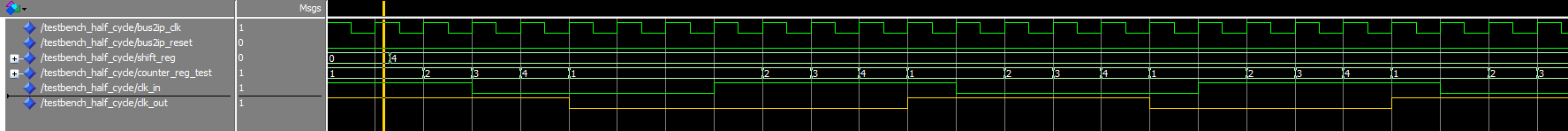

以下の図では、ロジックの動作が遅れている状態で、入力信号のリアルタイムで40 nsの位相シフトがどのように実行されるかを確認できます。

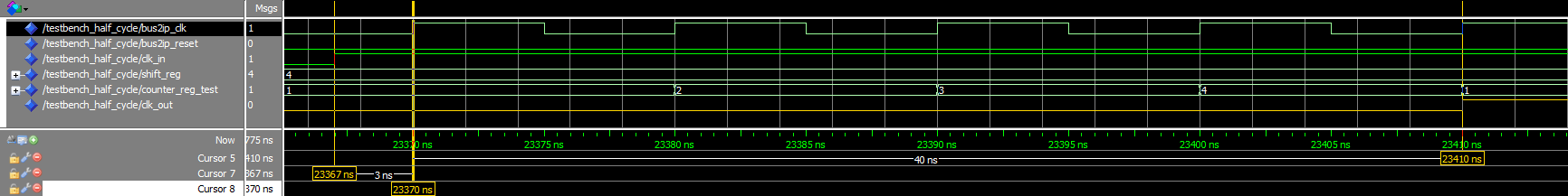

以下は、調整可能な信号と基準周波数が非同期の場合の状況のデモンストレーションです。

この状況を分析し、独自の結論を引き出すことをお勧めします。

次の記事では、このコードに新しい機能を追加することで、あなたのコメントとコメントを聞いてうれしいです。

ご清聴ありがとうございました。