レトロコンピューティングは異なります。 誰かが古代のプロセッサーのキログラムを集め、誰かがソ連のEUコンピューターを復元し、誰かがまだ液体窒素でCeleronを加速させます。だけでなく)。

マックス、何?

数字なしの

アルテラMAX (Multiple Array matriX)は、アルテラの一連の古代CPLDです。 このシリーズは1993年(20年以上前!)に始まり、現在は生産されていませんが、MAX II、MAX V、さらにはMAX 10シリーズに完全に置き換えられています。 MAX9000、次に「洗練された」MAX5000および「安価な低電圧」MAX3000。 次に、JTAG、低電力および低電圧バージョンなどに異なる文字S、E、Bを追加しました。一般的には、ドキュメントを参照してください。

J7000ポートの存在によって区別される

MAX7000Sのバージョンに興味があります。つまり、組み込みIEEStdインターフェースを介して「システムのプログラミング」の可能性を実装します。 1149.1ジョイントテストアクショングループ(JTAG)。

ちなみに、最初のMAX7000(Sなし)は特別なハードウェアプログラマでプログラムされており、DIYアプリケーションには実際には適していません。

アルテラUP1

アルテラはその製品を宣伝するために、シンプルでエラーのない方法を選択しました。1997年に

アルテラ大学プログラムを発表し、デバッグ料金を(アメリカの)大学に安く分配し始めました。 このボードは、アルテラUP1(University Programmから)と呼ばれます。 少し後に、2番目の改訂版がリリースされました-アルテラUP2で、配線がわずかに変更され、より容量の大きいFLEXチップがはんだ付けされました(それより少し低い)。

このボードに関するWebArchiveからの

リンク 。 (「親」サイトはすでに削除されています。)

アルテラのアイデアは成功したと言わなければなりません。 数十の大学が、このコースで「デジタルエレクトロニクスの高速開発」などのコースの実験室作業を行っています。 「Altera UP1」と「UP2」をグーグルで検索すると、ビデオコースも含め、多数のリンクが提供されます。

最も包括的なリソースの1つ:

users.ece.gatech.edu/~hamblen/ALTERA/altera.htm別のレビュー:

www.pyroelectro.com/tutorials/up22000年代初頭のこのボードの人気は非常に高かったため、このボード(Google Altera UP1の本)を取り上げた本がいくつか出版され、James O. HamblenとMichael D. Furmanの本「

Rapid Prototyping of Digital Systems 」このボードは、ドキュメントの拡張版と見なすことができます。 (希望する人は2回のクリックで見つけることができます)。 ちなみに、この本は何度か再版に耐えましたが、エディション3(SOPCエディション)からは、引き出しにも愛されているTerasic DExボードに基づいていますが、レトロな接頭辞には該当しません

最後に、2010年代には理事会は完全に古くなり、大学から償却され始め、ばかげたお金でe-bayに登場し始めました。実際、このような理事会がいくつか購入されました。 軟膏にハエがあります-残念ながら、学生(アメリカ人も)は正確ではないので、そのような中古のボード上の叩かれたI / Oピンは珍しくなく、CPLD記録リソースは消耗します。 したがって、チップはわずかに燃えている可能性があります。PLCC84ソケットにあるため、すぐに交換することをお勧めします。

ディープグーグルは、日本からポーランドまで、さまざまな国の大学のリソースへのリンクを提供します。これは、理事会の広がりを示しています。 UP1ボードがロシアでそれほど広く使用されているかどうかは確かではありませんが、サンクトペテルブルクLIAPのウェブサイト(古い名前はご容赦ください)に、いくつかの実験用のボードの説明が記載さ

れたロシア語のマニュアルがありました。 他の大学でこのボードを使用している人がいたら、私に知らせてください、面白いです。

次に、ボード自体について少し説明します。 CPLD EPM7128Sに加えて、古いFPGA FLEX 10Kチップもはんだ付けされており、コンフィギュレーションメモリ用のDIP-8パネルがありますが、何らかの理由でEPC1チップがパッケージに含まれていません(おそらく使い捨てであるため)。 FLEX 10Kチップは、特にアルテラのUP2ボードであるEPF10K70で、現代の標準でもかなりまともです。 通常どおり、電源安定装置、7セグメントインジケータの2つのペア、25.175 MHzのクォーツ、ボタン、スイッチ、LEDのみがあります(点滅可能です!)。 VGAおよびPS / 2マウスソケットはFLEXにはんだ付けされており、ビデオゲームを作成することもできますが、これはFLEXに関するものではありません。

古い豪華なLPTに輝いたJTAG Altera ByteBlasterMV(MultiVoltという言葉のMV)がボードに取り付けられています。 ところで、e-bayを使用する場合は、ByteBlasterの存在が必要です。 確かに、なぜUSBの時代であり、LPTが存在しないのか-明確ではありませんが、完全なセットが必要です。

暖かい5ボルト

「retrocomputing」という言葉が発せられたので、はい、たとえば、BK-0010またはMikroshiに何かを取り付けるなど、レトロなコンピュータに統合するためにそれを適用するという点でMAX7000Sへの注意が正確に生じたことを認めなければなりません。 そして、ここでの関心の理由は非常に単純です:5ボルトTTL。 時代が変わって低電圧の進行を止めることはできないことは明らかですが、レトロなものと進行中のもの、mmmm ...は互換性がありません...

いずれにせよ、5ボルトCPLDとFPGAは事実上消滅しています。 MAX7000Sファミリの使用は推奨されておらず、競合するザイリンクスXC9500シリーズ(XLなし)と同様に使用できなくなりました。 新しいCPLDはすでに「5ボルト耐性」です。つまり、せいぜい5ボルトの入力で燃えませんが、出力はまだ3.3ボルトです。サイト6502.orgには、一部の古いプロセッサが3.3ボルトピンで動作しないという情報がありました。

MAX7000Sはe-bay / aliexpressで購入することができますが、高価ではありませんが、これらは在庫の残り物または率直に使用されるチップです。 かなり傷のあるケースPLCC84を受け取ったが、5個注文されたものの、6個だった。

すべての設備を備えたプログラミング

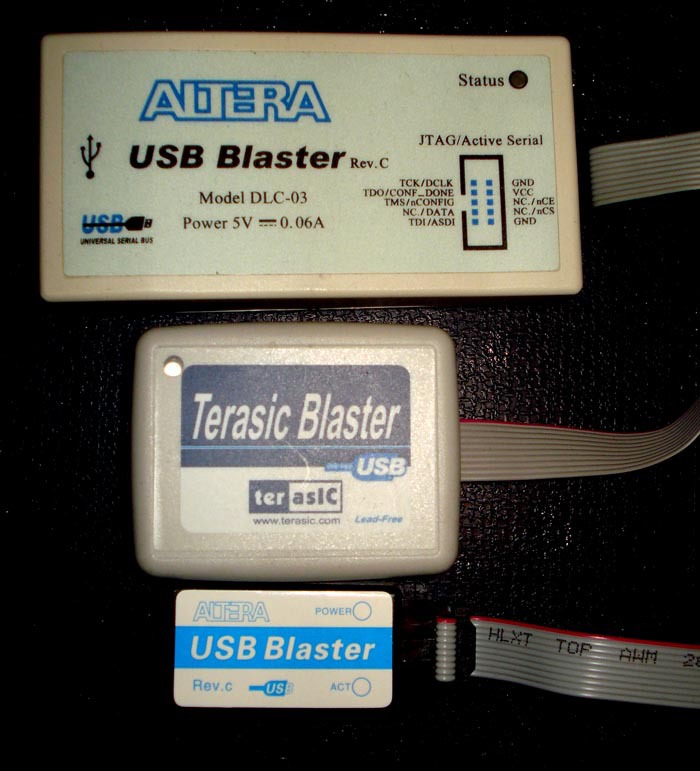

アルテラUP1コースでは、古代のMAX + PLUS IIプログラムを使用してプログラムし、2I-NOTおよびDフリップフロップから回路を残酷に引き出し、LPTポートでアルテラByteBlasterプログラマをフラッシュすることをお勧めします。 これはもちろん素晴らしいことですが、レトロコンピューティングとマゾヒズムを混同しないでください。 各ダクトはQuartus IIで展開され、USB Blasterを備えています。 そうでない場合は、価格が大幅に下がったため、aliexpressのUSB-Blasterクローンの価格は5ドル未満であり、購入をお勧めします。 繰り返しになりますが、DE2などに役立ちます。 (ブラスターについては後述します)。

Quartus IIに関しては、最新バージョンはMAX7000S 13.0のサポートであり、Web Editionは非常に適しています。たとえば、コンパイラがマルチコアをサポートしないなど、少しのカット機能がありますが、これは重要ではありません。 著者は通常、Quartus II 11.0 SP1を展開し、すべてが機能します。

そのため、(ほぼ)現代のQuartus IIで、現代のVHDLでプログラムし、(ほぼ)現代のUSB-Blasterを介してフラッシュします。 そして、レトロなMAX7000Sではこれがすべてです。 彼らが言うように、ハードウェアはレトロであり、ソフトウェアは快適さを備えています。

ネットワーク上のCPLD / FPGAプログラミングに関する記事は多数あります。たとえば、

FPGAハブの

we.easyelectronics.ruには多数の記事があり、死にかけているHabrにはほぼ12の記事がありました。 たとえば

、火星探査機プロジェクトの委員会はイデオロギー的に近いが、そこではCPLDだけが新しい。 したがって、火星探査機のチュートリアルは非常に便利です。

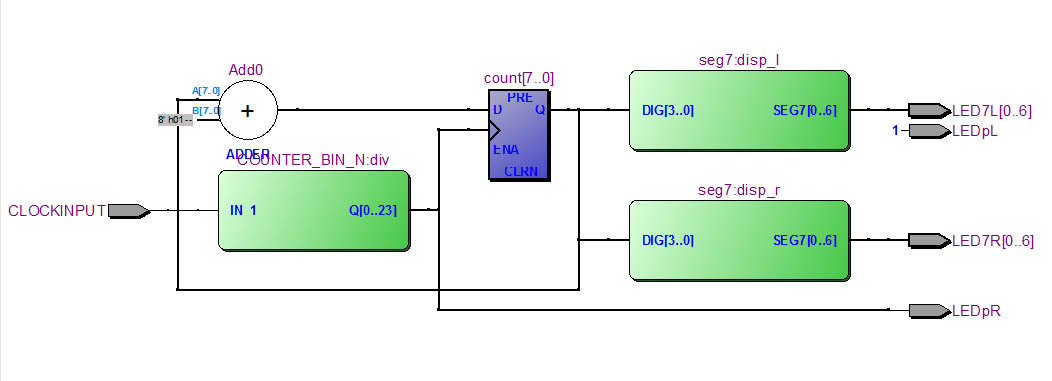

このプロジェクトは特別なものではありません。ボードに既にはんだ付けされているため、7 LEDディスプレイを備えた16進タイマーを作成します。 さらに、小数点をフラッシュします。 CPLDのリソースは非常に限られており、MAX7128Sには128個のマクロセルしかないため、結果のRTLを確認し、使用されているリソースの量に注意を払って常に確認します。

まず、1秒程度の蛇行を取得する必要がありますが、必ずしもそうとは限りませんが、これはデモです。 クォーツから25.175MHzを分周するには、かなり大きな変換係数を持つカウンターが必要です。 たとえば、2 ^ 24 = 16777216で除算して、約1.5ヘルツの周波数を取得できます。 Quartusは1つの入力に定数「1」が適用された巨大な24ビット加算器を生成するため、従来の同期+1カウンターはここでは適していません。 スズ。 24個のセル、いわゆるリップルカウンターを使用して、Dトリガーのチェーンから通常のディバイダーを作成します。 Grammar-design-naziは、これは悪いスタイルだと言います。クロックパルスはグローバルブロックを通過する必要があり、カウンターは同期する必要があります。 これに簡単に答えます-PLLを与えるか、そのような高周波水晶を入れないか。

トリガーの長いチェーンを生成するには、VHDL GENERATEコンストラクトを使用します。 これは、VHDL言語の非常に偽装されたマクロ演算子であり、それを使用して面白いことを行うことができますが、すべては簡単です。

カウンターlibrary ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity D_FF is

トップレベルの設計は非常に原始的です。 ここでは、加算器を使用して受信したRTL実装に恐怖を

覚えるために純粋に

隣接する、古典的な8ビットカウンターを

作成します。 しかし実際には、すべてがそれほど悪くなく、カウンターは正確に8つのマクロセルを消費しますが、論理ブロック内のマクロセルの標準的な論理部分に収まるものの、加算器は印象的です。 コンパイラオフセット。

トップレベル library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; entity UP1TEST is port ( CLOCKINPUT : in std_logic; LEDpL : out std_logic; LEDpR : out std_logic; LED7L : out std_logic_vector(0 to 6); LED7R : out std_logic_vector(0 to 6) ); end entity UP1TEST; architecture rtl of UP1TEST is signal COUNTER : std_logic_vector(7 downto 0); signal SLOWCLOCK : std_logic; signal divider : std_logic_vector(0 to 23); begin

7セグメントデコーダーは問題を引き起こさず、LED用の正直なウォーム5ボルトピンを備えた通常の論理回路に合成されますが、各ピンのマクロセルを消費します。

7-LEDデコーダー library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity seg7 is port ( DIG : in std_logic_vector(3 downto 0); SEG7 : out std_logic_vector(6 downto 0)); end entity seg7; architecture rtl of seg7 is begin with DIG select SEG7 <= "1001111" WHEN "0001",

結果:

週末のピンを結ぶことを忘れないでください。 割り当てには、Pin Plannerエディターを使用できますが、テキストの.QSFファイルをハードコア編集できます。 おそらく微妙なのは1つだけです。TOまたはDOWNTOの宣言に依存する配列内のビットの順序です。 ここでは、カウンタービットとの互換性のために入力がDOWNTO側に移動し(DOWNTOの右側に最下位ビットがある)、ドキュメントとの互換性のために7セグメントインジケーターへの出力がTOであることがわかります。 また、それを下に置くこともできますが、その後、ピン番号を再定義する必要があります。

QSF #------------------------------------------------- -------------------------#

#

#Quartus II

#バージョン11.0ビルド208 2011年3月3日Service Pack 1 SJ Web Edition

#作成日= 23:59:49 2015年7月10日

#

#------------------------------------------------- -------------------------#

#

#注:

#

#1)割り当てのデフォルト値はファイルに保存されます:

#UP1-TEST_assignment_defaults.qdf

#このファイルが存在しない場合は、ファイルを参照してください:

#assignment_defaults.qdf

#

#2)アルテラは、このファイルを変更しないことをお勧めします。 これ

#ファイルはQuartus IIソフトウェアによって自動的に更新されます

#また、加えた変更は失われるか上書きされる可能性があります。

#

#------------------------------------------------- -------------------------#

set_global_assignment -name FAMILY MAX7000S

set_global_assignment -name DEVICE "EPM7128SLC84-7"

set_global_assignment -name TOP_LEVEL_ENTITY UP1TEST

set_global_assignment -name ORIGINAL_QUARTUS_VERSION "11.0 SP1"

set_global_assignment -name PROJECT_CREATION_TIME_DATE "2015年7月10日23:59:49"

set_global_assignment -name LAST_QUARTUS_VERSION "11.0 SP1"

set_global_assignment -name ERROR_CHECK_FREQUENCY_DIVISOR "-1"

set_global_assignment -name MAX7000_DEVICE_IO_STANDARD TTL

set_global_assignment -name RESERVE_ALL_UNUSED_PINS_NO_OUTPUT_GND "AS INPUT TRI-STATED"

set_global_assignment -name OPTIMIZE_HOLD_TIMING OFF

set_global_assignment -name FITTER_EFFORT "STANDARD FIT"

set_location_assignment PIN_83 -to CLOCKINPUT

set_location_assignment PIN_58 -to LED7L [0]

set_location_assignment PIN_60 -to LED7L [1]

set_location_assignment PIN_61 -to LED7L [2]

set_location_assignment PIN_63 -to LED7L [3]

set_location_assignment PIN_64 -to LED7L [4]

set_location_assignment PIN_65 -to LED7L [5]

set_location_assignment PIN_67 -to LED7L [6]

set_location_assignment PIN_68 -to LEDpL

set_location_assignment PIN_69 -to LED7R [0]

set_location_assignment PIN_70 -to LED7R [1]

set_location_assignment PIN_73 -to LED7R [2]

set_location_assignment PIN_74 -to LED7R [3]

set_location_assignment PIN_76 -to LED7R [4]

set_location_assignment PIN_75 -to LED7R [5]

set_location_assignment PIN_77 -to LED7R [6]

set_location_assignment PIN_79 -to LEDpR

set_global_assignment -name VHDL_FILE counter.vhd

set_global_assignment -name VHDL_FILE seg7.vhd

set_global_assignment -name VHDL_FILE "UP1-TEST.vhd"

結果:論理セル。 47/128(37%)

MEの処分に関する報告 + ------------------------------------------------- -------------------------------------------------- ------------------------ +

; エンティティごとのフィッターリソース使用率。

+ ---------------------------------- + ------------ +- ----- + -------------------------------------------- --------- + -------------- +

; コンパイル階層ノード。 マクロセル ピン; 完全な階層名。 ライブラリー名;

+ ---------------------------------- + ------------ +- ----- + -------------------------------------------- --------- + -------------- +

; | UP1TEST; 47; 21; | UP1TEST; 仕事;

; | COUNTER_BIN_N:div | ; 24; 0; | UP1TEST | COUNTER_BIN_N:div; 仕事;

; | D_FF:\ G_1:0:D_Flip_Flop | ; 1; 0; | UP1TEST | COUNTER_BIN_N:div | D_FF:\ G_1:0:D_Flip_Flop; 仕事;

; | D_FF:\ G_1:10:D_Flip_Flop | ; 1; 0; | UP1TEST | COUNTER_BIN_N:div | D_FF:\ G_1:10:D_Flip_Flop; 仕事;

; | D_FF:\ G_1:11:D_Flip_Flop | ; 1; 0; | UP1TEST | COUNTER_BIN_N:div | D_FF:\ G_1:11:D_Flip_Flop; 仕事;

; | D_FF:\ G_1:12:D_Flip_Flop | ; 1; 0; | UP1TEST | COUNTER_BIN_N:div | D_FF:\ G_1:12:D_Flip_Flop; 仕事;

; | D_FF:\ G_1:13:D_Flip_Flop | ; 1; 0; | UP1TEST | COUNTER_BIN_N:div | D_FF:\ G_1:13:D_Flip_Flop; 仕事;

; | D_FF:\ G_1:14:D_Flip_Flop | ; 1; 0; | UP1TEST | COUNTER_BIN_N:div | D_FF:\ G_1:14:D_Flip_Flop; 仕事;

; | D_FF:\ G_1:15:D_Flip_Flop | ; 1; 0; | UP1TEST | COUNTER_BIN_N:div | D_FF:\ G_1:15:D_Flip_Flop; 仕事;

; | D_FF:\ G_1:16:D_Flip_Flop | ; 1; 0; | UP1TEST | COUNTER_BIN_N:div | D_FF:\ G_1:16:D_Flip_Flop; 仕事;

; | D_FF:\ G_1:17:D_Flip_Flop | ; 1; 0; | UP1TEST | COUNTER_BIN_N:div | D_FF:\ G_1:17:D_Flip_Flop; 仕事;

; | D_FF:\ G_1:18:D_Flip_Flop | ; 1; 0; | UP1TEST | COUNTER_BIN_N:div | D_FF:\ G_1:18:D_Flip_Flop; 仕事;

; | D_FF:\ G_1:19:D_Flip_Flop | ; 1; 0; | UP1TEST | COUNTER_BIN_N:div | D_FF:\ G_1:19:D_Flip_Flop; 仕事;

; | D_FF:\ G_1:1:D_Flip_Flop | ; 1; 0; | UP1TEST | COUNTER_BIN_N:div | D_FF:\ G_1:1:D_Flip_Flop; 仕事;

; | D_FF:\ G_1:20:D_Flip_Flop | ; 1; 0; | UP1TEST | COUNTER_BIN_N:div | D_FF:\ G_1:20:D_Flip_Flop; 仕事;

; | D_FF:\ G_1:21:D_Flip_Flop | ; 1; 0; | UP1TEST | COUNTER_BIN_N:div | D_FF:\ G_1:21:D_Flip_Flop; 仕事;

; | D_FF:\ G_1:22:D_Flip_Flop | ; 1; 0; | UP1TEST | COUNTER_BIN_N:div | D_FF:\ G_1:22:D_Flip_Flop; 仕事;

; | D_FF:\ G_1:23:D_Flip_Flop | ; 1; 0; | UP1TEST | COUNTER_BIN_N:div | D_FF:\ G_1:23:D_Flip_Flop; 仕事;

; | D_FF:\ G_1:2:D_Flip_Flop | ; 1; 0; | UP1TEST | COUNTER_BIN_N:div | D_FF:\ G_1:2:D_Flip_Flop; 仕事;

; | D_FF:\ G_1:3:D_Flip_Flop | ; 1; 0; | UP1TEST | COUNTER_BIN_N:div | D_FF:\ G_1:3:D_Flip_Flop; 仕事;

; | D_FF:\ G_1:4:D_Flip_Flop | ; 1; 0; | UP1TEST | COUNTER_BIN_N:div | D_FF:\ G_1:4:D_Flip_Flop; 仕事;

; | D_FF:\ G_1:5:D_Flip_Flop | ; 1; 0; | UP1TEST | COUNTER_BIN_N:div | D_FF:\ G_1:5:D_Flip_Flop; 仕事;

; | D_FF:\ G_1:6:D_Flip_Flop | ; 1; 0; | UP1TEST | COUNTER_BIN_N:div | D_FF:\ G_1:6:D_Flip_Flop; 仕事;

; | D_FF:\ G_1:7:D_Flip_Flop | ; 1; 0; | UP1TEST | COUNTER_BIN_N:div | D_FF:\ G_1:7:D_Flip_Flop; 仕事;

; | D_FF:\ G_1:8:D_Flip_Flop | ; 1; 0; | UP1TEST | COUNTER_BIN_N:div | D_FF:\ G_1:8:D_Flip_Flop; 仕事;

; | D_FF:\ G_1:9:D_Flip_Flop | ; 1; 0; | UP1TEST | COUNTER_BIN_N:div | D_FF:\ G_1:9:D_Flip_Flop; 仕事;

; | lpm_counter:count_rtl_0 | ; 8; 0; | UP1TEST | lpm_counter:count_rtl_0; 仕事;

; | seg7:disp_l | ; 7; 0; | UP1TEST | seg7:disp_l; 仕事;

; | seg7:disp_r | ; 7; 0; | UP1TEST | seg7:disp_r; 仕事;

+ ---------------------------------- + ------------ +- ----- + -------------------------------------------- --------- + -------------- +

ファームウェア

CPLD MAX7128Sファームウェアは問題を引き起こしません; Quartus IIの観点とアルテラUP1ボードの観点の両方から、標準の

アルテラByteBlasterMVを

アルテラUSB Blasterに置き換えることはスムーズに行われます。 JTAGコネクタのピン配列はまったく同じで、VCCピンはJTAGポートの電圧を示します。 実際、それがByteBlasterMVがMulti Voltプレフィックスを付けていた理由です。 ByteBlasterMVから継承したさまざまな電圧のUSB Blasterで動作する機能。

Altera Byte Blasterプログラマーとそのクローンは、多くの詳細に書かれています。

最初の2つはほぼ標準のアルテラUSB Blasterであり、Terasic(または理解できるクローン)は一般にライセンスされているようです。 ご存じのように、「クラシック」USB Blasterは、

マニュアルに記載されているスキーム「FT245BM + CPLD + buffer」に従って組み立てられ

ます 。

後者は本当の中国の奇跡です(より正確には、日中)。 これは

、安価なPIC18F14K50上のFT245BM + CPLD

エミュレータです。 それでも、Quartus IIはこの「偽物」をネイティブUSB Blasterとして認識し、JTAGを介したファームウェア機能が動作します。 独自のFTDI FT ProgでさえFT245BMチップを見つけて、そこから何かを読み取るのは驚くべきことです。

以下は、この中国クローンエミュレータの内部の説明です。

おわりに

だから、私たちは学生の靴にかかっていた〜2007、および同時にCPLDファームウェアにVHDLとUSB Blasterを使用していました。 このボードはCPLDコースに参加するのに非常に便利です。LCExpress CPLDおよびFPGAボードと競合します。これらのボードはaliexpressで詰まっており、高価でない場合は購入する価値があります。 それに関する文献とコースは膨大です。 このボードは標準のTTL 5ボルトで動作し、古いデバイスとよく合います。 在庫MAX7128Sを購入することを忘れないでください-彼らはリソースは永遠ではありません。

次のパートでは、MAX7128Sを互換性のあるAtmel ATF1508ASに置き換えて、何が起こるかを確認します。