みなさんこんにちは!

初心者の開発者は、特定の言語の真剣な研究のためにどのような文学を読むべきかをあまりよく知らないことがあります。

FPGA(FPGA)開発は単なる言語ではありません。 これは非常に膨大な領域で、落とし穴とニュアンスが非常に多くあります。

この記事には以下が含まれています。

- 初心者FPGA開発者が学ぶべきトピックのリスト

- 各トピックに関する推奨文献

- テスト問題と実験室作業のセット

- 古典的な初心者のバグ(およびトラブルシューティングのヒント)

猫へようこそ!

知って必要なこと

デジタル回路

必要です:

- 基本的なデジタルノード(AND / OR / NOT論理要素、エンコーダー、マルチプレクサー、加算器など)を知っている

参照 :

テストの質問 :

- デジタル回路はアナログ回路とどう違うのですか?

- 基本的なデジタルノードとは何ですか? それらのうち、出力は入力のみに依存しますか?

- マルチプレクサとは何ですか? プリミティブAND / OR / NOT要素の4-in-1マルチプレクサーダイアグラムを描画します。

- 式の真理値表を作成します: X = A or(B and C)or D.

HDL構文

これには以下が含まれます:

- HDL言語の合成コンストラクト(構文)の知識

- HDL言語を使用して基本的なデジタルノードを記述する方法に関する知識

- HDLコードのこの部分が(基本的なデジタルノードの側から)何を変えているかを理解する

- 正しい動作を得るためにHDL言語で書く能力

HDL言語として、最初に

Verilogの最も基本的な構造を学習し、次に

SystemVerilogに切り替えることをお勧めします。

参照 :

テストの質問 :

- ブロッキング割り当ては、ノンブロッキングとどのように違いますか? 一方を使用する価値がある場合、もう一方を使用する価値がある場合

- 次の3つの説明に違いはありますか? もしそうなら、それはどのように現れますか?

// code 1: assign a = b + c; // code 2: always @( b or c ) begin a = b + c; end // code 3: always @( * ) begin a = b + c; end

テストタスク :

1.次のコードの基本的なデジタルノードの図を作成します。

非表示のテキスト module test( input clk_i, input a_i, input [2:0] b_i, output reg x_o ); reg [7:0] cnt = 8'd0; reg [7:0] cnt2; wire c; reg d; always @( posedge clk_i ) cnt <= cnt + 1'd1; always @(*) begin cnt2 = cnt + 1'd1; end assign c = ( cnt < 8'd5 ) && ( a_i == 1'b0 ); always @( posedge clk_i ) begin d <= c; x_o <= c ? ( d ) : ( cnt2[ b_i ] ); end endmodule

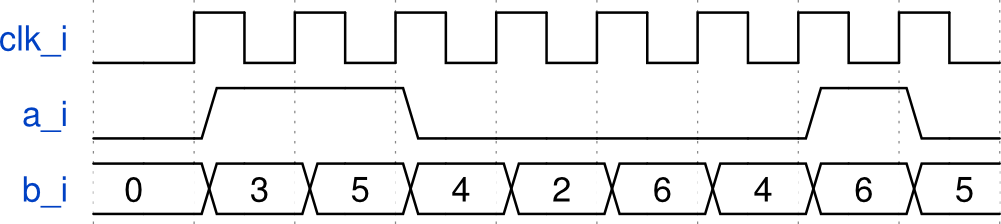

2.次の入力アクションの下で、項目1からの回路の動作(つまり、すべての「変数」の状態)を描画します。

非表示のテキスト時間は、WaveDromオンラインエディターを使用して描画されます。

3.赤、赤、黄、緑、緑の点滅、黄、赤の順序で赤、黄、緑のライトを点灯する信号機を制御するモジュールを作成します。 信号機の燃焼時間と緑色のライトの点滅期間を指定するパラメーターは、モジュールパラメーターです。 時間は

clk_iのクロックサイクル数で設定されます。

モジュールインターフェイス:

非表示のテキスト module traffic_light( // c input clk_i, // input rst_i, // 1, , 0 — output red_o, output yellow_o, output green_o );

HDLコードのシミュレーションと検証

必要です:

- Verilog'aおよびSystemVerilog'aの非合成コンストラクトを知っている

- 簡単なテストベンチを作成し、シミュレーターで実行できるようにします(ModelSimなど)

- 「完璧な」テストベンチの配置方法を理解する

参考文献 :

ビデオチュートリアル :

テストの質問 :

- 機能はタスクとどう違うのですか?

- 5ステージRISCプロセッサの最も単純なHDLモデルを書いたと想像してください。 どのように検証しますか? ( 複雑さの増加の問題 )。

- キューとメールボックス (SystemVerilog言語のデータ型)の違いは何ですか?

- 機能シミュレーションと一時シミュレーションの違いは何ですか? いつどれを使うべきですか?

FPGA

必要です:

- FPGAが構成する基本要素を知る

- FPGAでの開発ワークフローの仕組みを理解する

- FPGAのどの操作が安価で、どの操作が(周波数とリソースにおいて)直感的に想像できる

私は

アルテラのチップを使用しているため、以降、ファミリおよびユーティリティの名前はこのベンダーのものになります。

ザイリンクスに関する同様の文献を知っている場合-個人的なメッセージやコメントを書いてください-間違いなく記事に追加します。

参考文献 :

ビデオチュートリアル :

テストの質問 :

- FPGAとASICの違いは何ですか? FPGAはどのブロックで構成されますか(または構成される可能性がありますか)?

- FPGAを使用するのが適切な(経済的に実行可能な)タスクと、どのMCUおよびCPUのタスクの範囲を概説してみますか?

- どのハードウェアブロックを知っていますか? 彼らは何のために使われますか? (ここでハードウェアブロックとは、 ハードIPを指します )。

- Yファミリは、3つの入力と1つの出力を持つLUTを使用します。 assign eq =(a == b)を計算するために必要なLUTの最小数は何ですか。 aとbが32ビットの正の整数である場合 LUTに4つ(5つ、6つ)の入力がある場合

- 16ワードのシングルポートメモリを作成する必要があります。 各ワードは100ビット幅です。 いくつのM9Kブロック(9216ビット)が占有されますか? 私たちは、Cyclone IIIの下でプロジェクトを行っていると考えています。 (*)

(*)で示される事項では、もちろん、すべてを暗記する必要はありませんが、データシートを使用できます。

同期設計とタイミングに関連するすべて

必要です:

- 同期設計の原理を知っている

- これらのスキームまたは他のスキームがどのようなマイナスの結果をもたらすかを知る

- 制約の概念を持っている

参考文献 :

テストの質問 :

- タイミング制約とは何ですか? それらはどこで説明され、何のために(何のために)使用されますか? 記載されていない場合はどうなりますか?

- クロックドメインクロッシングとは何ですか? どのように、いつそれを実装しますか?

- 同期リセットと非同期リセットの違いは何ですか? 同期リセットの入力に非同期リセットが行われるとどうなりますか?

- ラッチとは何ですか(ラッチ、ラッチ)? ラッチを使用した結果はどうなりますか? ラッチを作成するコードの例を示します。

- 組み合わせループとは何ですか? 組み合わせループを使用した結果はどうなりますか?

- 準安定性とは それを達成する方法は? 長所と短所は何ですか?

- グリッチとは何ですか? これに対処する必要がありますか? もしそうなら、どこで、どのように?

- Dトリガーのセットアップ時間/ホールド時間とは何ですか?

CAD

必要です:

- プロジェクトを作成できる

- I / Oピンと定数を記述できる(少なくとも単純な状況では、複雑なI / Oインターフェイスなしで)

- アセンブリレポートとは何か、各レポートに含まれる情報を知る

- ハードウェアデバッグツールを使用できる

- Timing Analysis Tool( STA )を使用できるようになる

- ベンダーが提供する既製のIPコア/モジュール(FIFO、RAM、FFT、DDR、イーサネットなど)と、それらをプロジェクトに追加する方法を知っている

参照:ビデオチュートリアル :

テストの質問 :

- 「プロジェクト全体をビルドする」ボタンをクリックして完成したバイナリファイルを取得するアセンブリの段階は何ですか? 各段階で何が起こりますか?

- CADがプロジェクトを指定された制約(制約)に入れることに成功したかどうかを確認する方法は?

講義と研究室

2学期の間、私はサンクトペテルブルクの大学の上級生向けにコース「FPGA開発」を教えました。 このコースには、講義と一連の実験室作業の両方が含まれていました。 講義は上記の文献に基づいていました。

コースプラン:

非表示のテキスト : * ? . * ( Quartus ). Verilog: * ( HDL ). * / . * : * . * , / * . * . * . * / . * . * Verilog . * ( +SystemVerilog ): * . . Testbench. testbench. * testbench'. * . . * ( , .. ). * tasks. * . * . * SystemVerilog Assertions. * testbench . * c ( ) .

講義タイトル(2015年):

- FPGAの紹介。

- 内部FPGAデバイス。

- Verilog / SystemVerilogの概要。 さまざまなタイプのロジックの説明の例。

- 同期設計。 簡単なテストベンチを作成します。

- SystemVerilogのFSM、配列、および構造の説明。 メモリ:VerilogおよびMegaWizardを使用した作成。

- DCFIFOの仕組み 静的タイミング分析。 TimeQuest、制約。

- 検証:カバレッジ、アサーション、SystemVerilogインターフェイス

- Avalonファミリーのインターフェース。 IPコア。 Qsys。

- 検証:SystemVerilog OOP、制約付きランダムテスト。

講義スライド非表示のテキスト残念ながら、これらは私が講義をするのを助けたスライドです(すべてのコース情報がスライド上にあるわけではなく、一部はサポートとして使用し、資料はボード上で提供されました)。

隣の写真とはまったく関係のない写真が表示されることがあります(たとえば、講義で行われたテストのタスク)。

実験室の仕事 :

古典的なエラー

記事のこの部分では、初心者の開発者が犯した典型的な間違いについて説明し、それらを修正するためのヒントを提供します。

割り当ての混乱(ブロックと非ブロック)

症状- ブロック割り当てと非ブロック割り当てに関する質問に答える自信がありません(上記を参照)

- 「=」を「<=」 (およびその逆)にランダムに変更し、機能することを期待していることに気づいた

- シミュレーターが奇妙なことを示している場合、Dトリガーがどのように機能するかを理解していることを疑い始めます

- シミュレーション結果は、ハードウェア上で発生していることと安定して一致しません(何かがビートに浮かぶ)

処置 :

- Verilogの資料を理解する(上記の文献を参照)

- シミュレーション結果をハードウェアで合成および実装するものと一致させたい場合は、単純なルールを覚えておいてください:組み合わせロジック( always_comb 、 常に@(*) )を記述するブロックでは、ブロック割り当て( = )のみを使用する必要があります トリガーを記述するブロック( always_ff 、 常に@(posedge clk ...) )では、非ブロッキング割り当て( <= )のみを使用する必要があります。

タイミングの問題

症状- シミュレーション結果がハードウェアで発生することと一致しません

- 鉄は不安定に動作します:干渉がはっきりと見える場合があります(VGAなど)

- 「シグナリング手順を追加し、その後、回路が正常に動作しなくなった後、シグナリング手順を削除しましたが、すべて正常です」

処置 :

- 必要なすべての制約(少なくとも* .sdcファイルの使用クロック周波数)を規定し、このファイルをプロジェクトに接続します

- プロジェクトを再コンパイルします。 TimeQuestに移動して、ネガティブスラックがあるかどうかを確認し、そうである場合は、なぜこれが起こっているのかを調べます(Quartusの設定を変更するか、コードを書き直す必要があります)。

SignalTapに異常がある場合は、「ゲーティング」周波数で撮影した信号が同期していることを再確認してください。

同期設計の原則に準拠していない(非同期)

最初の段落の続きですが、別に強調することにしました。

症状は前の段落と似ています。

何らかの理由で、多くの人がこのようなことをしたいのです:

// BAD EXAMPLE ... input clk_i, ... logic [7:0] sec_cnt; logic [7:0] min_cnt; logic last_sec_value; assign last_sec_value = ( sec_cnt == 8'd59 ); always_ff @( posedge clk_i ) if( last_sec_value ) sec_cnt <= 'd0; else sec_cnt <= sec_cnt + 1'd1; always_ff @( posedge last_sec_value ) min_cnt <= min_cnt + 1'd1;

つまり

clk_iクロックとは異なる信号が、

min_cntトリガーの入力信号として使用されます。 組み合わせ論理(コンパレータ出力)によって形成されます。

またはこのように:

// BAD EXAMPLE ... input clk_a_i, input clk_b_i, ... logic [7:0] cnt_a; logic [7:0] cnt_b; logic [7:0] sum; always_ff @( posedge clk_a_i ) cnt_a <= cnt_a + 1'd1; always_ff @( posedge clk_b_i ) cnt_b <= cnt_b + 1'd1; always_ff @( posedge clk_b_i ) sum <= cnt_a + cnt_b;

トリガー入力の

合計は、組み合わせクロックの出力を受け取ります。組み合わせロジックの入力は、

異なるクロック信号で駆動されます。

両方の例は

間違っています;絶対にしないでください! これらの例は、同期設計の規則に明らかに

違反しています。

これはすべて、チップが小さく、開発者が最善を尽くして生き残った2000年代に由来すると思います。

ほとんどの場合、低周波数(1 MHzなど)で機能しましたが、トップエンドチップで深刻なことをするチームに参加する場合、そのようなトリックのためにインターンシップから簡単に飛び出すことができます。

処置 :

- プロジェクト全体を調べ、各トリガーに使用するクロッキングブロック(信号)を(紙に)書き留めます。

- この数を最小数に(もちろん合理的な制限内で)減らす方法を理解し、同期設計の規則に従ってコードを修正します。

- プロジェクト全体を調べ、クロックドメインの交差がどのように発生するかを注意深く監視します(つまり、ある周波数から別の周波数にデータが転送されます)。 正しくない場合は修正します。

- 「タイミングの問題」の項目からすべてのステップを完了します。

ハードウェアでの永続的なデバッグ(シミュレーションを無視)

開発が次のような場合、この間違いを犯します。

- HDLファイルの編集

- 完全なプロジェクトのコンパイル

- バイナリをボードにフラッシュする

- SignalTap接続、目的の信号を表示

- エラーの理解、パラグラフ1への移行

なぜこれが悪いのですか:

- SignalTapでは、大規模なプロジェクトがある場合、すべてすべてすべての信号を見ることができません

- 完全なプロジェクトをコンパイルするとき、あなたはあなたの時間、または雇用者の時間をとります。 これにはかなりの時間がかかります。 小さなチップでは5〜10分かかり、その時間にハンマーを使って喫煙/お茶を飲む/キッカーをすることができますが、大規模なプロジェクトではあなたの側に来ます。

- 手元にワーキングボードが必要です

- あなたは、コードの変更が機能するかどうかわからず、他のものを壊さない

処置 :

- プロジェクト全体またはその部分のテストベンチを作成する

- シミュレーションで正しい動作を実現する

- プロジェクトを組み立て、ボードを確認します

ハードウェアで何かが機能しない場合は、次のようにします。

- 上記のポイントを通過します(タイミングと非同期性)

- タイミングに問題がない場合は、これが発生する入力の影響を理解してください

- シミュレーションでこれらの効果を送信し、問題が再現されることを確認してください

- RTLコードのエラーを修正し、シミュレーションとハードウェアをチェックインします

- required :シミュレーションの以前のバージョンがこのエラーをキャッチできなかった理由を結論付ける

症状- 昨日書いたコードの読み取り(解析)に多くの時間を費やしています。

- 多くの場合、同じタイプのコードを記述します(キーボードで最も一般的なキーはCtrl + CおよびCtrl + Vです )

- 同僚が書いたコードを理解することはできません(同じモジュール/ IPコアで一緒に作業する場合)。それはあなたのものです。

処置 :

おわりに

この記事で、FPGAの開発の世界に入るために読んで知っておくべきことを明らかにしたことを願っています。

もしあなたが:

- 上記のテストの質問に簡単に答えることができます(もちろん暗記なしで)

- 適切なラボを決定する

- 「古典的な間違い」を取り除く

- githubで1-2プロジェクトを作成し、ハードウェアでテストします。 (できれば、点滅するLEDや時計よりも複雑です)。

その後、何の問題もなく、真面目な会社のジュニアポジションに応募できます。

もちろん、このパスを1つの週末に習得することはできません。 1か月以上かかる場合がありますが、学生のFPGA開発からプロフェッショナルに切り替える場合は、この方法で行う必要があります。

ご清聴ありがとうございました!

いつものように、私はコメントや個人的なメールで質問やコメントを喜んでいます。

PS

時々、彼らは午後に私に手紙を書きます:

こんにちは

私はそのような大学とそのような大学の3(4、5)コースの学生です。

私はFPGAで書くというアイデアが好きで(並行性、好きなことができます、何とか何とか)、Javaが好きです(Android用のシンプルなアプリケーションを作成しました)。 私はこれのいくつかを多かれ少なかれ真剣にやりたいです。 何を学ぶことを勧めますか?

ほとんどの場合、2つのリファレンス(

FPGAと

JAVA )を見て、独自に結論を出すことをお勧めします。