いずれかのデバイスでは、停電や短期間のシャットダウンが発生した場合に、以前の動作モードを完全に復元する必要が生じました。 もちろん、バックアップ電源を設置することもできましたが、その使用は、いわば、デバイスの設計機能によって制限されていました。 その結果、復元に必要な多くの値をメモリに書き込むことが決定されました。 書き込みサイクルの数が限られているため、リカバリの値を頻繁に更新するため、フラッシュとEEPROMの使用は考慮されていませんでした。

私の意見では、現時点では、このような場合に最適なソリューションはFRAMメモリです。 フラッシュに必要なデータを周期的に書き込み、常に新しい値のアドレスをインクリメントすることが可能ですが、この場合、最新の値へのポインターを保持するか、フラッシュを完全に読み取って「最新の」データを取得する必要がありました。

Lapis Semiconductorには、I2CまたはSPIを介して、またはパラレルインターフェイスを介してマスターと通信する3行のFRAMチップがあります。 パラレルインターフェイスに対するシリアルインターフェイスの利点は明らかです。 I2CおよびSPIに関しては、SPIを介したデータ転送速度はI2Cの4倍ですが、この接続での消費はほぼ16倍です。

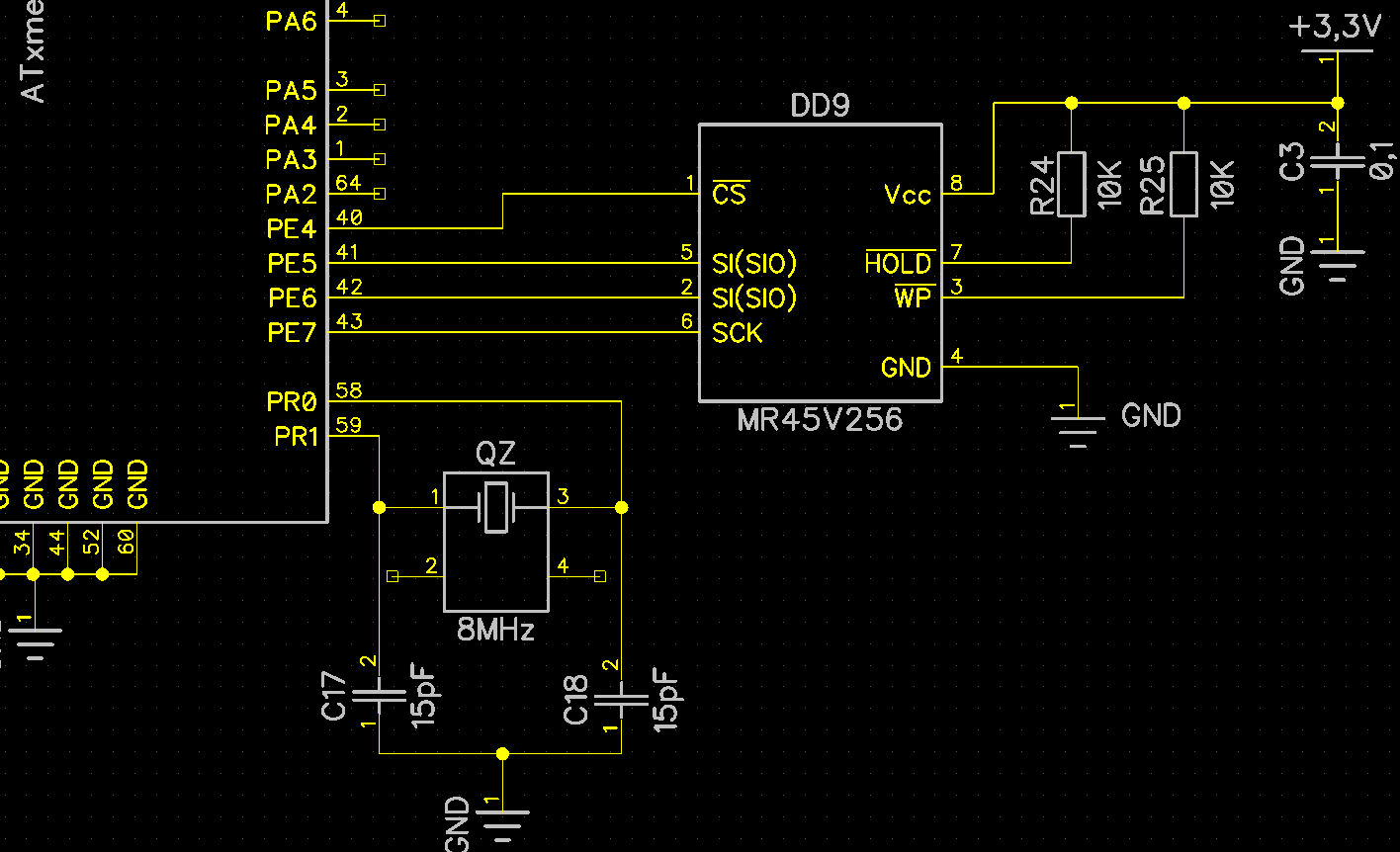

32 KBのメモリとSPIインターフェイスを備えたMR45V256のみが利用可能でした。 必要に応じて32 Kbで十分なので、残りのメモリを使用して、あらゆる種類の技術情報を記録し、オペレーターから受け取ったコマンドを記録します。

FRAMメモリの操作は非常に簡単です。 すべての操作は、CS#スレーブ選択ラインをローに設定することから始まります。 次に、操作コマンドの1つが送信されますが、そのうちの6つだけがあります。

-データの読み取り(READ)

-データ記録(WRITE)

-FRAMステータスレジスタ(WRSR)への書き込み

-FRAMステータスレジスタ(RDSR)からの読み取り

-上書きからのデータ保護の設定(WRDI)

-上書きからのデータ保護の削除(WREN)

上書きに対する保護は、メモリの前半、前半、またはメモリ全体に設定できます。 読み取りおよび書き込みコマンドを使用する場合、コマンドの後に、読み取り/書き込みを開始する16進アドレスを送信する必要もあります。 コマンドとアドレスは一度だけ送信され、後続のマイクロサーキット自体がアドレスをインクリメントし、CS#がHigh状態に転送されるまで後続のすべてのデータを転送します。

メモリへの書き込みを開始する前に、常にステータスレジスタMR45V256の書き込みイネーブルビット(WREN)を設定する必要があります。 そして、その後、書き込みコマンド(WRITE)を送信します。

マスターデバイスはXmegaマイクロコントローラーを使用していました。 Xmega SPIマイクロコントローラーは、他のAtmelマイクロコントローラーのSPIと実質的に違いはありません。 最も顕著な違いはDMAを使用する可能性ですが、この場合に送信される情報の量は多くないため、DMAの使用を拒否しました。 Xmegaは4つのSPI動作モード(モード0、1、2、3)をすべてサポートしています。 MR45V256はモード0とモード3のみをサポートすることに注意してください。

Xmega SPIモジュールは、送信チャネルにシングルレベルバッファリング、受信チャネルに2レベルバッファリングを備えています。 つまり、シフトサイクルが完了するまで、送信用のバイトをSPIデータレジスタに配置することはできません。 データの受信中、次のパッケージを受信する前に、受信したパッケージを考慮する必要があります。 そうしないと、データの最初のバイトが失われます。 したがって、SPIステータスレジスタを制御するために、割り込み時または受信および送信中に作業することをお勧めします。

FRAMには、他のタイプのメモリなどで最初に消去することなくデータを上書きできるため、消去するコマンドはありません。 それでも、FRAM全体を完全に「消去」することが必要になる場合があります。

void FramErase(void) { SPIE_init(); FRAMPORT.OUTCLR = (1<<SPICS);

FRAMを使用する利点について説明する場合、まず第一に信頼性です。 記録サイクルの数は10〜12度です。 メーカーは、情報を失うことなく最大10年間の情報保存を約束します。 同じFLASHと比較して、FRAMは高速で消費電力がはるかに低くなっています。 マイナスのうち、大量のメモリではない場合がありますが、FRAMが通常使用されるタスクを考慮すると、大容量はそれほど重要ではありません。