, TMS320C6678. . — , . DSP. , . DSP - , .

- -

- L1P

- L1D

- L2

- — IDMA

TMS320C66x 3- . . . ; . , , . , . L1. L2 , . . ( ) -.

TMS320C66xx :

- L1P L1D, ;

- L2 ;

- MSM (Multicore Shared Memory), L2 L3;

- L3.

L1 L2 , -, L2 L3. , . TMS320C66x.

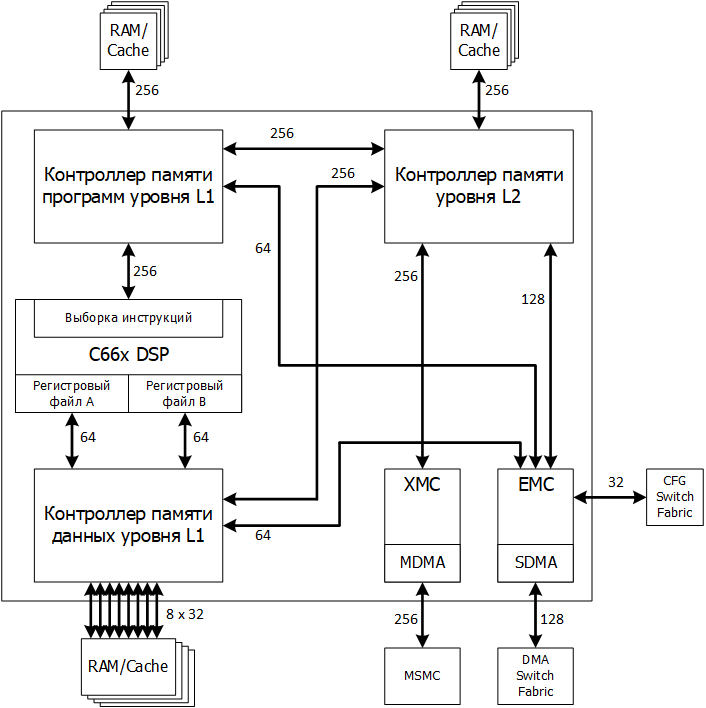

1 — CorePac TMS320C66xx

1 — CorePac TMS320C66xxCorePac TMS320C66x. , 1. – 66, –

, :

- L1 (L1P);

- L1 (L1D);

- L2 (L2);

- (IDMA)

- (EMC);

- (XMC);

.

-

, TMS320C66x, .

. , , L1, . L2 , , , . L3, L4 , , . .

– (temporal and spatial locality) [1]. . , / . / /, , , / .

/, , (cache line). , , , /, , , /. L1P 32 . , , , TMS320C66x L1P .

(direct-mapped cache). , . , , . /, , . (conflict miss), . – - (capacity miss). – (compulsory miss). .

, . , ( – 2 way), 4 ( – 4-way) . , / / , ( — way) . , . , , (Set). , , , . LRU, . .

| way1 | way2 |

|---|

| set1 | line0 | line0 |

| set2 | line1 | line1 |

| set3 | line2 | line2 |

« » (read-allocate cache) – , , / , . ( , ) (write buffer) .

/ (write back cache) , (write hit) / , , (Dirty), .

TMS320C66xx . L2 L1, L1, . , , . L1P . 16 , MAR.

, , MEMORY cmd-.

(cache coherence). () . , , . , , , , .

C66x

EDMA/IDMA. DMA L2 SRAM, L1D- L2 SRAM. DMA L2 SRAM, L2 SRAM, L1D. snooping – . DMA / .

( CSL) :

- DMA , CPU;

- CPU , DMA ;

- DMA L2 SRAM, CPU;

- L2 SRAM , .

. C 1 DMA L2 . DMA L2 2. , , ping-pong . L2 L1 .

2 ping-pong 2 – L2 L1 – . DMA L1D L2, , (invalidate). , . , , DMA , L1D L2 – write back.

- . . Texas Instruments Code Composer Studio . .

L1P

L1 (L1P) . TMS320C6678 32 . L1P . 0, 4, 8, 16 32 . . L1P. L1P , ( ).

L1P . L1P EDMA IDMA. L1P , - .

L1P 0, , L1P 3. L1P . .

L1P . L1P (direct-mapped cache). . , , , .

L1P (freeze mode) . , . L1P . - , «» .

L1P . , , . (invalidation) . , .

, , .

. . . , , , , .

L1P- , ( ). . L1P- L2- . , , . - ( ) - . TMS320C66x , - , . , , , . – , . , L2 , L1P. (L1P miss pipeline).

66 .

, , , , , . - .

, . L1P (static power-down), ; , «» L1P IDLE. (dynamic power-down), SPLOOP. L1P- (feature-oriented power-down), (disabled). L1P , , .

L1P , DMA IDMA. 2 – . . , ( ) ( DMA/IDMA). , L1P L1P .

/ DMA/IDMA . . L1P 16 .

L1D

L1 128 TMS320C6678 32 . L1D -.

L1D- – « » « » (2-way set-associative, read-allocate, write back cache). .

L1D . L1D .

. 32- , , , .

2 —

2 —offset – . , , . 64 offset 6 . .

set – , . set - 5-14 .

Tag , , (way).

- , , . (write back) , . L1D- .

L1D . LRU . . . . , L1D L1P. .

L1D- :

- (invalidation);

- (writeback);

- (writeback-invalidation).

, L1P. L1P L1D ( ), writeback-invalidate, L2-.

L1D- L2, DMA, L1D- , L2. L2 / (snoop-read snoop-write) DMA. snoop-read L2, L2 , DMA (Dirty). L1D L2. snoop-write , L2 , , DMA, L1D-. L1D , .

L1D L2 , L2 () L1D-. L1D L2 , L2 , L1D . L2 , L1D , L1D.

L1D. 8 . – 4 . – , . . , , ; . DMA, – . , , . L1D .

L1D . , , . L1D L2, L2, — L3. 2 , , . , , .

(victim buffer). , , , . , , , . , . . . , L2, (L1D write buffer).

L1D , (L2) . (write buffer). 128 4-, 4 L2 . , . . , , . , , , , .

L2 , , L1. . , . , , . , , 128 , L2 ( ) . . L2. .

, L1P, .

L1D- L1P. L1D , (idle mode). IDLE , ( ) . , L1D, L1P L2 DMA (PDC) «» , DMA . . .

L1D L1D / , . , . ( , DSP IDMA) . . , , , , . .

L2

L2 64 — 4096 TMS320C6678 512 . L2 1 256 . L2 , 4 . 128- . L2 L1D, L1P IDMA .

L2 . .

L2- 4- -. L1 L2- - , . 3 — (offset), (set) (tag). . L2- 128-, 7 . Set . Tag , (Way) , , .

L1. L2- . L1- L2 - , L2- . DSP. XMC.

L2 . , , .

L2- « » . -. CorePac .

, L1.

L2. L1, . L1-.

, . (MAR). . , . , . MAR . , [2].

L1P L1D L2, L2 ( ), L2 MAR- . , « » – L2 L1D ( ). DSP , . L1P , , MAR-.

L1 L2. L2 L1D-. L2 L1P, ( ) - L2 L1.

L1 L2 – snoop-. Snoop-read – – L2, DMA L2 , L1D , L1 L2 , . L2 L1D- , ( , LRU ). Snoop-write – – L2 L2 DMA , L1D-. , , . 256 L2 L1D. .

L2- «» , L1D ( L1P) .

L1 L3 ( L2 ) – victim writebacks – L2 , L2-, , L2-.

XMC L2- MAR.

L2 . – . – , ( CorePac) . . DMA L1PD L2, , DMA (PDC) .

L2 . L2 Retenion Until Access – RTA. «» , . , L2 , .

L2, L1, , . . [2].

— IDMA

DMA – IDMA – , L1P, L1D L2, (CFG). 2 . – L1 L2-. IDMA L1 L2- , . – IDMA CFG-. IDMA .

IDMA 2 . 0 (channel 0) – CFG. 1 (channel 1) . IDMA DMA- DSP- . [2].

— EMC

EMC CorePac . , , .

EMC 2 – CFG DMA «» — Slave DMA – SDMA. SDMA , , DMA ( ), SRIO , . , , .

— XMC

XMC 4 :

- MSMC – MDMA- L2- MSM-;

- , CorePac;

- ;

- (prefetching).

CorePac MSM.

( ) MSM RAM EMIF CorePac.

MPAX. , .

TMS320C66x 32- . 4 . , . , 32- CorePac 36-. 36- 64 .

32- 16 , , , MSM. .

XMC . MPAX, XMC .

MPAX . 16 MPAX 3.

3 — MPAX

3 — MPAXBADDR SEGSZ . 4 4 . . 36- , , , ( ) . , , .

[2]. , , , , .

:

- :

:

- TMS320C66x DSP Cache. User Guide. SPRUGY8. Texas Instruments, 2010

- TMS320C66x DSP CorePac. User Guide. SPRUGW0B. USA. Texas Instruments, 2011