注釈

この記事では、Vivadoの動作モードについて説明します。これにより、接続リストの編集レベル(以降-ネットリスト)でプロジェクトを変更できます。 ECOモード自体、および作業中に表示されるいくつかのニュアンスについて説明します。 デモンストレーションの例が示されており、結果を取得するためのアクションの完全なシーケンスが説明されており、誰でも操作性を確認できます。 この記事は、FPGA開発者、特にLogic Analyzerでプロジェクトを頻繁にデバッグする開発者の「一般的な開発」に役立ちます。 このモードでは、ネットリストを変更するときに実装に費やす時間を文字通りに減らすことができるため、このモードでの作業は、コンパイル時間が数時間(または数十時間)に達する可能性のある大きなクリスタルで作業する開発者に興味があることを願っています数分。

目次

この記事には、ネタバレではない写真がたくさんあります(140枚)。 電話から来る場合は注意してください。

はじめに

多くの場合、講義をしたり、セミナーを実施したりする必要があるとき、私は常にプログラムが示唆するよりも少し多く話そうとします。 そのため、シングルコアZynq-7000Sの使用に関する最後の3つのセミナーでした。 今回は、Vivadoを操作する「隠された」モードのいくつかについて、聴衆がどれだけ知っているかを見るのは興味深いものでした。 質問は非常に簡単でした。「出席者はECOフローモードについて知っていますか?」質問の直後に「手の森」と呼ばれるものが続きましたが、私は特に驚きませんでした。

少なくともVivadoでのこのモードの存在について開発者にいくらか啓発したいという願望は、それでの動作のデモは言うまでもなく、非常に昔に私に現れました。 しかし、何らかの不思議な理由で、MicroBlazeを使用してプロジェクトを構築し、それを操作するためのガイドを作成するように「利用」しました。 ただし、最近のセミナーの後、ECO Flowについての記述が依然として必要であることが明らかになりました。

この記事

の目的は、ザイリンクスが水晶に提供するVivado環境[1]のECOモードの一般的な考え方を示し、実際の例でその動作を示し、「微妙な」ポイントを示し、その長所と短所を分析することです。

この記事で設定される

タスク :

- 可能であれば、ECOモードで動作する可能性のすべて(または少なくともほとんど)を含み、実証するテスト例を開発します。

- プロジェクトを実装します。

- デザインチェックポイントの概念を説明します。

- ECO動作モードへの移行を説明してください。

- ネットリストを変更し、FPGAファームウェアファイルを取得します。

- 行われた変更が正しいことを確認してください。

- プロジェクトの標準的な変更にかかった時間の要約表を作成し、それをECOモードで費やした時間と増分実装と比較します。

残念ながら、かなり「重い」チップ(Virtex UltraScaleなど)で方法論を物理的に検証する機会はありません。 しかし、Artyボード[2]にインストールされた控えめなArtix-7でのテストでの例でさえ、非常に参考になると思います。 執筆の過程では、ECOモード[3]、[4]、[5]を説明するいくつかの基本的な文書に依存します。 Vivadoの使用バージョン(およびドキュメント)は2017.4です。

小さな余談:はい、プロジェクトの作成、MicroBlazeでのプロセッサシステムの構築、IPインテグレーターでの作業、デバッグなどの方法に関するマニュアルには多くの写真と「些細なこと」があります。 経験があり、ECOについて読みたい場合は、第

4章

「ECOモードへの切り替え」に直接進んでください。 MicroBlazeでプロジェクトを構築する方法がわからない場合、IPインテグレーターで働いたことがない、またはステップバイステップの図のスタイルのガイドのように、提示された資料にさらに75分から90分をかけていただければうれしいです。 それでも、だれかがハードウェアで検証してマニュアルを完全に完成させてくれることを願っています。

1. ECO:概要

ECO-エンジニアリング変更命令[6]-これは、元のネットリストへの影響を最小限に抑えて、合成または実装されたプロジェクトであるネットリストに変更を加えることができるモードです。 VivadoにはECOモードがあり、プロジェクトのいわゆるデザインチェックポイントの変更(以下を参照)、変更の実装、変更されたネットリストに必要なレポートの生成、FPGAファームウェアファイルの生成が可能です。

このモードの最も典型的なアプリケーション:

- プロジェクトのデバッグ中のプローブおよびロジックアナライザーの接続ライン(ILA-IntegratedLogicAnalyzer)の変更。 ユーザーは、プロジェクトの完全な再実装を回避しながら、ILAに接続されたラインのセットを変更できます。

- FPGAレッグに接続された回路の再割り当て。 プロジェクト開発者、回路設計者、またはPCB開発者がレッグの割り当てを間違えた場合(たとえば、rxとtxが混同される場合)、FPGAのプロジェクトが既に実装されている場合、この方法でネットリストのポートを再割り当てして、完全な実装(tすなわち、プロジェクトの合成、マッピング、最適化、配置、トレース-マシン時間とリソースのすべての関連コスト)。

- 「What_if?」分析の実行(メモリの内容の編集、LUTの機能の変更、タイミングの改善など)

ECOモードで作業する主なタスクは、プロジェクトのセットアップまたはデバッグの段階で変更を行うときに、時間を節約し、プロジェクトの再実装を回避することです。 多くはECOでも使用されるインクリメンタル実装モードに精通していますが、ECOでは、インクリメンタル実装と比較して、ファームウェアファイルを取得するのが速く、現在のデバッグ反復を実行するのが速いです。

注:ECO操作は、デザインチェックポイントでのみ可能です。2.設計チェックポイント

設計ルートは、合成と実装を含むいくつかのコンポーネントに分かれています。 実装は、さまざまな最適化、配置、トレースのサブステージに分かれています。 設計ルートの中間段階は、設計チェックポイント(DCP)[7]と呼ばれる「コンテナ」に保存されます。 これは、拡張子が「.dcp」のファイルです。 デザインチェックポイントの内容

- dcpファイルを書き込む前に実行されたすべての最適化を含む、現在のネットリスト(デザインルートの段階に依存)。

- プロジェクトに課せられた制約(設計上の制約)。

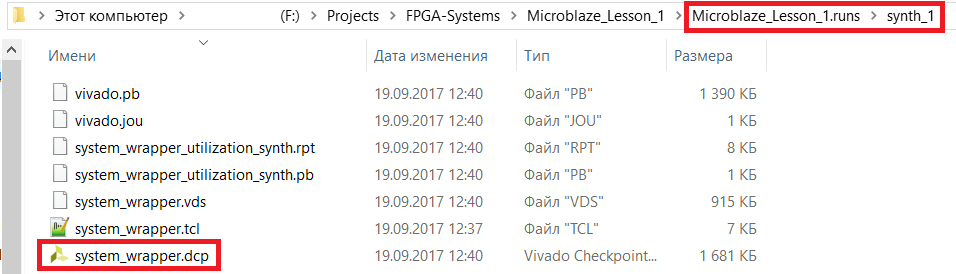

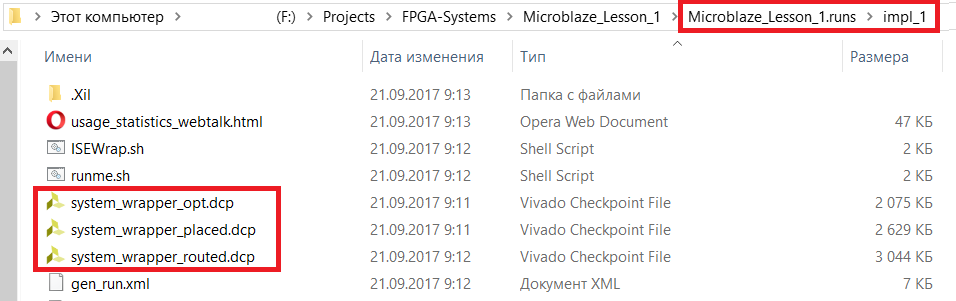

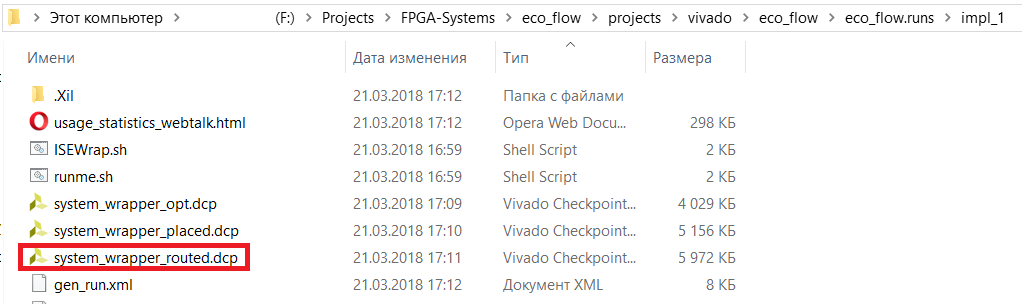

デフォルトでは、Vivadoは4つのdcpファイルを作成します。1つ-プロジェクトの最上位モジュールの合成段階で(コンテキスト外モードで合成を実行する場合、コンテキスト外で合成されるすべてのモジュールに対して、独自のdcpファイルが作成されます) 3-実装段階で。 これらのファイルは、フォルダーにあります。

「プロジェクト名.runs /合成名/ top_module_name.dcp」

「Project_name.runs / implementation_name /」。

図 図1は、一部の抽象プロジェクト用にデフォルトで作成される場所と.dcpファイルの例を示しています。

図1-デフォルトで作成されたdcpファイル(1-「postsynthesis-」および3-「post-implementation-」:最適化後(_opt)、配置後(_placed)、トレース後(_routed))

Vivadoのプロジェクト作業モード(プロジェクトモード[8])では、.dcpファイルが自動的に作成されます。 ただし、非プロジェクトモード(Non-ProjectMode [8])で作業する場合、ユーザー自身がプロジェクトの現在の状態の「スナップショット」が記録されていることを確認する必要があります。 これを行うには、適切なTclコマンド[9、10]を使用します。

write_checkpoint <file_name>.dcp read_checkpoint <file_name>.dcp

なぜ、どのように、どのdcpファイルを開くべきかについては、後で説明します。

3.テストプロジェクトの開発

テストプロジェクトでECO機能を実証するには、次のものが含まれている必要があります。

- 元のネットリストにない要素、または機能を変更できる要素。 たとえば、ボタンのLEDをオンにします。元のプロジェクトでは押すと点灯し、変更したプロジェクトでは押すと消灯します。 つまり、元のプロジェクトにはないインバータをネットリストに追加する必要があります。

- コンテンツを変更できる要素。 たとえば、LUTの真理値表やブロックメモリの内容。 さらに、ここでブロックメモリの内容を変更することをお勧めします。追加のインバータを作成するときに、手順1でLUTの変更を既に実行しているためです。

- ILA-接続された回路を他の回路に置き換える可能性。 つまり、ILA自体に触れることなく、ネットリストを介して、それに接続されている元のプロジェクトで選択された回路を他の回路に置き換えます。

- 混乱した結論。 プリント基板の設計時に、開発者がFPGA開発者と調整せずに、配線の利便性のために2つのピンのピンスワップを実行したとします。 rxとtx UARTを混同するエラーを起こしました。 ECOモードでは、接続を復元する必要があります。

3.1。 プロジェクト作成

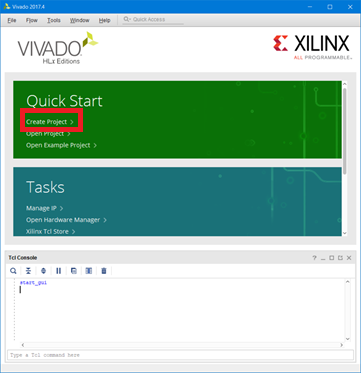

Vivadoアイコンを見つけて2回クリックすると、ようこそウィンドウが開きます(図2)

図2-Vivadoのようこそウィンドウ

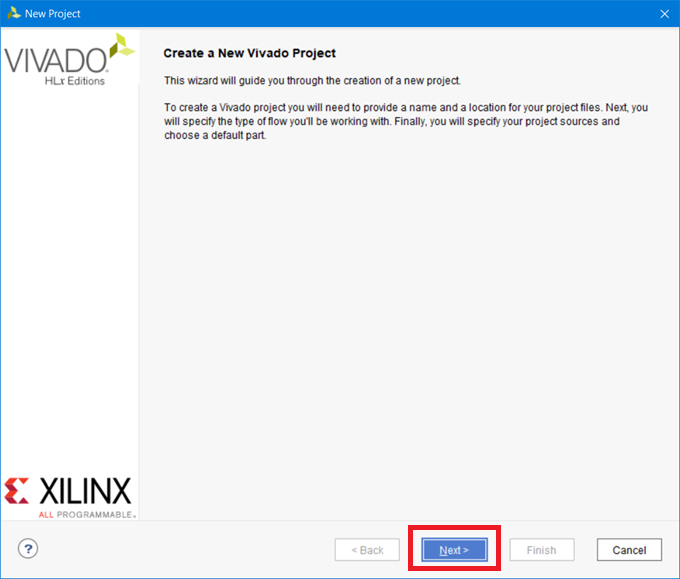

図2-Vivadoのようこそウィンドウ新しいプロジェクトを作成するには、[プロジェクトの作成]ボタンをクリックします。 ボタンを押すと、新しいプロジェクトを作成するためのウィザードが表示されます。 表示されたら、[次へ]ボタンをクリックします(図3)。

図3-新しいプロジェクトウィザードを作成するためのウィンドウ

図3-新しいプロジェクトウィザードを作成するためのウィンドウ

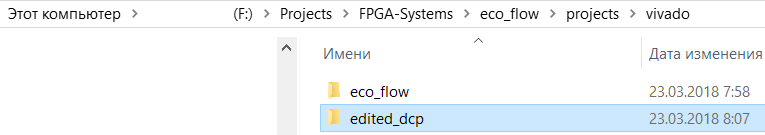

プロジェクトの名前を入力し、「プロジェクト名」フィールドに「eco_flow」と入力します。 プロジェクトの場所を指定します。[プロジェクトの場所]フィールドで、プロジェクトのディレクトリを指定します。 「F:/ Projects / FPGA-Systems / eco_flow / projects / vivado」にします。 [プロジェクトサブディレクトリの作成]チェックボックスをオンにすると、プロジェクト名を持つ追加のフォルダーが作成されます。 [次へ]をクリックします(図4)。

図4-プロジェクトの名前と場所の入力

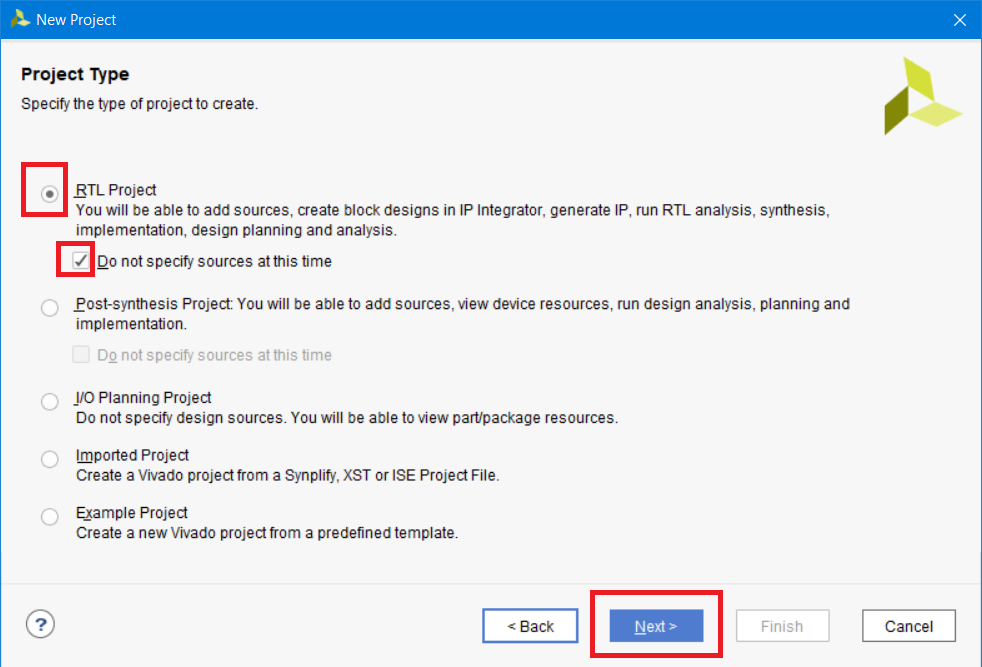

通常のプロジェクトを作成するため、RTLプロジェクトタイプを選択するだけです。 現在の段階では、プロジェクトにファイルを追加しません。そのため、「この時点ではソースを指定しない」をチェックして、「次へ」をクリックします(図5)。

図5-作成するプロジェクトのタイプの選択

Artyボード[2]で作業するため、その上にインストールされている水晶xc7a35tcsg324-1を選択します。 [次へ]をクリックします(図6)。

注:使用可能なボードのテンプレートから既製のボードを特に選択しません。 これは、ユーザーが手動でミスをすることができるようにするために行われます。

図6-水晶xc7a35tcsg324-1の選択

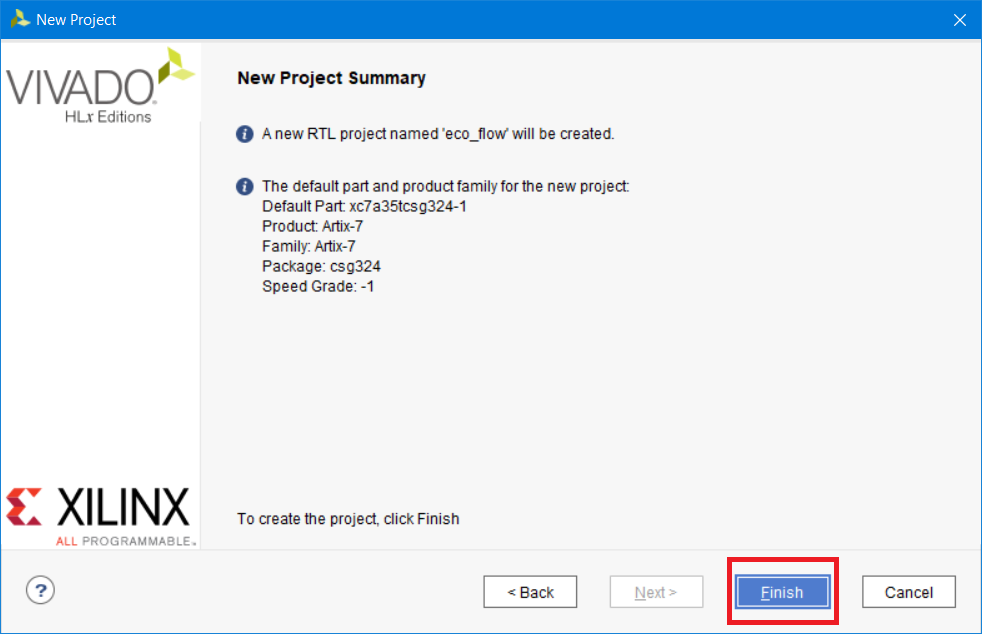

新しいプロジェクトセットアップウィザードの最後は、作成されたプロジェクトの[概要]ウィンドウです。 [完了]をクリックします(図7)。

図7-作成されたプロジェクトの簡単な情報のウィンドウ

3.2。 HDLファイルを作成してプロジェクトに追加する

ここでは、2つのモジュールを作成します。点滅するLEDと、常に読み取られるブロックメモリのみです(実際、これは、後で変更しようとするフィルタ係数メモリの模倣です)。

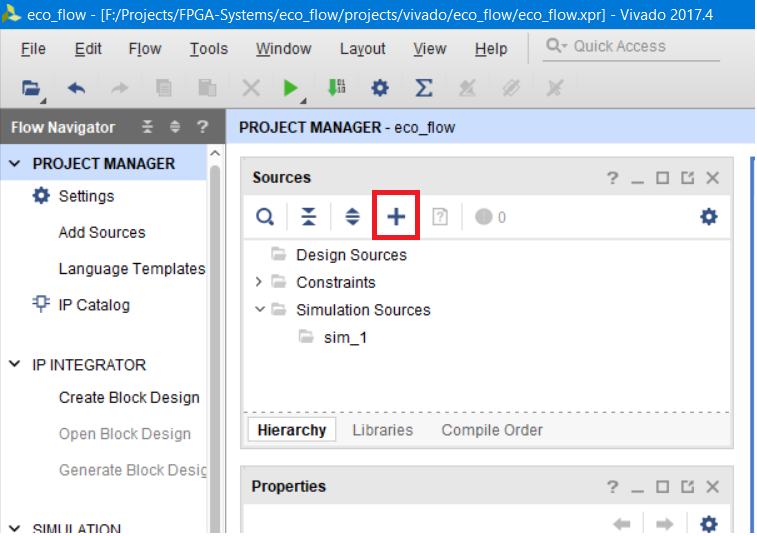

新しいファイルを作成してプロジェクトに追加するには、ウィザードを使用します。ウィザードは、青いプラス記号をクリックして呼び出されます(図8)。

図8-プロジェクトへのファイルの追加を作成するためのウィザードの呼び出し

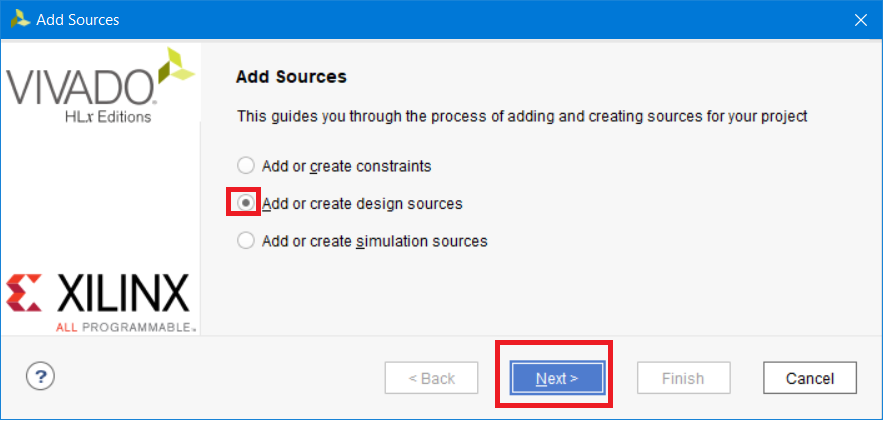

図8-プロジェクトへのファイルの追加を作成するためのウィザードの呼び出し表示されるウィンドウで、[デザインソースの追加または作成]を選択し、[次へ]をクリックします(図9)。

図9-作成または追加するファイルの種類の選択

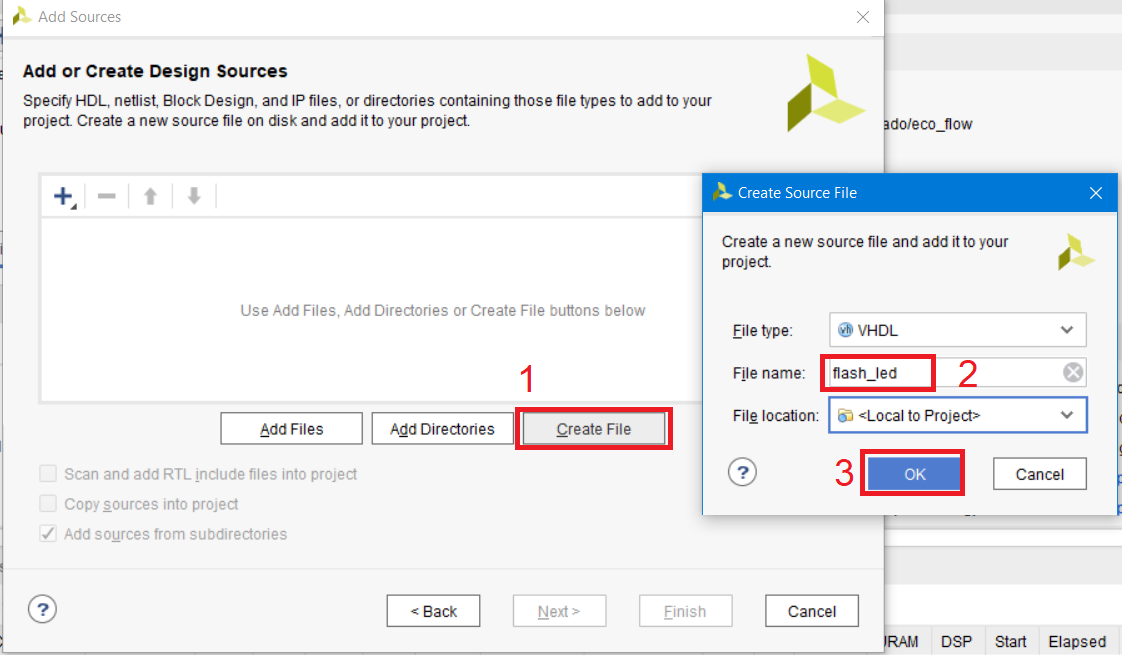

図9-作成または追加するファイルの種類の選択[ファイルの作成]を選択し、表示されるウィンドウの[ファイル名]フィールドに、作成するflash_ledファイルの名前を入力して、[OK]をクリックします(図10)。

図10-新しいファイルの作成とその名前の入力

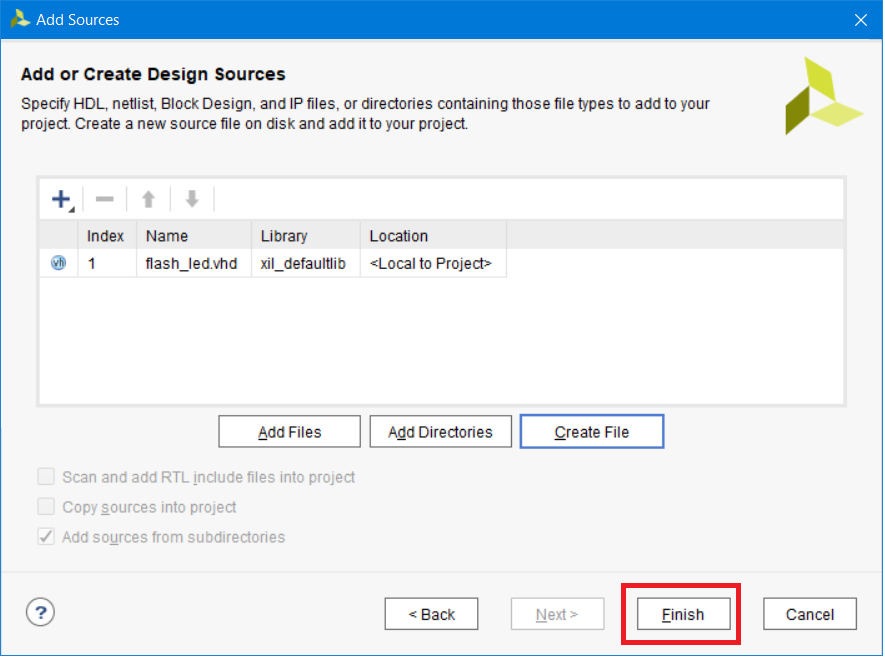

その後、追加されたファイルのリストにファイルが表示されます。 [完了]をクリックします(図11)

図11-追加または作成されたファイルのリスト

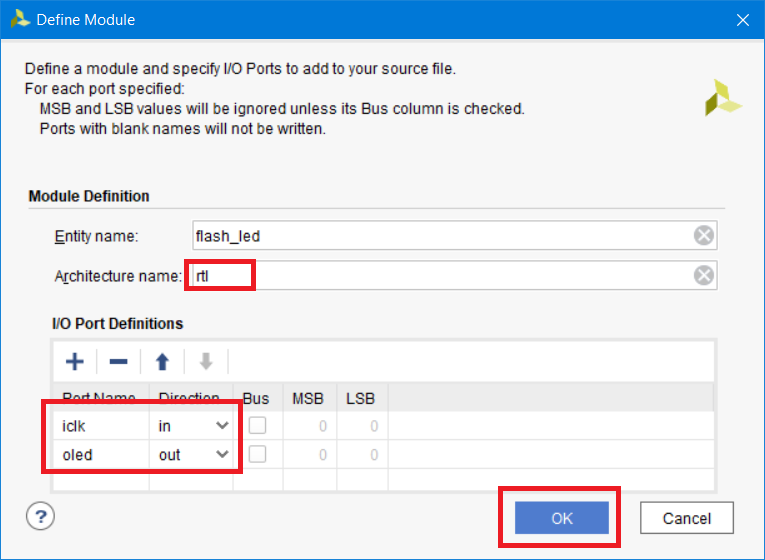

これで、ファイルのテンプレートを作成するためのウィザードが表示されました。 VHDLを使用しているため、アーキテクチャ名をrtlに変更できます。 モジュールの2つのピンを作成します。「in」方向のiclk(モジュールのクロック信号)と「out」方向のollk(LEDに接続された出力)。 [OK]をクリックします(図12)。

図12-モジュールテンプレートを作成するためのウィザード(VHDLの場合)

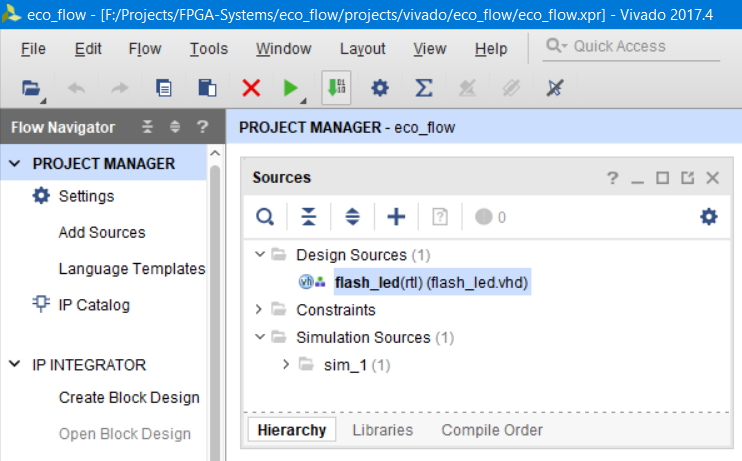

図12-モジュールテンプレートを作成するためのウィザード(VHDLの場合)これで、モジュールがプロジェクトツリーに追加されました(図13)。

図13-作成されたflash_ledモジュール

モジュールは単純な機能を実行する必要があります。1秒の周期でLEDを点滅させるだけです。 今後の展望として、プロジェクトのクロック周波数は100 MHzであり、モジュール自体は宿題をする際に引き続き役立つと言えます。

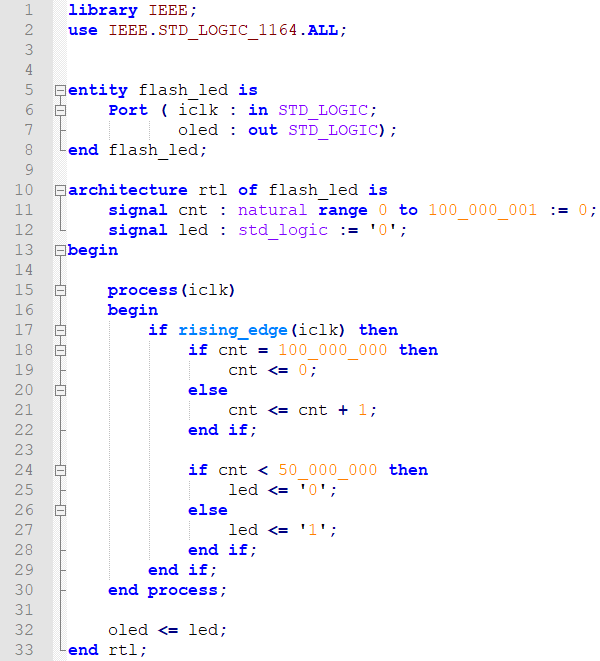

ファイルの内容を次のものに置き換えます(リスト1(リスト1のテキストバージョンについては、付録Aを参照)。 コードは非常に単純であり、その作業を説明するために追加のコメントを必要としません。

リスト1-Flash_ledモジュールコード

brom_readerと呼ばれる新しいモジュールを作成します。iclkポートは「in」方向、odout [7:0]は「out」方向です(図8から図12の手順を繰り返します)。

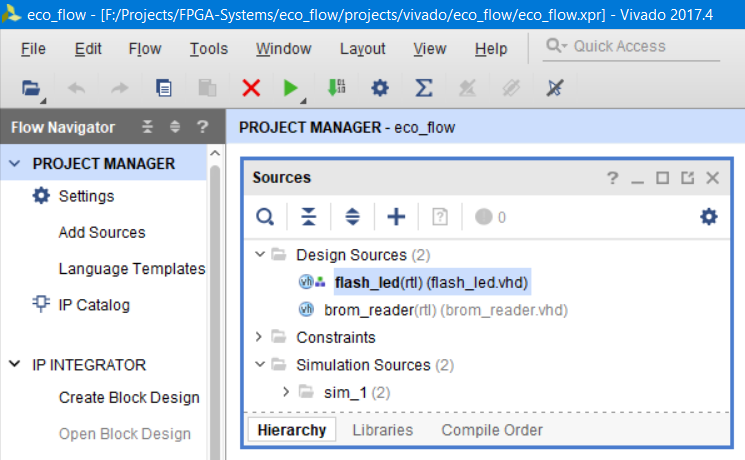

すべてが正しく行われると、プロジェクトツリーにbrom_readerモジュールが表示されます(図14)。

図14-プロジェクトツリーのbrom_readerモジュール

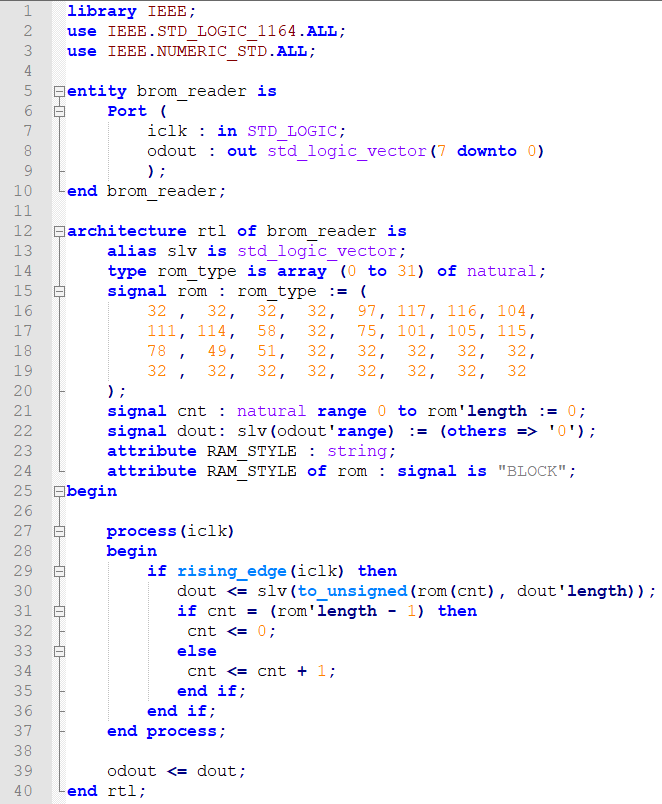

図14-プロジェクトツリーのbrom_readerモジュールモジュールの内容を次のテキストに置き換えます(リスト2(リスト2のテキストバージョンについては、付録Bを参照)。 ここでいくつかのコメントが必要になります:

- 13行目:std_logic_vectorタイプのエイリアスが作成されます。 VHDLで作業する人は、多くの場合「std_logic_vector()」データ型を使用します。 これらの長い名前を毎回書かないようにするために、エイリアスを宣言して、モジュールコード全体で使用できます。

- 行14〜20:自然数の2次元配列の標準宣言と配列の初期化(数値を含むメモリが作成されます)。

- 行22:エイリアスslvを使用してシグナルを宣言する

- 23〜24行目:合成属性の使用[11]。 なぜここに登録されているのですか? かなり小さな2次元配列(行15〜20)を作成しました-おそらく、合成中に最適化され、LUTの分散メモリとして実装されます。 また、配列をブロックメモリ(BRAM-Block RAM)に配置するため、シンセサイザーにこれを明示的に伝える必要があります。これは、合成属性を使用して行われます。 [11]のVivado合成ガイドで詳細を確認してください。

そうでなければ、すべてが明確になります。その内容が連続的、連続的、周期的に読み取られるROMメモリを作成しました。

リスト2-brom_readerモジュールコード

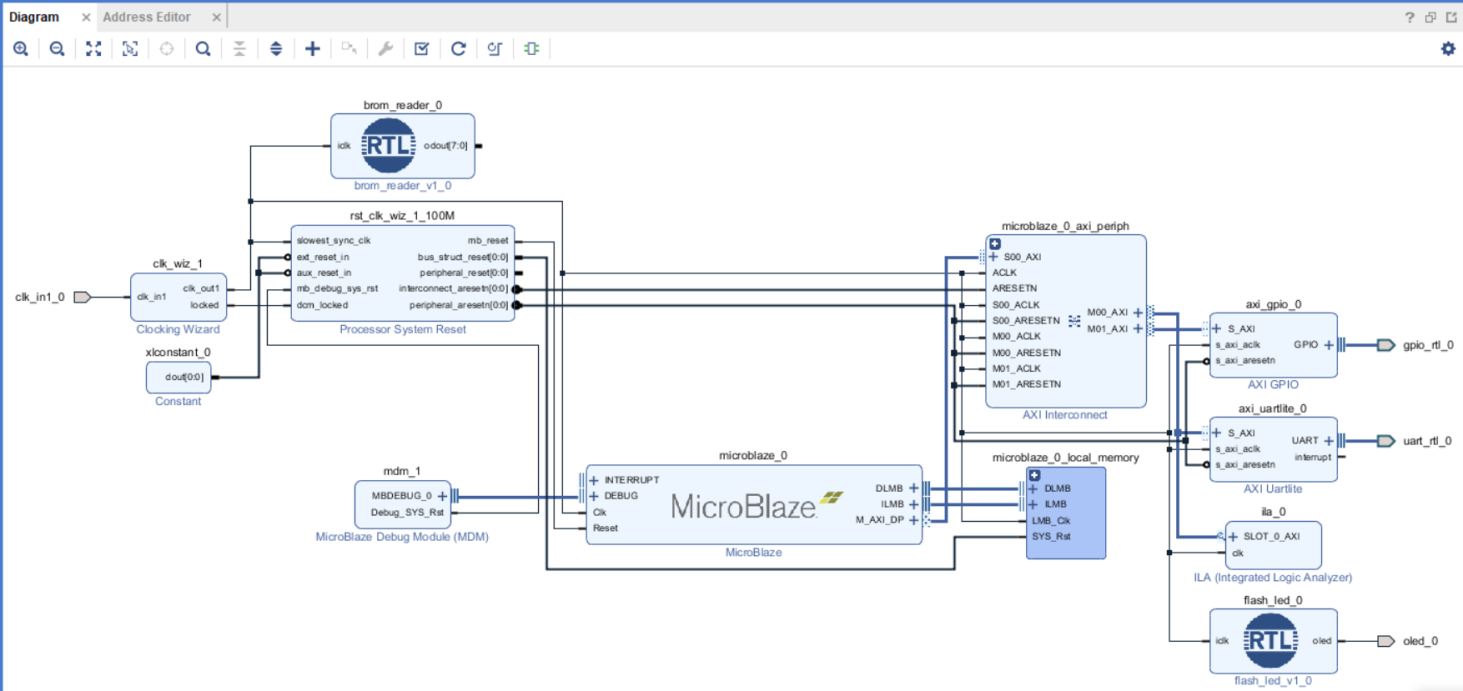

3.3。 MicroBlazeプロジェクトの作成とIPインテグレーターでの作業

次に、MicroBlazeを使用してプロジェクトを作成します。 ここでも、初心者向けのMicroBlazeソフトウェアプロセッサでのプロジェクトの作成に関するステップバイステップガイドがロシア語で提供されていることに注意してください[16]。

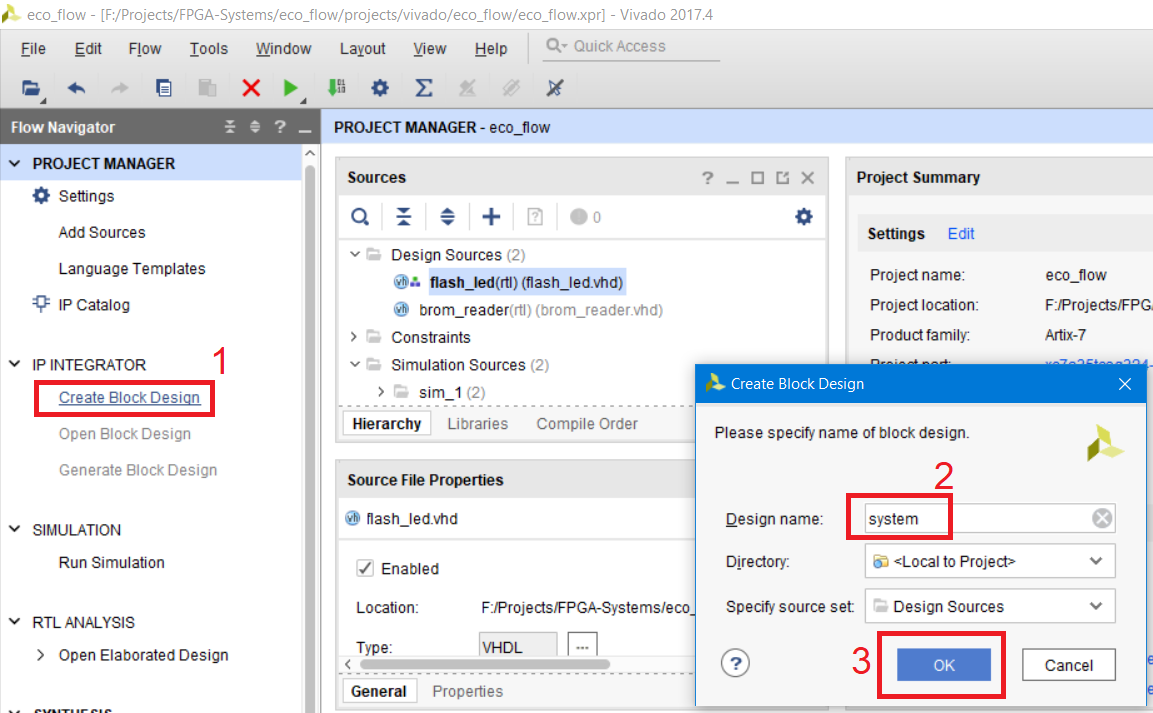

ブロックプロジェクトを作成するには、ブロックデザインを作成する必要があります。 [ブロックデザインの作成]を選択し、ネームシステムを入力して[OK]をクリックします(図15)。

図15-新しいブロックデザインの作成とその名前の割り当て

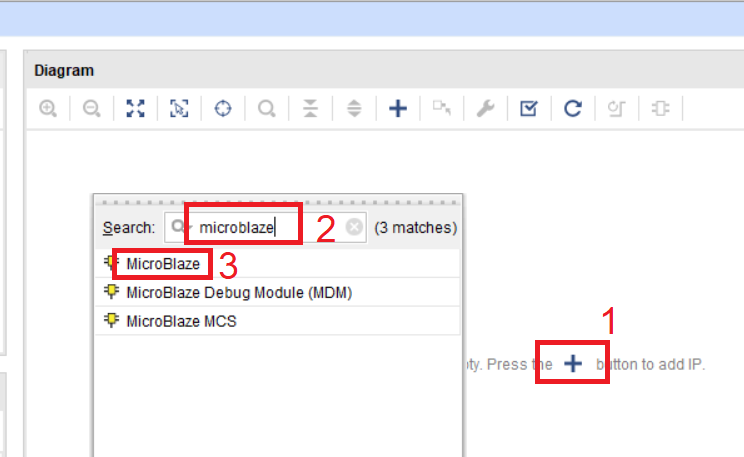

図15-新しいブロックデザインの作成とその名前の割り当てVivado IPディレクトリのカーネル、またはVHDL / Verilog / SystemVerilogで記述されたRTLモジュールが[ダイアグラム]フィールドに追加されます。 MicroBlazeモジュールはIPディレクトリにありますが、これを行うには、青いXをクリックし、検索フィールドに「MicroBlaze」と入力して選択します(図16)。

図16-図ワークスペースへのMicroBlaze IPコアの追加

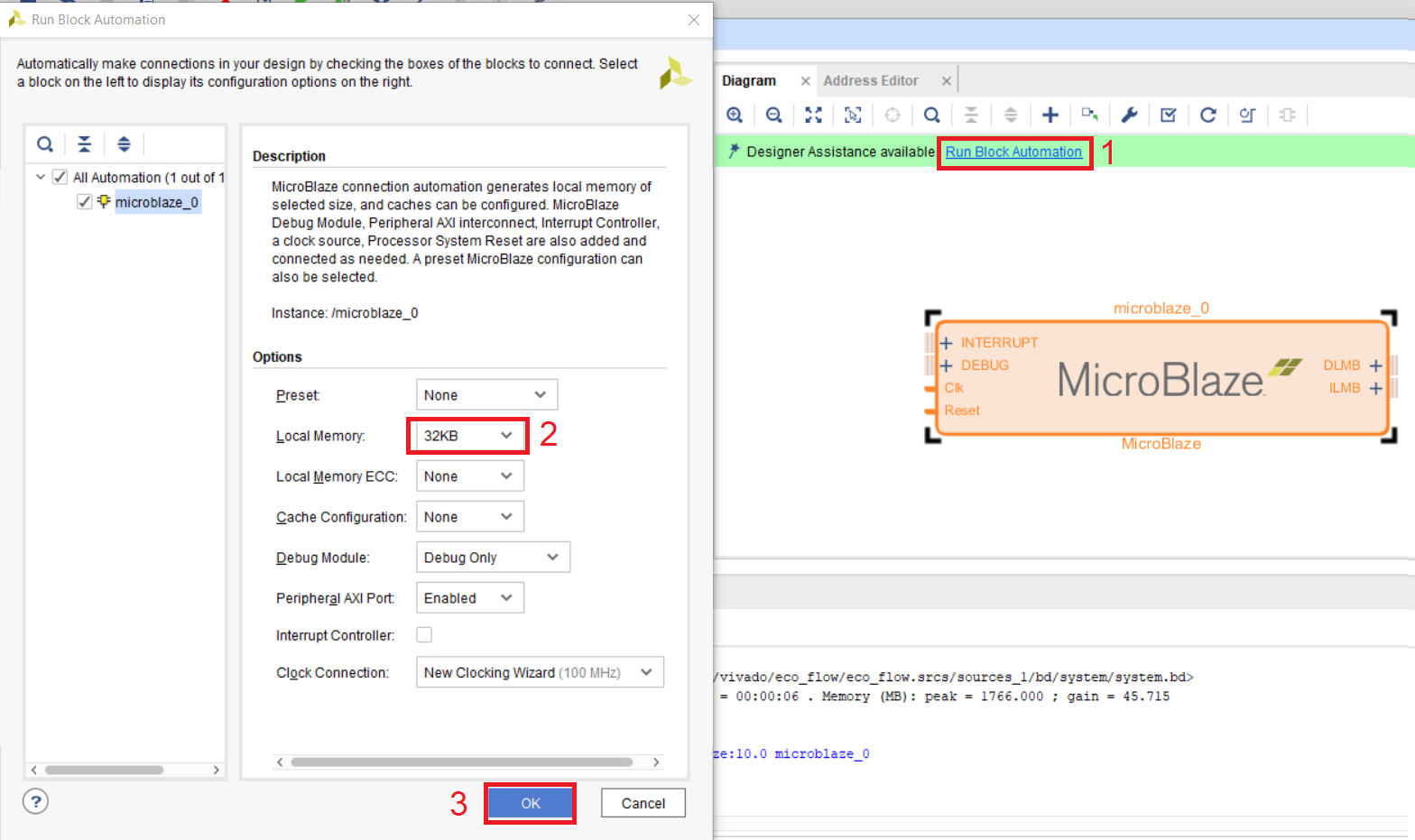

MicroBlazeを作業フィールドに追加した後、ソフトプロセッサのエクスプレス設定を使用します。 [ブロックオートメーションの実行]を選択し、図に従って設定を設定します。 17. [OK]をクリックします。

図17-Express設定MicroBlaze

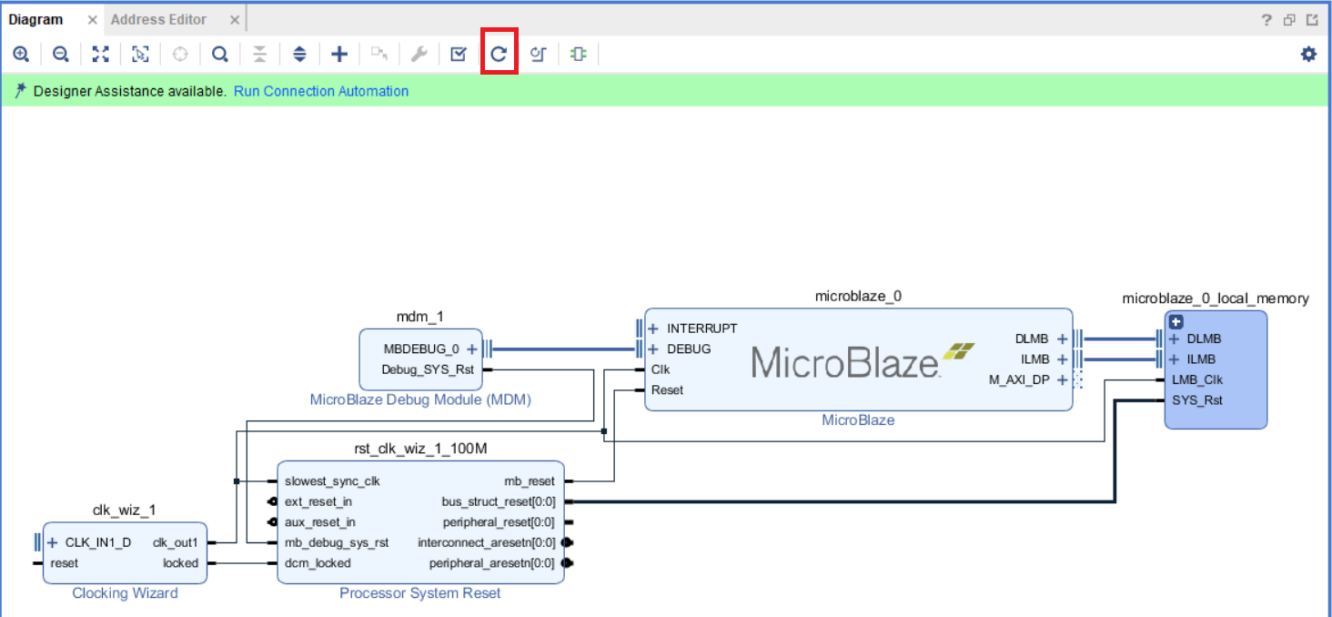

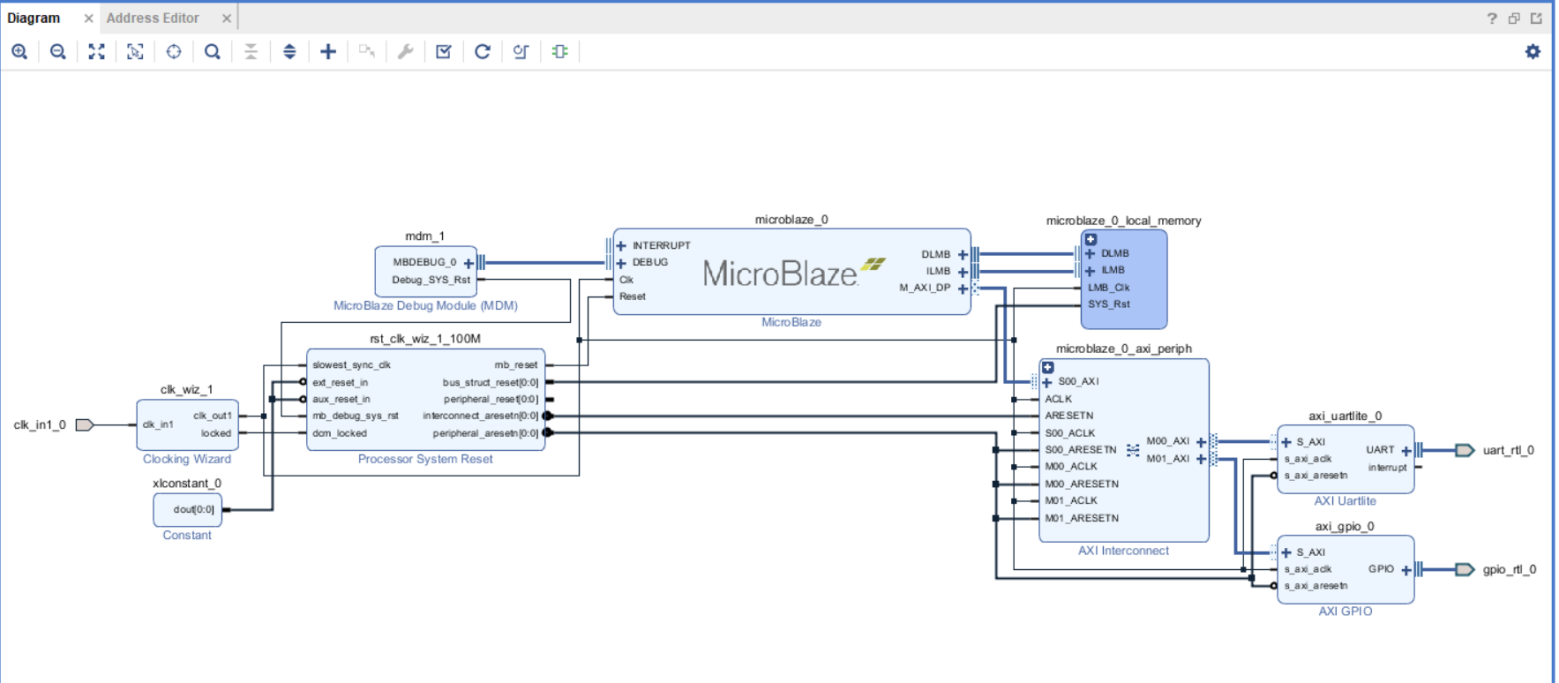

その後、クロックジェネレーターとローカルプロセッサメモリ[11、12]を含む、いくつかの新しいIPコアがダイアグラム作業フィールドに表示されます。 [再生成]ボタンを押して、作業フィールドを最適化します(図18)。

図18-MicroBlazeの基本的な組み込み

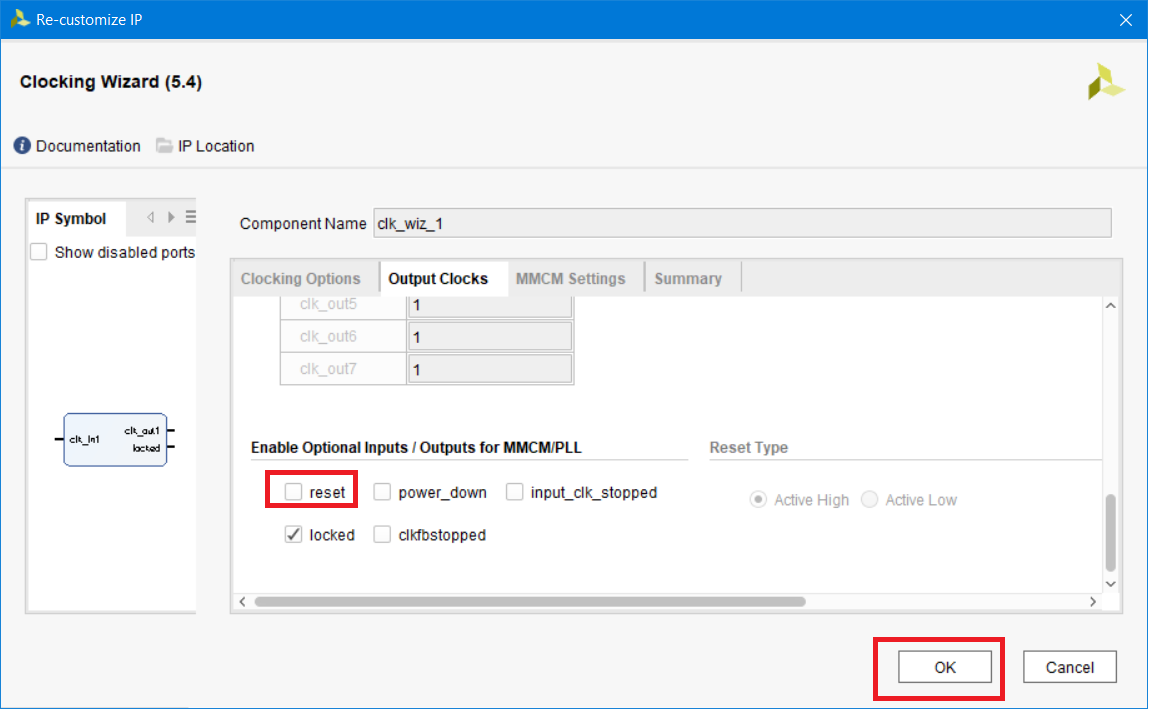

図18-MicroBlazeの基本的な組み込みArtyボードに従っていくつかのモジュールを構成しましょう。 clk_wiz_1クロックグリッド生成モジュールをセットアップします。 モジュールの設定を呼び出すには、マウスの左ボタンでダブルクリックします。 設定ウィンドウで、100 MHzのジェネレーターがボードにインストールされているため、入力クロック周波数の値を100 MHzに設定します[12]。 また、ソースタイプをユニポーラとして設定します(図19)。 [出力クロック]タブに移動して、モジュールの出力周波数を設定します。

図19-入力周波数パラメーターの設定

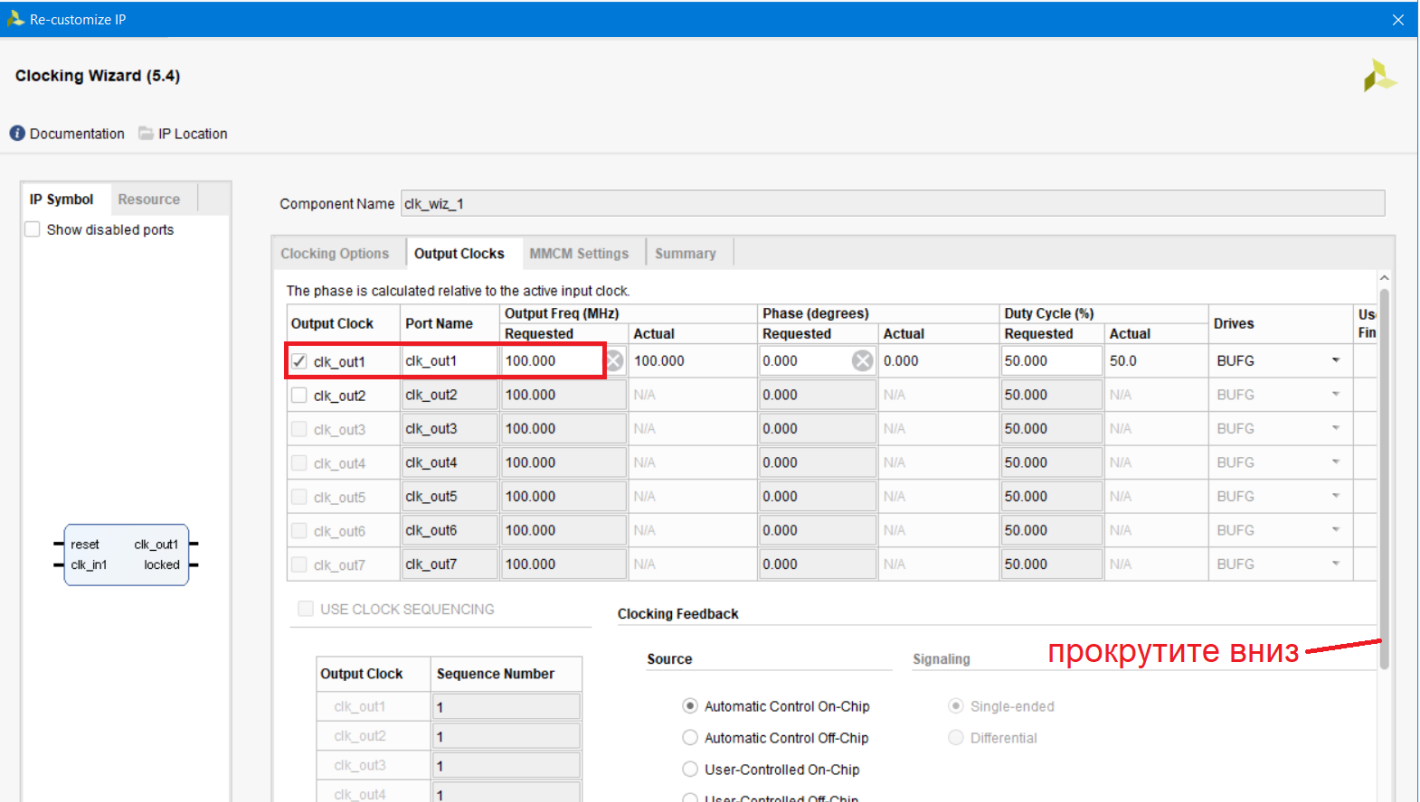

[出力クロック]タブでは、プロセッサシステムと他のモジュールのメイン周波数である1つの周波数のみを指定します。 100 MHzに設定します(図20)。

図20-出力周波数パラメーターの設定

下にスクロールして、追加のサービストーンを設定します。 使用しないリセット信号を削除します。 チェックを外します(図21)。 残りの設定は必要ありません。[OK]をクリックします。

図21-サービス信号の設定

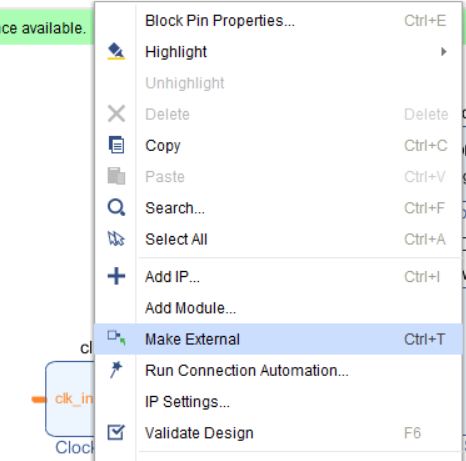

図21-サービス信号の設定次に、外部モジュールclk_wiz_1の入力clk_in1を宣言します。実際には、そこからブロックデザインの入力を作成します。 これを行うには、マウスの右ボタンでclk_in1をクリックし、[外部作成]を選択します(図22)。

図22-clk_in1ポートを外部にする

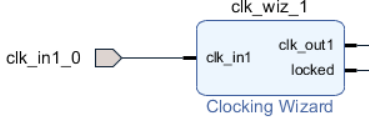

ご覧のとおり、clk_in1_0ポートが表示されました(図23)。

図23-入力ポートclk_in1_0

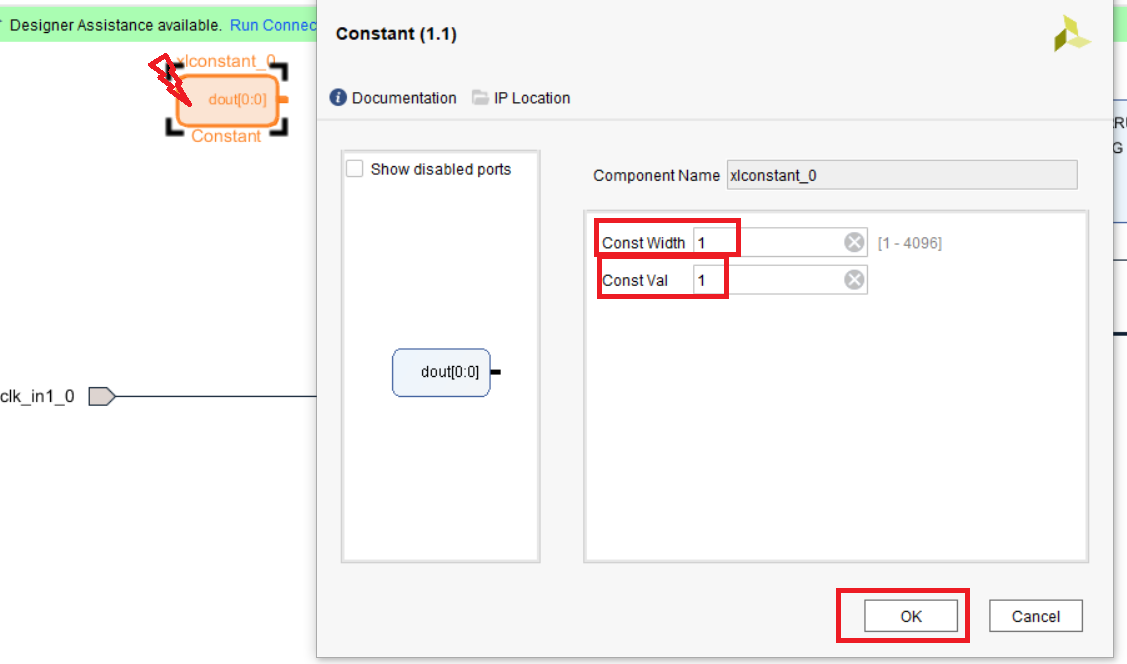

プロセッサシステムのリセット制御モジュールでは、2つの未使用の入力(外部リセットと追加リセット)を非アクティブロジックレベル「1」に接続します。 これは、constantと呼ばれるIPブロックを使用して行います。 これを行うには、上部の青い十字をクリックし、検索バーに「const」と入力して、定数モジュールを選択します。

図24-使用可能なIPのリストでIPブロック定数を検索

図24-使用可能なIPのリストでIPブロック定数を検索左マウスボタンでダブルクリックして、モジュールxlconstant_0を構成しましょう。 行値(Const val)に1を入力し、行幅(Const Width)に1を入力して[OK]をクリックします(図25)

図25-xlconstant_0モジュールの構成

図25-xlconstant_0モジュールの構成モジュールxlconstant_0の出力doutを、モジュールrst_clk_wiz_1_100Mの入力ext_reset_inおよびaux_reset_inに接続します。 これらのポートをマウスで接続するだけです(図26)。

図26-未使用のポートを定数に接続する

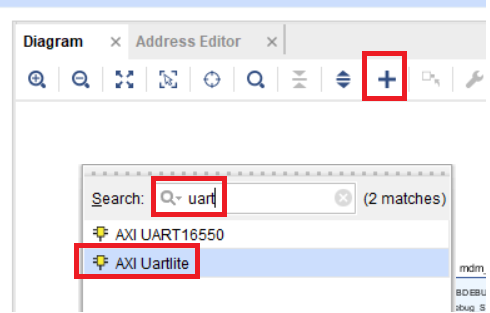

図26-未使用のポートを定数に接続するUARTモジュールを追加し、利用可能なIPコアのカタログで見つけます(図27)。

図27-利用可能なIPブロックのリストでUARTモジュールを検索

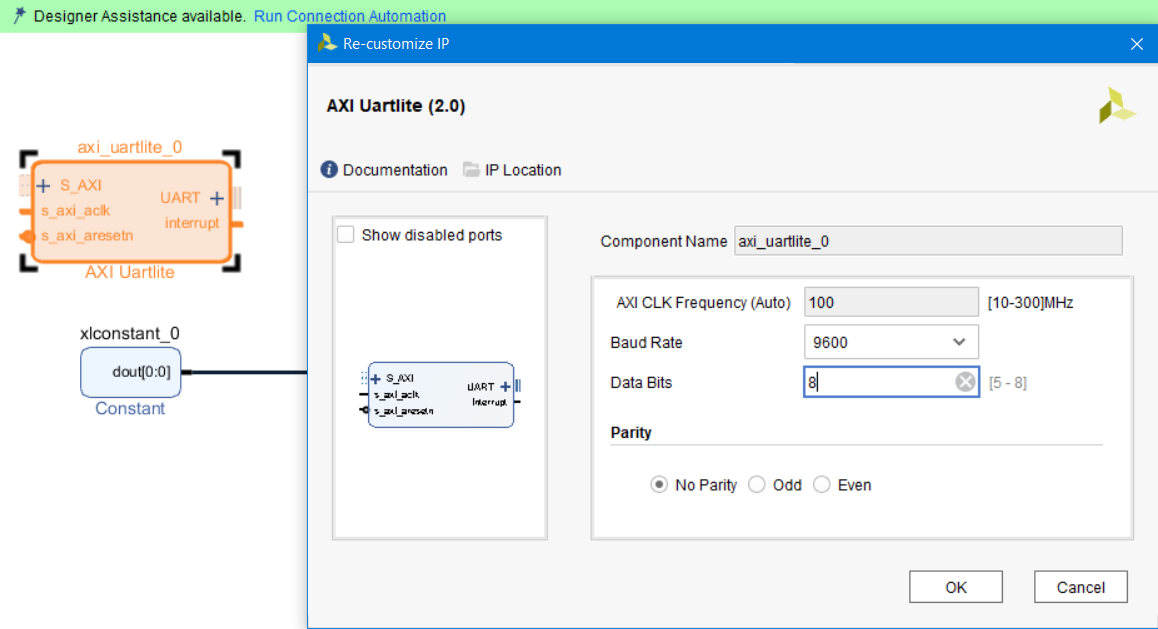

図27-利用可能なIPブロックのリストでUARTモジュールを検索図に従って送信設定を設定して、axi_uartlite_0モジュールを構成しましょう。 28. [OK]をクリックします。

図28-axi_uartlite_0モジュールの設定

図28-axi_uartlite_0モジュールの設定次に、axi_uartlite_0モジュールをプロセッサに接続します。 これには自動化された方法を使用します。 [接続オートメーションの実行]の上部をクリックし、接続先(AXI MicroBlazeへのAXI UART入力)を選択します。 29。

図29-axi_uartlite_0をプロセッサに接続

図29-axi_uartlite_0をプロセッサに接続UARTインターフェイスは標準であり、Vivado IPインテグレーターでは別のタイプのインターフェイスに分離されています。 図のパラグラフ2 29 axi_uartlite_0モジュールのrxとtxを外部にしたいと言いました。 インターフェイスを開くと、表示されます。 インターフェイスに青色のワイヤが1つしかないことを恥ずかしがらないでください。後でプロジェクトのHDLラッパーを作成すると、2つのポート(rxとtx)があることがわかります。

[レイアウトを再生成]ボタンをクリックします。 その後、ブロックデザインワークスペースが最適化され、図に示すように、回路はidを受け入れます。 30.正しく接続されていることを確認します。 この段階ですべてが正常な場合は続行し、エラーがある場合はプロセッサシステムを再構築します。

図30-プロセッサシステムの組み立ての中間段階。

図30-プロセッサシステムの組み立ての中間段階。AXIバスに別のモジュールを追加しましょう。 これがGPIOモジュールになり、その出力をLEDに接続します。 利用可能なIPブロックのリストでAXI GPIOモジュールを見つけて、作業フィールドに追加します(図31)。

図31-利用可能なIPのリストにあるAXI GPIOモジュール

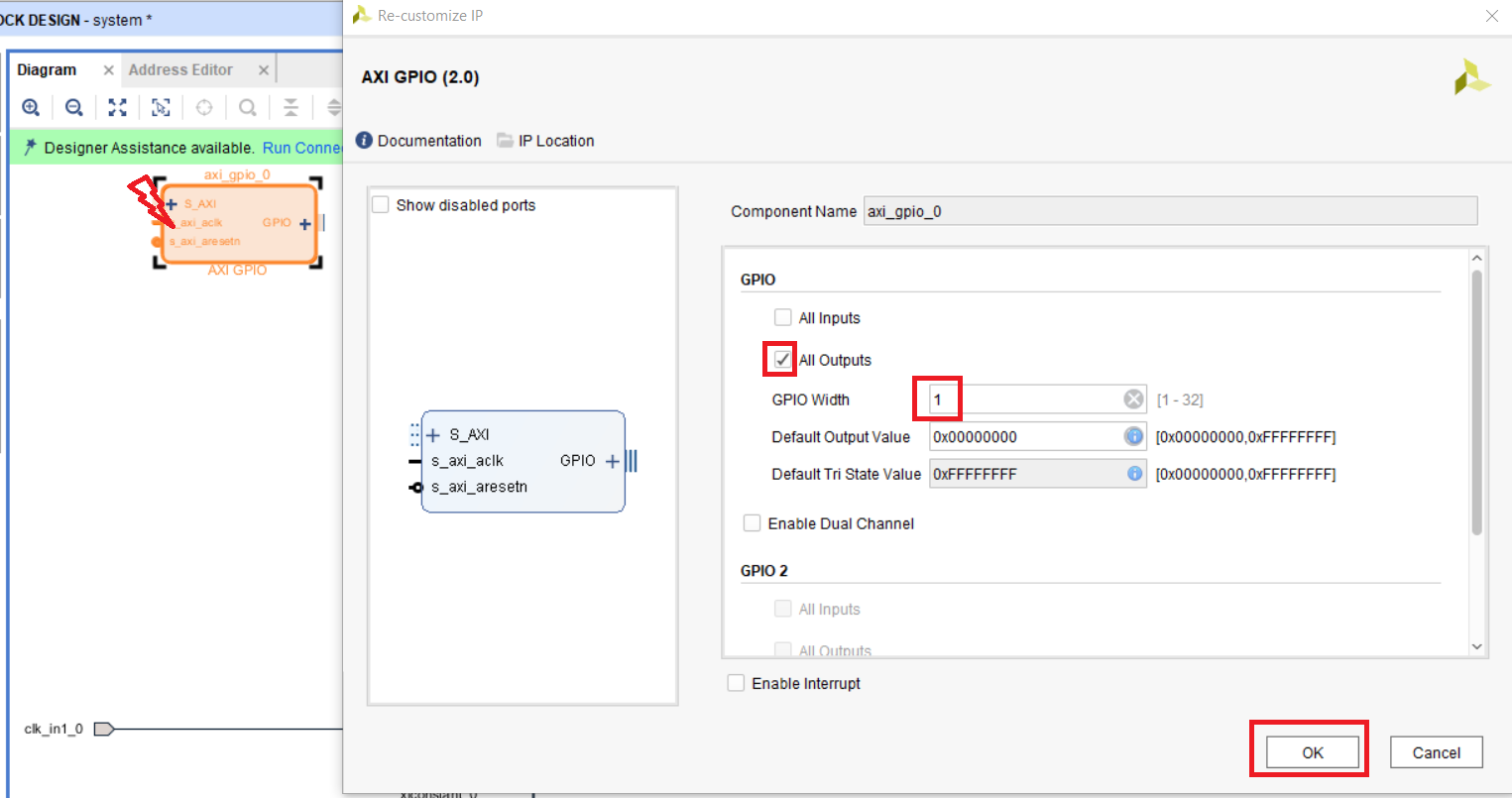

図31-利用可能なIPのリストにあるAXI GPIOモジュール図に従ってモジュールを構成します。 32(1つのチャネルと1つの出力のみを使用します)。

図32-モジュール設定axi_gpio_0

図32-モジュール設定axi_gpio_0axi_gpio_0モジュールをプロセッサに接続し、出力を外部にします。 [接続自動化の実行]をクリックし、すべてのボックスをオンにします(図33)。

図33-axi_gpio_0をプロセッサに接続

図33-axi_gpio_0をプロセッサに接続[レイアウトの再生成]ボタンをクリックし、すべての接続が表示されていることを確認します。 34。

図34-プロセッサシステムのアセンブリ。

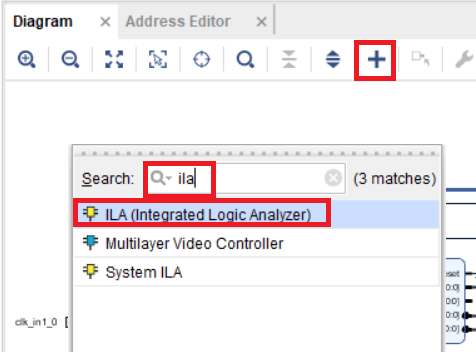

図34-プロセッサシステムのアセンブリ。次に、デバッグモジュールILAを追加します。 UARTモジュールのAXI Liteバスでトランザクションを表示するとします。 利用可能なIPモジュールのリストにILA(Integrated Logic Analyzer)があります。 35。

図35-利用可能なリストのILA IPブロック

図35-利用可能なリストのILA IPブロックここでは、デバッグモジュールをHDLコードに直接追加する際に、いわゆるHDL挿入フローとの類似性を使用します。 合成後にネットリストでデバッグ用の回路を検索することもできます。 このアプローチは、ネットリスト挿入フローと呼ばれます。

AXIトランザクションをデバッグするため、ILAプローブタイプをAXI(ILAブロックのモニタータイプパラメーター)として設定する必要があります。 このモードはデフォルトで設定されているため、ila_0ブロックの入力SLOT_0_AXIを、表示したいトランザクションであるAXIバスに接続するだけです。 この場合、これはインターコネクトからaxi_uart_0モジュールに向かうバスです(図36)。 また、モジュールのクロック信号をシステムのclkに接続し、[レイアウトを再生成]ボタンをクリックします。

図36-ila_0をAXIバスaxi_uart_0に接続

図36-ila_0をAXIバスaxi_uart_0に接続デフォルトでは、記録されたデータの長さは1024に設定されています。これは、トランザクションを表示するのに十分です。

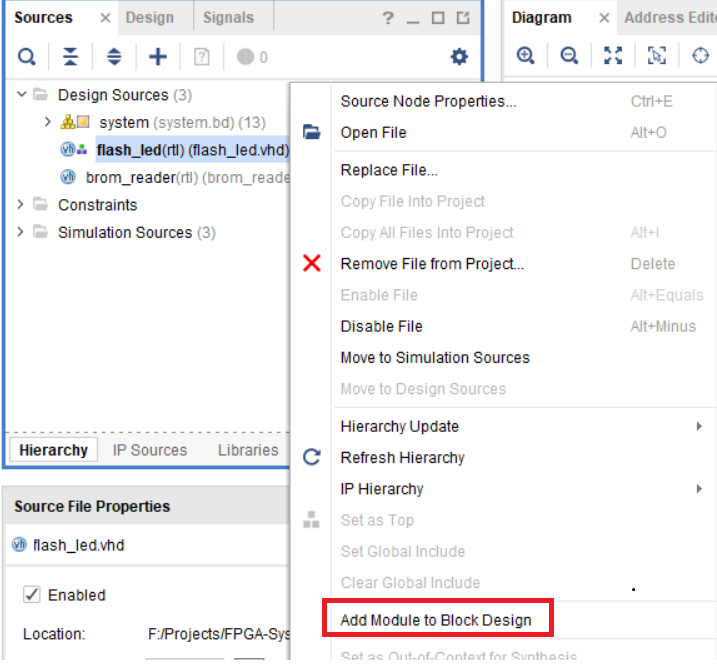

RTLモジュールをブロックデザインに追加し、flash_ledモジュールを選択して右クリックし、[モジュールをブロックデザインに追加]を選択します(これはバージョン2017.1以降のVivadoでのみ機能します)。

図37-図フィールドへのflash_ledモジュールの追加

図37-図フィールドへのflash_ledモジュールの追加flash_led_0モジュールのiclk入力をシステムのクロックに接続し、oledポートを外部にします(ポートを右クリックしてから、Make Exernalを選択します)。 [レイアウトを再生成]ボタンをクリックします。

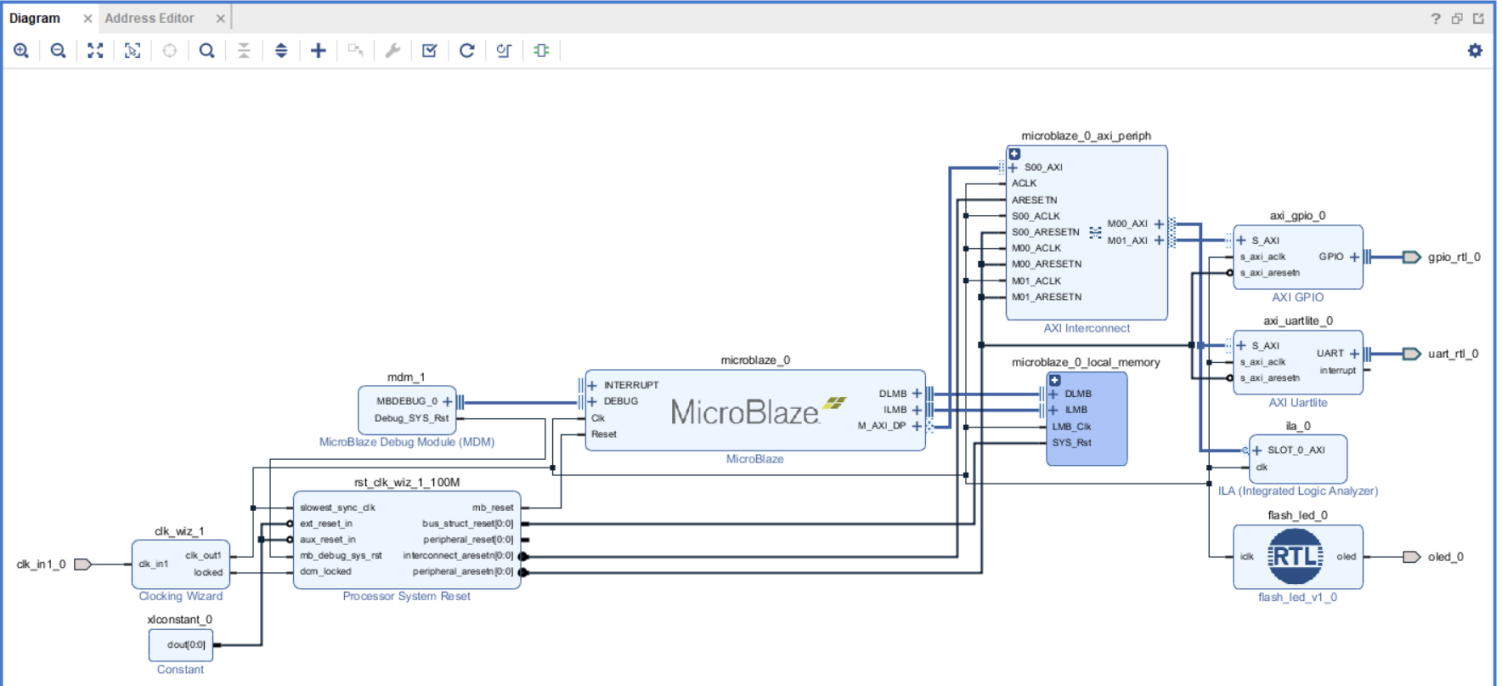

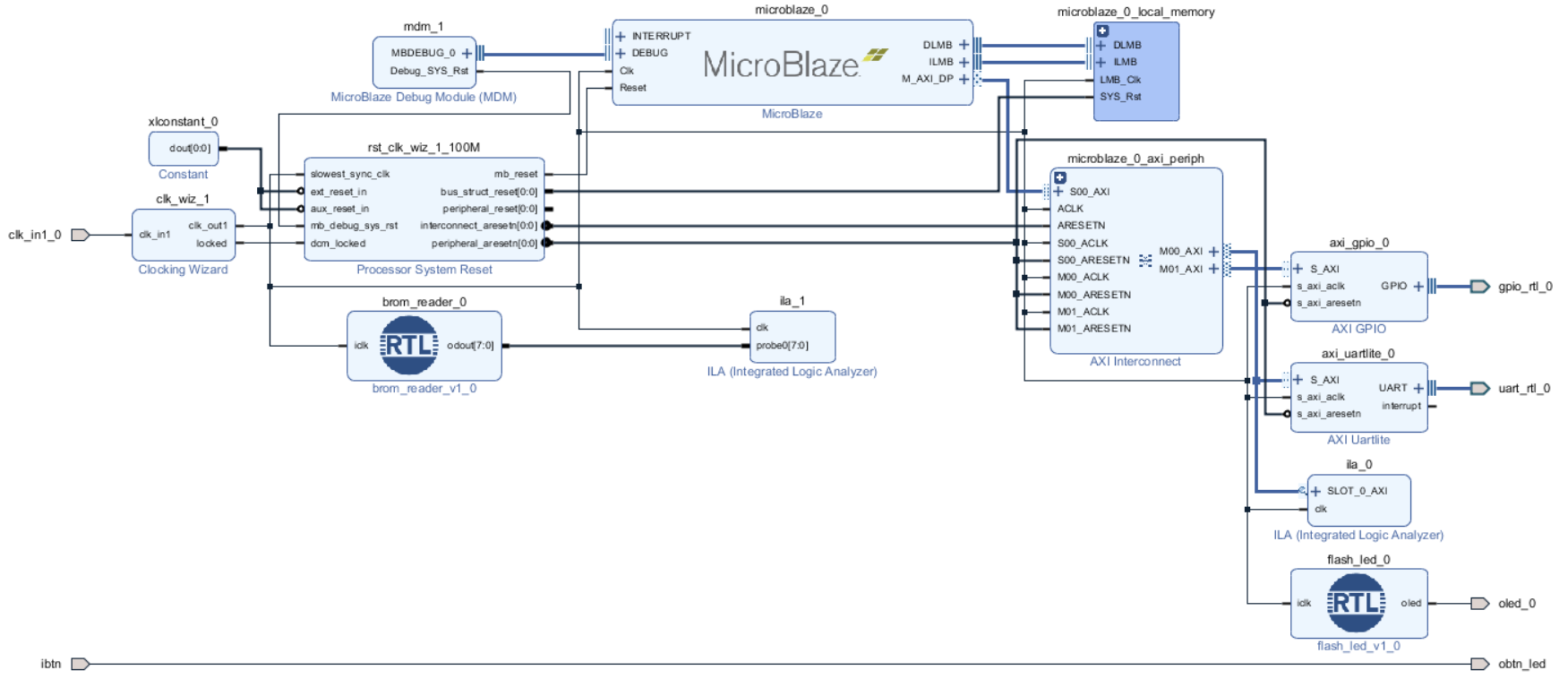

すべてが正しく行われると、図のようになります。 38。

図38-IPインテグレーターでプロジェクトを構築する中間段階

図38-IPインテグレーターでプロジェクトを構築する中間段階同じ手順を繰り返して、brom_readerモジュールを追加します。 iclkクロック入力をクロック回路に接続しますが、odout [7:0]出力を外部で宣言しません。 [レイアウトの再生成]をクリックします。 すべてが正しく行われると、図のようになります。 39。

図39-IPインテグレーターでプロジェクトを構築する中間段階

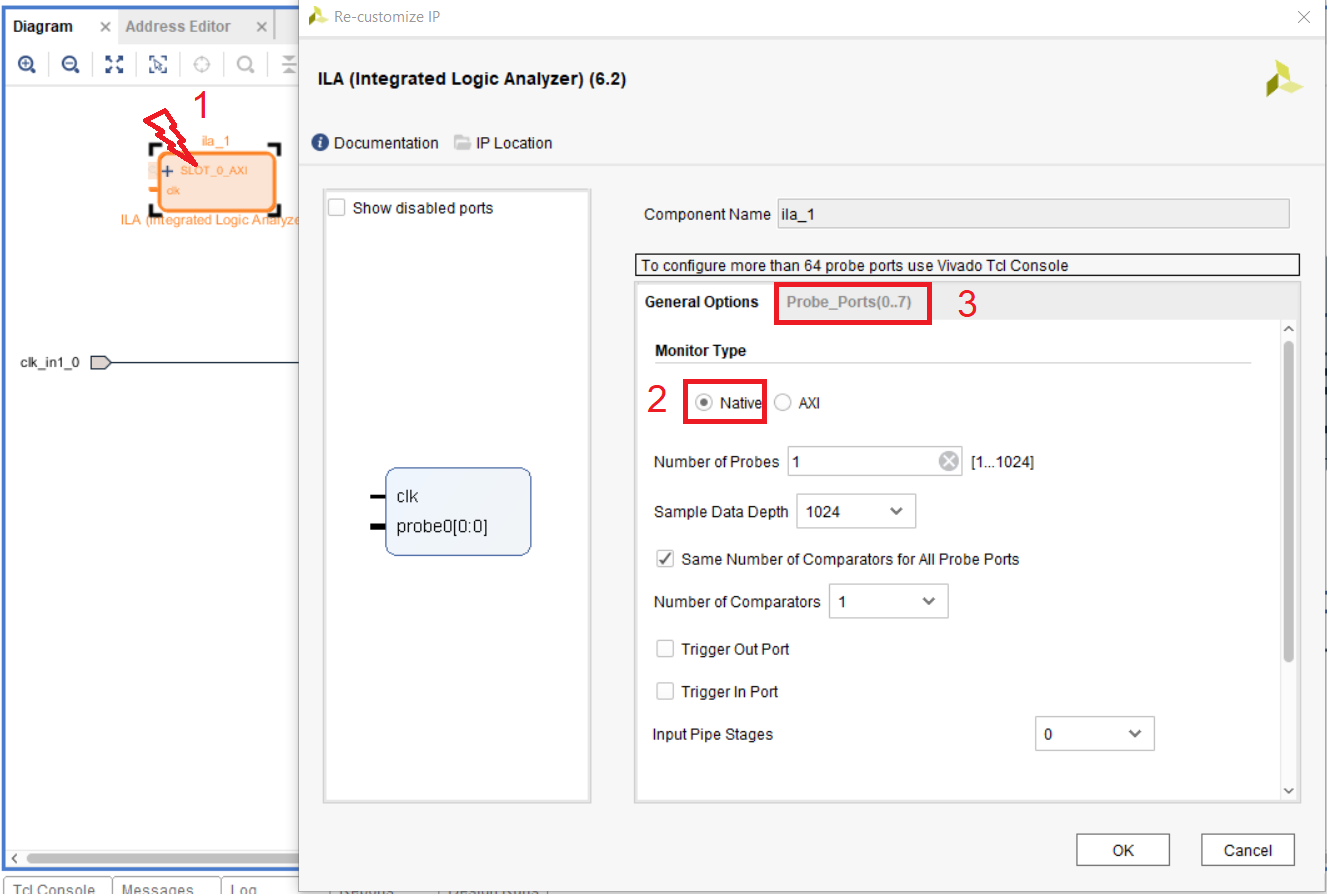

図39-IPインテグレーターでプロジェクトを構築する中間段階次に、別のILAを追加し、それをbrom_reader_0モジュールの出力odout [7:0]に接続します。

利用可能なブロックのリストでILA IPブロックを見つけ(図35)、それを[ダイアグラム]フィールドに追加します。 マウスでダブルクリックして設定してみましょう。 Monitor TypeをNativeに設定します(AXIバスをデバッグするのではなく、単純な回路をデバッグします)。 残りはデフォルトのままにします。 タブProbe_Ports(0..7)図に移動します。 40。

図40-ILAの構成

図40-ILAの構成プローブ幅を設定します。 幅の値を8に設定します(図41)。これは8ビット-brom_reader_0モジュールの出力バスodout [7:0]の幅です。 OKをクリックします。

図41-ILAプローブ幅の設定

図41-ILAプローブ幅の設定brom_reader_0モジュールの出力odout [7:0]をila_1モジュールのprobe_0 [7:0]入力に接続し、ila_1モジュールのclk入力をプロジェクトのクロック回路に接続します。 [レイアウトを再生成]ボタンをクリックします。すべてが正しければ、図のようになります。 42。

図42-IP Integaratorでプロジェクトを構築する中間段階

図42-IP Integaratorでプロジェクトを構築する中間段階ボタンを追加するだけで、LEDが直接点灯します。

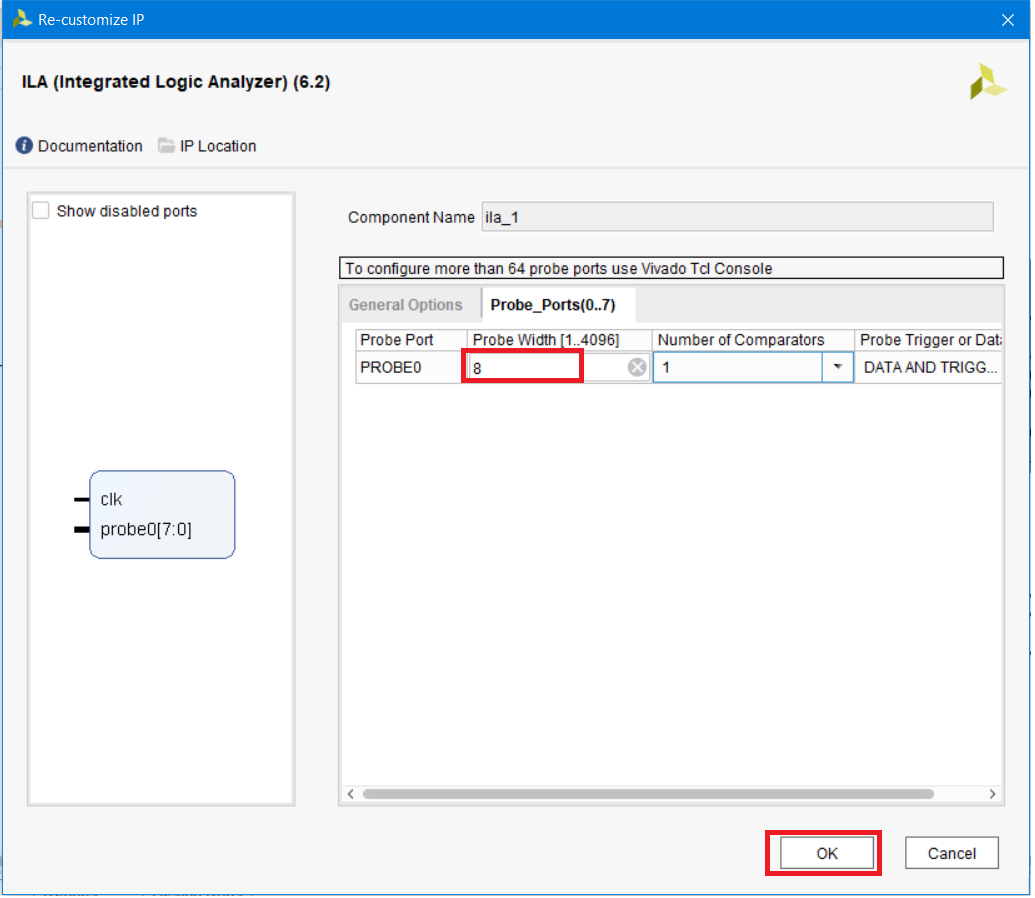

ブロック図の空の場所を右クリックし、[ポートの作成]を選択して、入力ポートを作成します(図43)。

図43-IPインテグレーターでのポートの作成

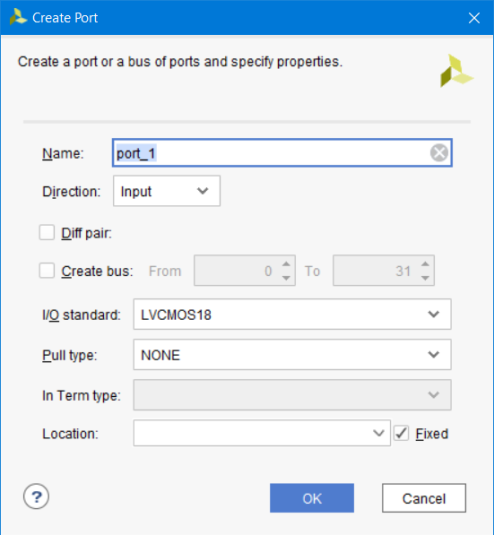

ポート設定ウィザードが表示されたら、名前にibtnを入力し、方向の入力と、必要に応じてビット深度を指定します。 [OK]をクリックします(図44)。

図44-新しいポート設定ウィザード(ibtnボタン)

図44-新しいポート設定ウィザード(ibtnボタン)その後、ポートが[ダイアグラム]フィールドに表示されます(図45)。

図45-作成されたibtnポート

出力方向を指定して、obtn_ledという別のポートを作成します(図43-44の手順を繰り返します)。

ibtnポートをobtn_ledに接続するだけで、[レイアウトの再生成]をクリックします。 図のようになります。 47。

図46-IPインテグレーターで組み立てられたプロジェクト

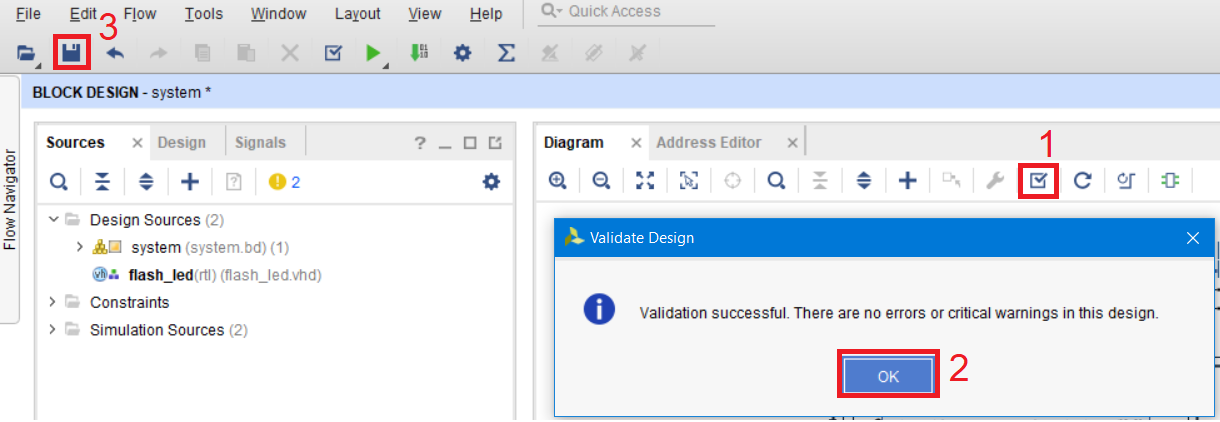

図46-IPインテグレーターで組み立てられたプロジェクト[デザインの検証]ボタンをクリックして、現在のブロックデザインにエラーがないことを確認します。 すべてが正しいが、Vivadoでメッセージが表示される場合。 [OK]をクリックして、現在のブロックデザインを保存します(図48)。

図47-IPインテグレーターでアセンブルされたプロジェクトの検証

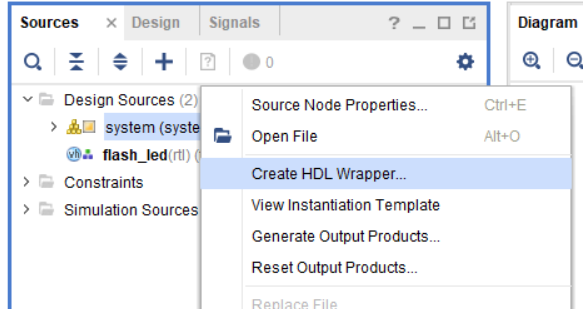

図47-IPインテグレーターでアセンブルされたプロジェクトの検証3.4。 合成と実装

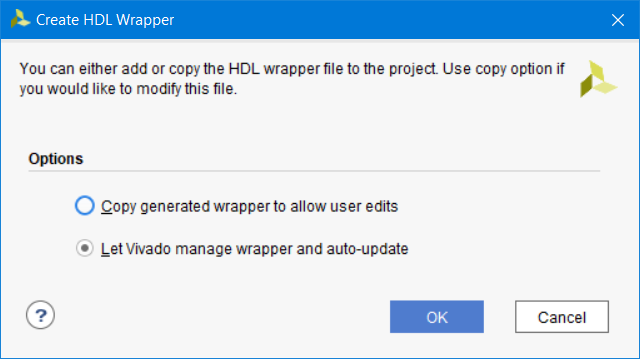

[Sources]タブに移動し、システムを右クリックして[Create HDL Wrapper](ブロックデザインのHDLラッパーを作成)を選択します。 48。

図48-プロジェクトラッパーの作成

その後、Vivadoはブロックデザインを変更するときにHDLラッパーを手動で更新するか、自動的に更新するかを提案します。 自動更新を終了し、[OK]をクリックします(図49)。

図49-HDLラッパーの更新オプション

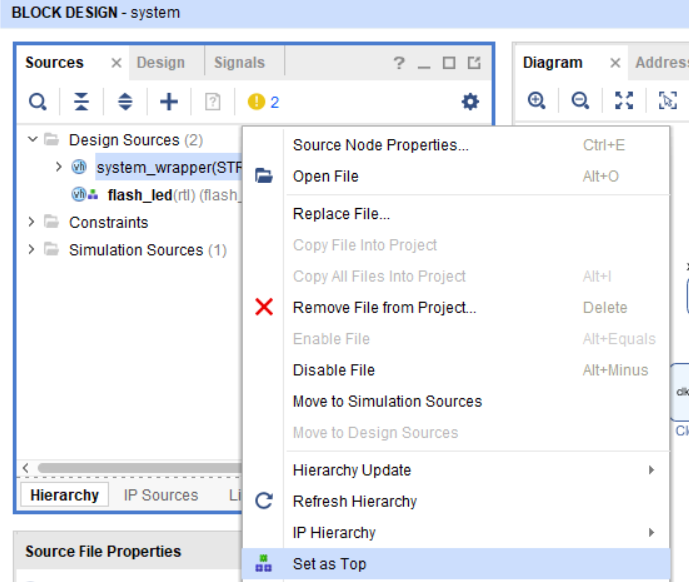

ここで、system_wrapperモジュールがTopモジュールであることを示します。 system_wrapperを右クリックして、[上部に設定]を選択します(図50)。

図50-system_wrapperモジュールをトップモジュールにする

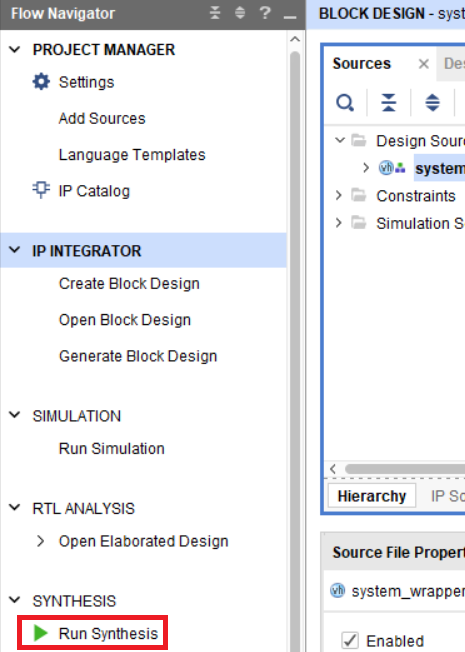

次に、Run Synthesisボタンをクリックして、system_wrapperモジュールの合成を実行します(図51)。

注:デバッグブロックを接続するために、実際にHDL挿入フロー[4]を使用しました。つまり、実際にILAブロックをコードに挿入し、チェーンを接続しました。 HDLまたはネットリストを介して、デバッグチェーンを作成して接続する方法に違いはありません。 最終的に、ECOは合成または実装されたネットリストと連携し、デザインチェックポイントに保存されます。

図51-プロジェクトの合成の開始

[Run Synthesis]ボタンをクリックした後、[OK]をクリックして、合成が完了するまで待ちます。

合成が完了すると、ウィンドウが表示され、実装を開始するか、合成結果を開くか、レポートを表示するように求められます。 合成結果を開きます(図52)。

図52-合成結果を開く

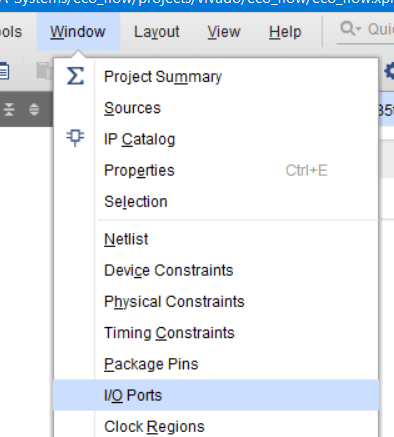

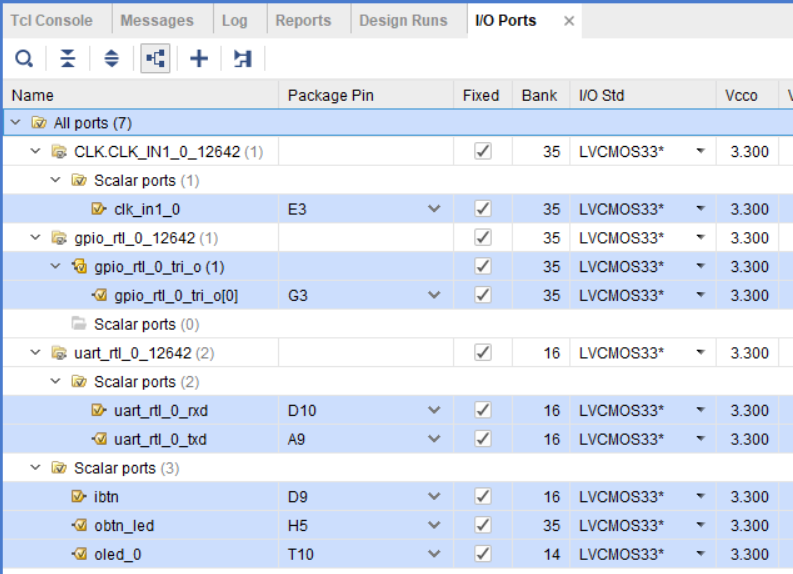

次に、プロジェクトの脚を接続します。 これは、ピンプレーナーを使用して行われます。 開くには、[ウィンドウ]→[I / Oポート]をクリックします(図54)。

図53-ピンを割り当てるためのウィンドウを開く

Artyのリファレンスマニュアル[12]を使用して、脚を割り当てます(図54)。

注意してください!!! 具体的には、UARTモジュールのrxとtxのレッグを混同しました!

図に従って脚を割り当てます。 54。

図54-プロジェクトレッグの割り当て(rxとtx UARTは特別に混同されています)

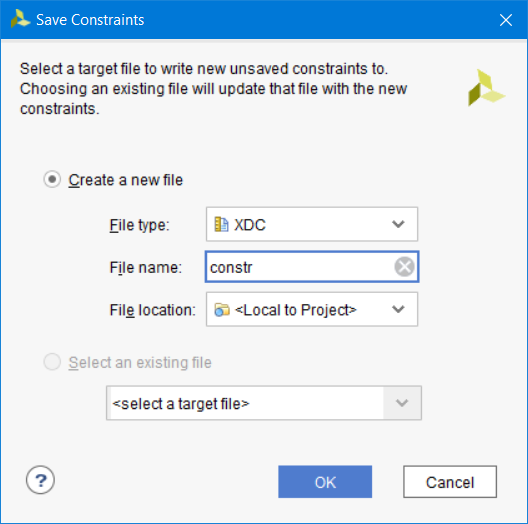

保存ボタンをクリックすると、Vivadoでプロジェクト制約ファイルを作成しなかったことが示され、作成を促すメッセージが表示されます。constrファイルの名前を入力し、[OK]をクリックします(図55)。

図55-設計制約ファイルの作成

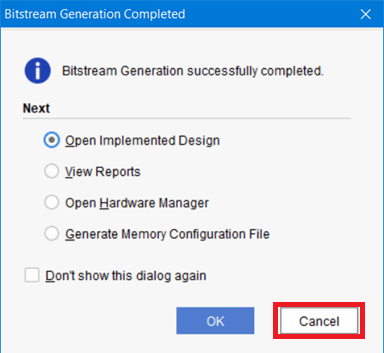

これで、プロジェクトを実装し、ファームウェアファイルを生成できます。 [Bistreamの生成]ボタンを押してから[OK]を選択し、手順が完了するまで待ちます(図56)。

図56-ビットストリームの生成ボタンの場所

ビットストリームの生成が完了すると、追加のアクションのウィンドウが表示されます。 [キャンセル]をクリックします(図57)

図57-ビットストリームの作成後の追加アクションのウィンドウ

3.5。 MicroBlaze用のプログラムの作成

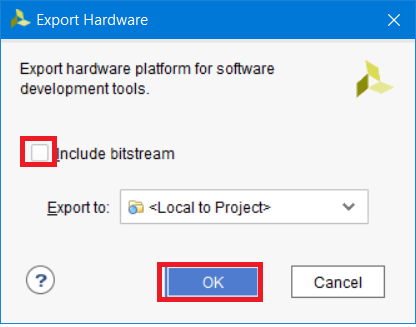

次に、MicroBlazeのソフトウェア開発を行います。 これは、ザイリンクスソフトウェア開発キット(SDK)環境で行われます。組み立てられたプロセッサシステムに関する情報(IPコア、AXIバス上のそれらのアドレス指定)をSDKに通知するには、SDKにエクスポートする必要があります。これは、ファイル→エクスポート→ハードウェアのエクスポートを使用して行われます(図58)。

図58-プロセッサシステム情報をSDKにエクスポート

表示されるウィンドウで、[ビットストリームを含める]チェックボックスをオンにしないでください。デフォルト設定のままにして[OK]をクリックします(図59)。

図59-エクスポートオプションウィンドウ

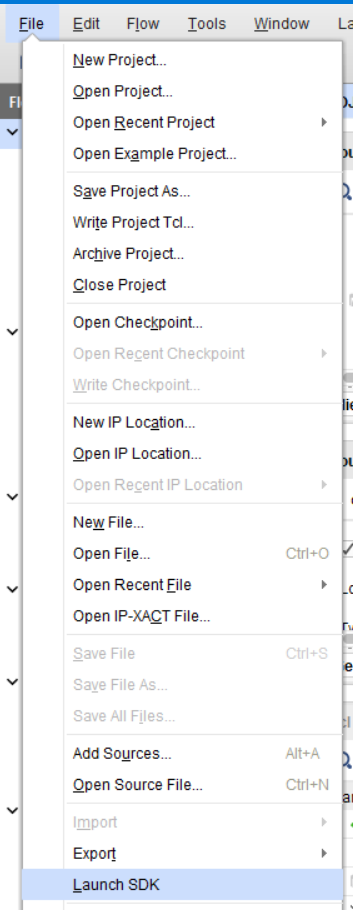

次に、SDKを実行します。これを行うには、ファイル→SDKの起動を選択します

図60-SDKの起動

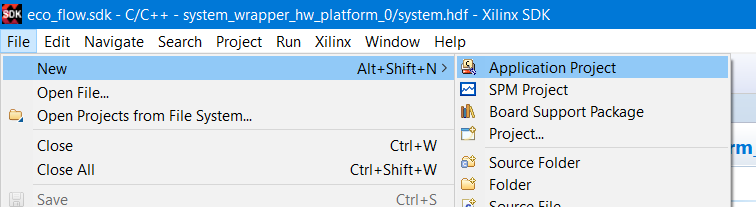

SDKのオーバーヘッドが完了するのを待ちます。完了後、新しいプロジェクトの作成を開始できます。[ファイル]→[新規]→[アプリケーションプロジェクト]を選択します。

図61-SDKでの新しいプロジェクトの作成

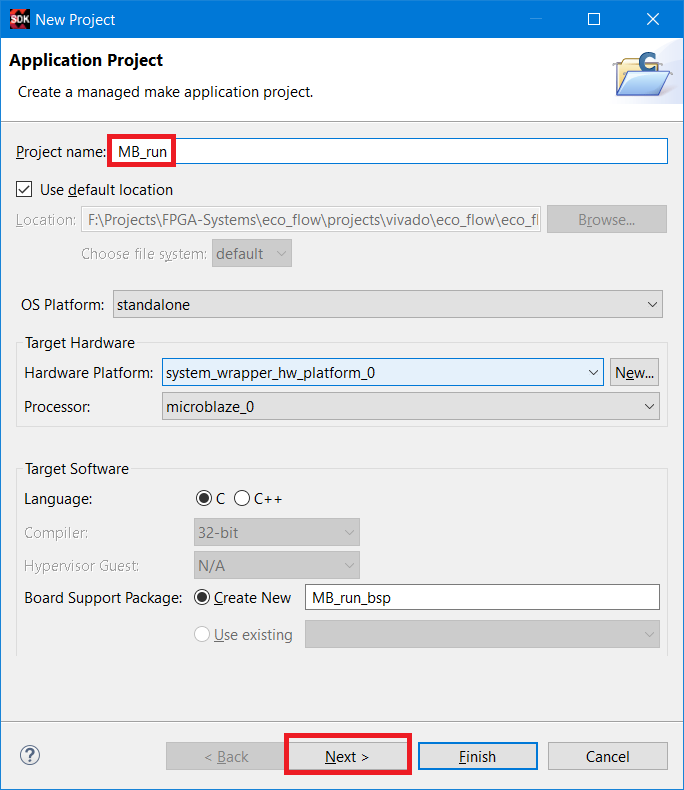

新しいMB_runプロジェクトの名前を入力し、[次へ]をクリックします(図62)

図62-新しいプロジェクトのセットアップ

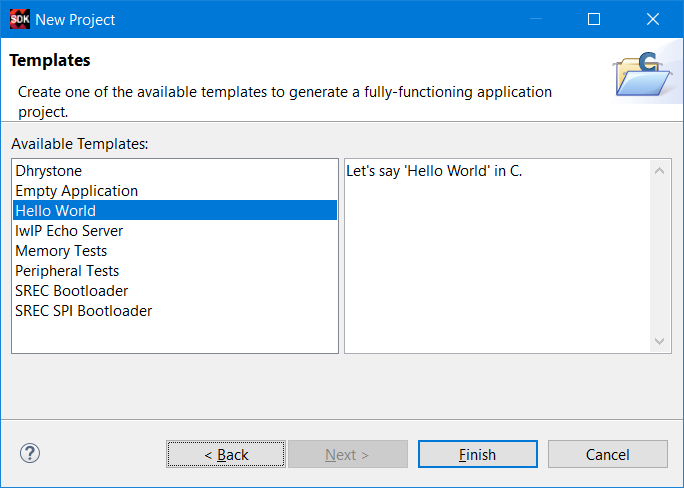

既製のテンプレートウィンドウで、Hello Worldアプリケーションの作成を選択し、[完了]をクリックします(図63)

図63-作成されたプロジェクトのテンプレートの選択

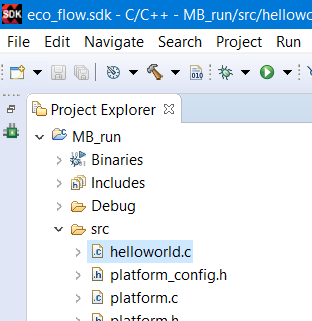

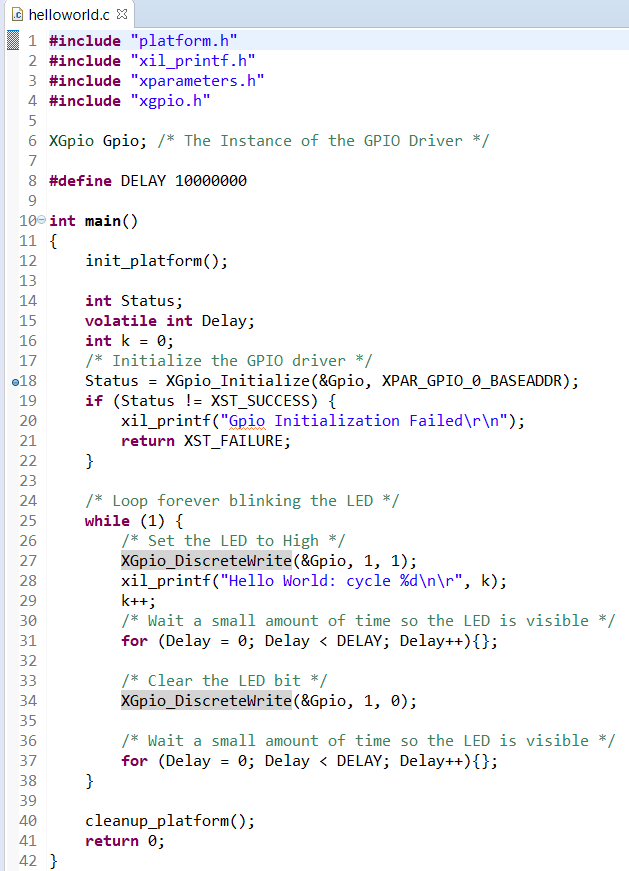

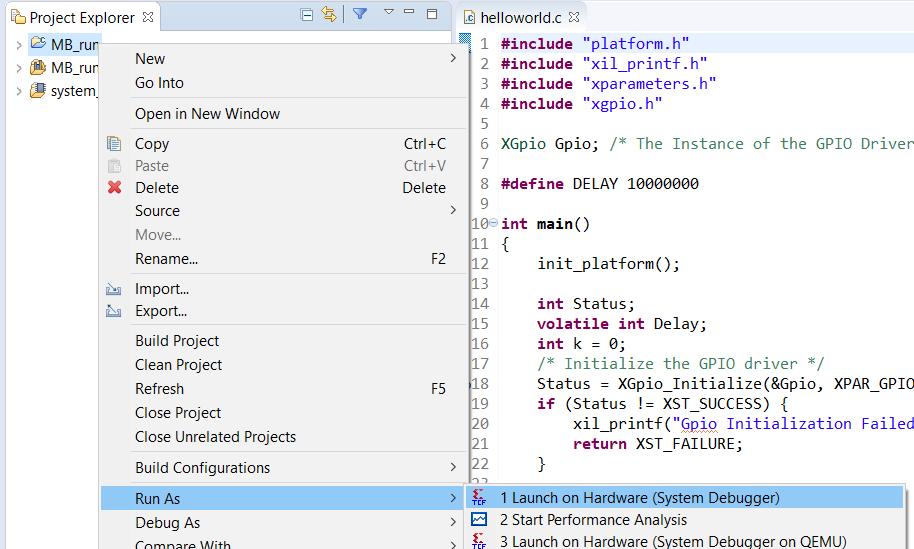

helloworld.cファイル(その場所を図64に示します)を開き、その内容をリスト3に示すプログラムコードで置き換えて、結果を保存します。

図64-helloworld.cファイルの場所 リスト3- helloworld.cファイルの置き換えられた内容

プログラムは、「Hello World:サイクル」を2秒に約1回送信し、LD1 LED(赤色のコンポーネント)を2秒に約1回点滅させます。3.6。プログラムを実行してデバッグする

プロセッサシステムのコードの記述とアセンブリを完了したら、次のことを確認する必要があります。

- BTN0が押されるとLD4 LEDが点灯する

- «Hello World: cycle» , , rx tx. , LD1.

- AXI-Lite UART

- .

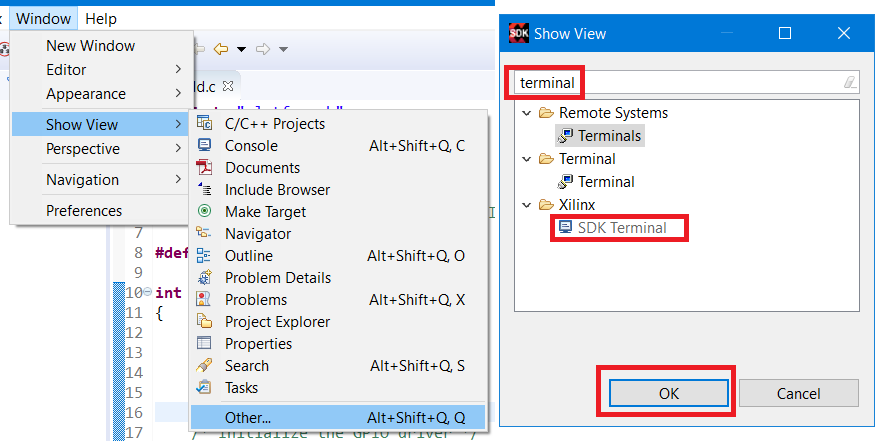

Arty . , UART. SDK. SDK , (. 65).

, Window → Show View → Others → Xilinx → SDK Terminal (. 65).

65 – SDK

65 – SDK, . 66. COM- .

図66-ターミナルSDKの構成

図66-ターミナルSDKの構成次に、Vivadoに移行してFPGAプログラミングを行います。

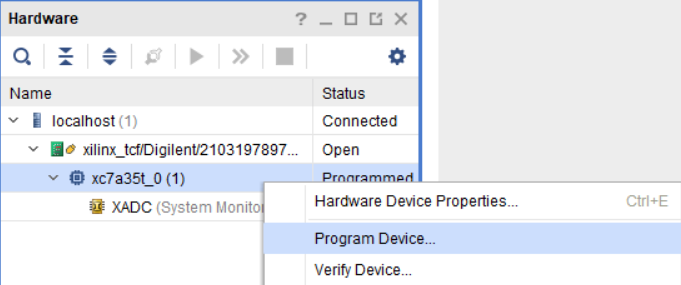

[ハードウェアマネージャーを開く]をクリックして、プログラミングモードとデバッグモードに入ります。[ターゲットを開く]を選択し、[自動接続]をクリックします(図67)

図67-ハードウェアマネージャーを開いてFPGAに接続する

リストからクリスタルを選択し、ファームウェアで満たします(図68)

図68-FPGAプログラミング

表示されるダイアログで、目的の.bitファームウェアファイルと.ltxプラグイン回路のリストが選択されていることを確認し(図69)、[プログラム]ボタンをクリックします。

図69-ファームウェアファイルと回路のリストの選択

図69-ファームウェアファイルと回路のリストの選択, LD4 , BTN0 LD4.

UART LD1.

SDK, MB_run, Run As → Launch on Hardware (System Debugger), . 70. , .

70 –

70 –, , LD1 , SDK Terminal , rx tx .

, , UART - .

Vivado. , , ILA: AXI UART, . ILA (. 71).

71 – ILA

, , , , . , , UART - . «», , , , ILA.

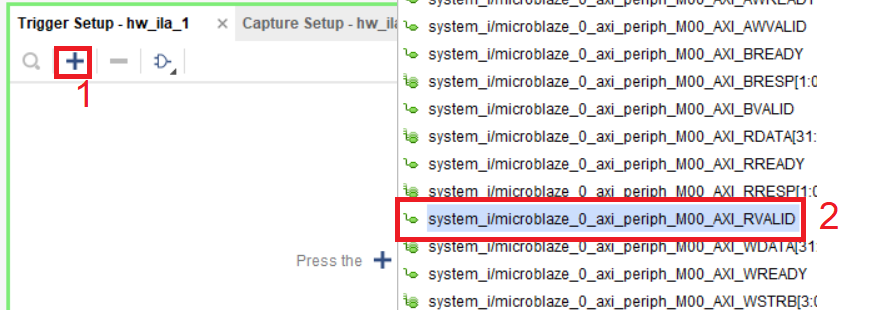

hw_ila_1 .

Trigger Setup , . , . 72. OK.

72 – ILA

72 – ILA: AXI-Lite, . , . , , [14].

. RVALID «1», , , «1». , . 73. .

73 – ILA

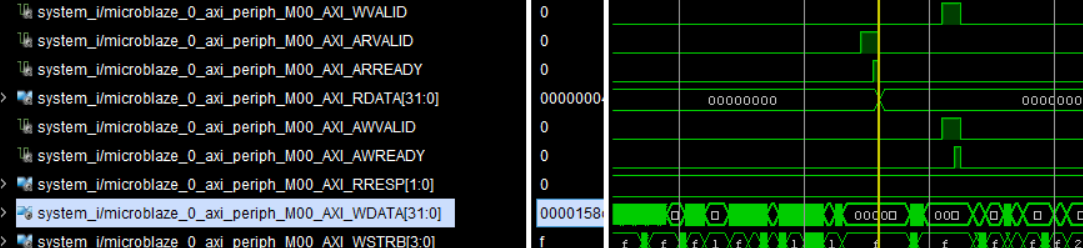

73 – ILA, , , . . 74

74 – AXI-Lite

表示されたバスステータスをASCIIに変更します。これを行うには、バスを右クリックし、[基数]、[ASCII]の順に選択します(図76)。

図75-* WDATAバス上のデータ表現の選択[31:0]

図75-* WDATAバス上のデータ表現の選択[31:0]その後、プロセッサが送信するメッセージのバス部分を確認します。これにより、トランザクションが正しく進行していることが部分的に確認されます(図76)。

図76-* WDATAバス上のデータのASCII表現[31:0]

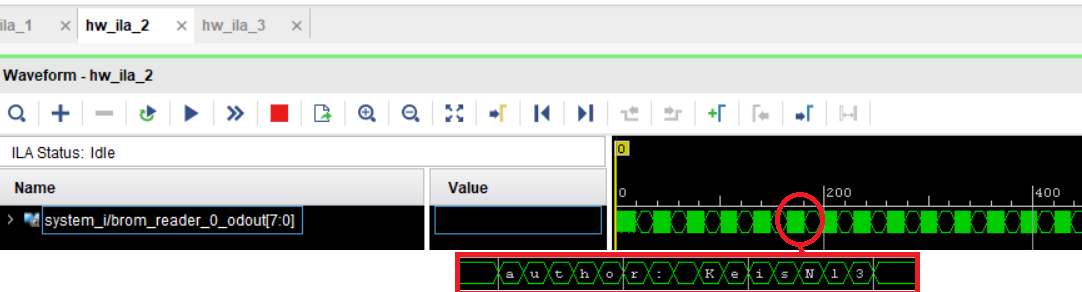

図76-* WDATAバス上のデータのASCII表現[31:0]図71から図71までの手順を繰り返してみてください。ブロックメモリリーダーの出力に接続されているhw_ila_2の場合は76。トリガーは必要ありません。すべてが正しく行われている場合、画像は図のようになります。77。

図77-ブロックメモリから読み取ったデータ

図77-ブロックメモリから読み取ったデータこれでテストプロジェクトのアセンブリが完了し、ネットリストの編集とECOモードでの作業を開始できます。

4. ECO

:

- BTN0

- UART , ( rx tx)

- ( ASCII:”author: KeisN13”).

, ECO, Design Checkpoint (DCP). DCP, (post route).

Vivado DCP, DCP «» DCP .

edited_dcp. (. 78)

78 – DCP

78 – DCPDCP , «_/_.runs/_/___routed.dcp» (. 79) edited_dcp.

79 – DCP

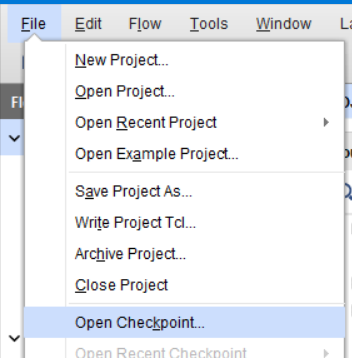

79 – DCPVivadoに移動し、DCPを開きます。これを行うには、[ファイル]→[チェックポイントを開く]をクリックします(図80)。

図80-DCPを開く

図80-DCPを開くedited_dcpフォルダ内のコピーされたDCPファイルの場所を選択し、OKをクリックします。

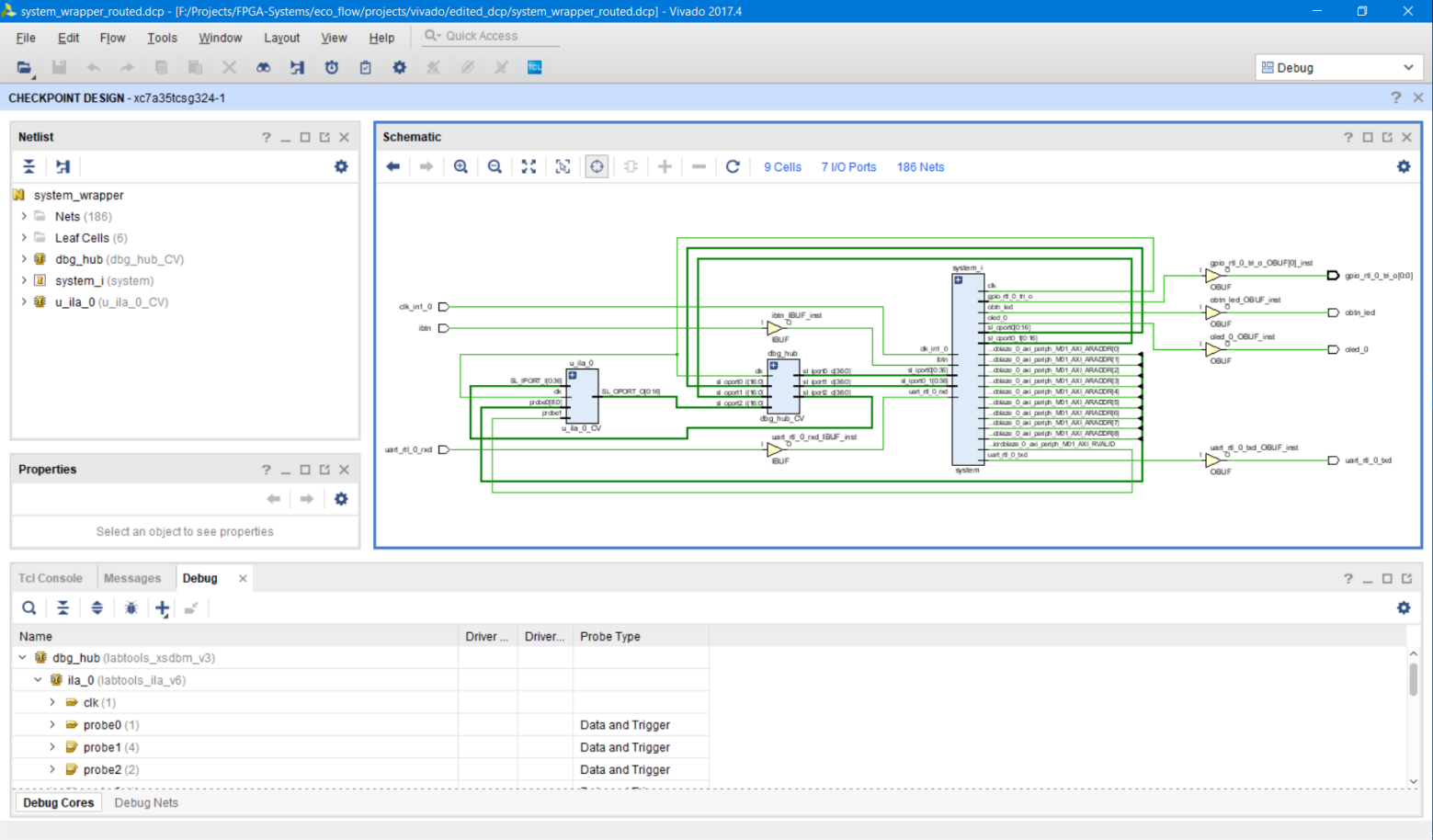

DCPを開くと、デフォルトでデフォルト(またはパースペクティブ)ビューが開きます。これは、前回DCPを開いたときに使用したビューです(図81)。図81-VistaデバッグオープンDCP

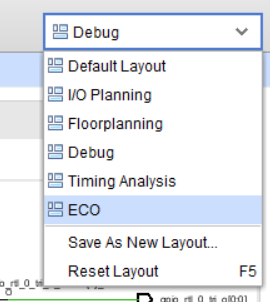

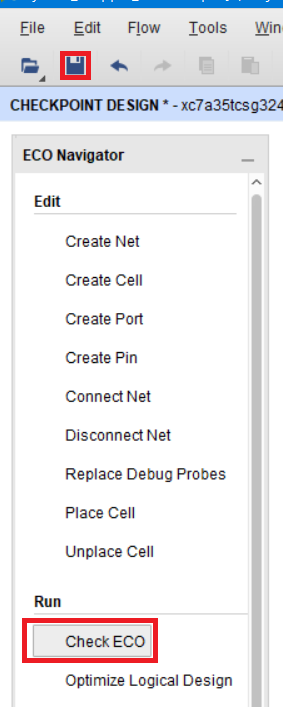

DCPにはいくつかの動作モードがありますが、今日はECOフローに関心があります。ECOモードに切り替えるには、ビューを変更する必要があります。これを行うには、ドロップダウンリストから右上隅のECOを選択します(図82)。

図82-ECOモードへの切り替え

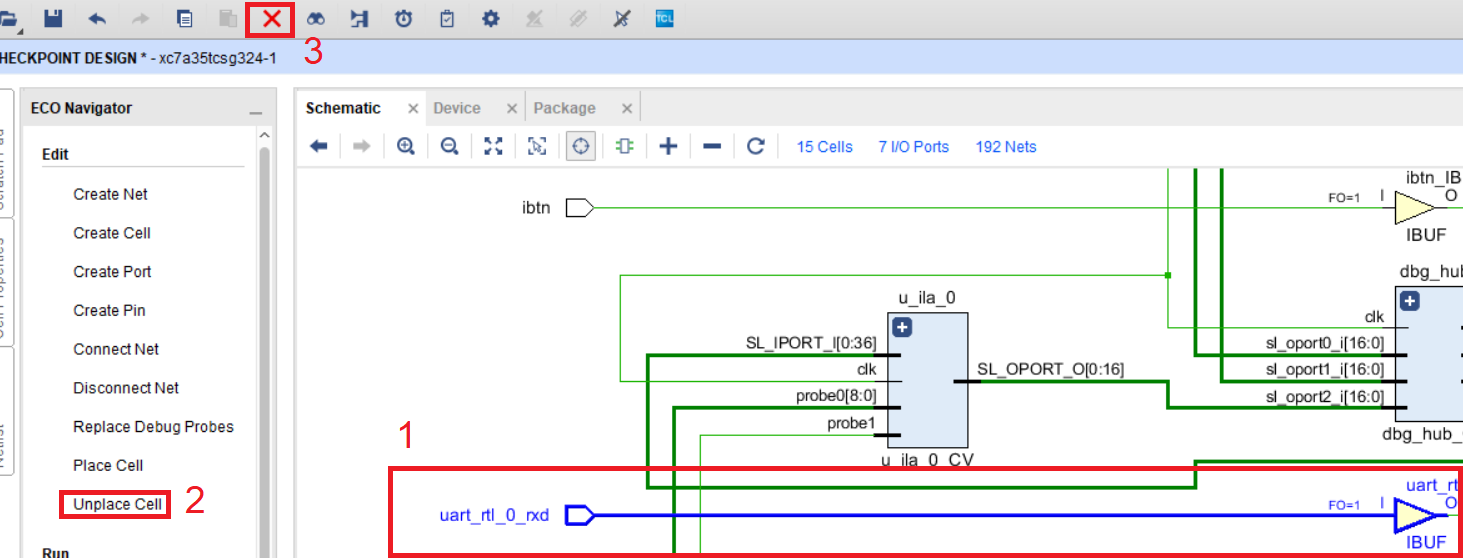

, ECO (. 83). , .

83 – ECO

83 – ECO5. ECO:

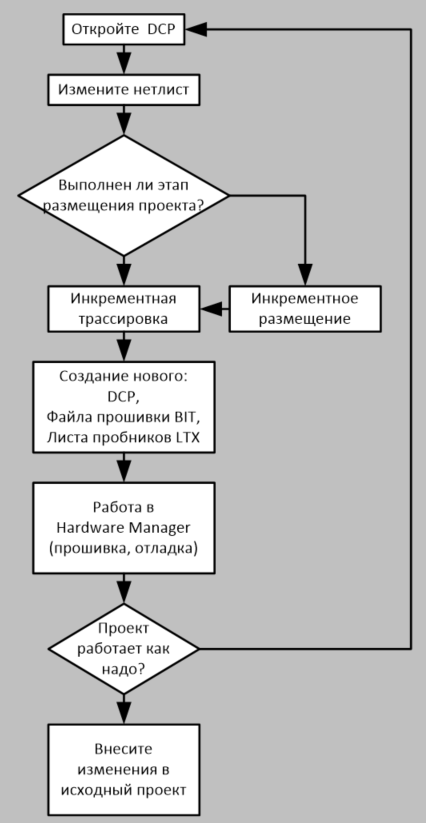

ECO , . 84. DCP. DCP , / Tcl-. , , , . , (, .bit) (.ltx). « », , . – DCP .

84 – ECO

84 – ECO. [3] Vivado ECO Flow.

ECO , , .

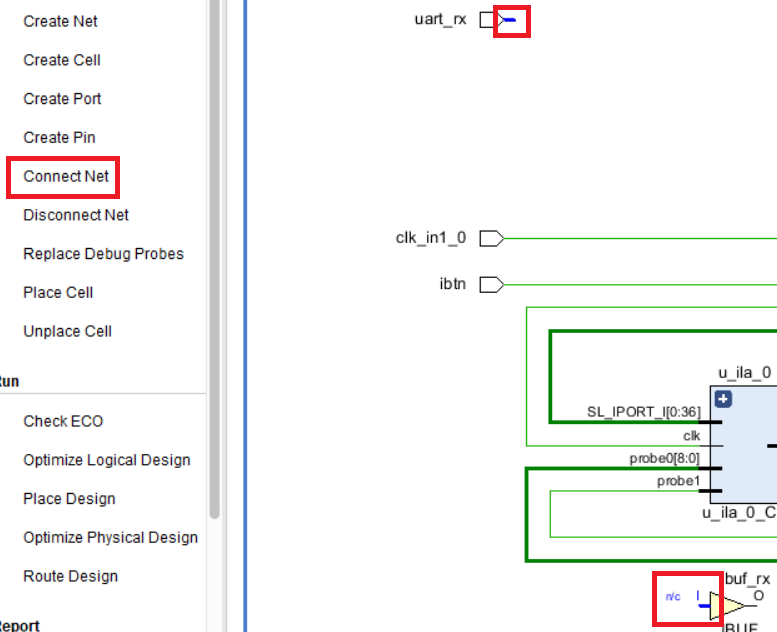

ECO Navigator, . ECO Navigator .

Edit (. 85): ,

85 – Edit

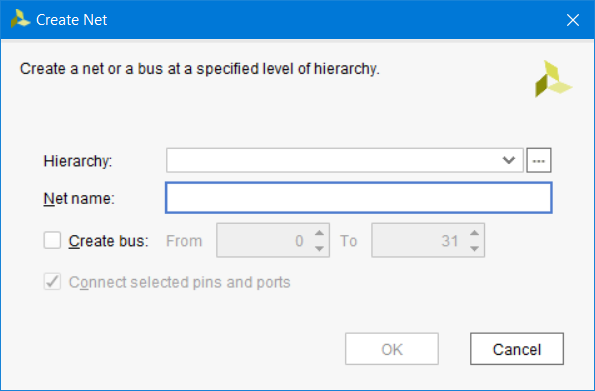

85 – EditCreate Net: , . , . . pin port, , Connect selected pins and ports (. 86).

86 – Create Net

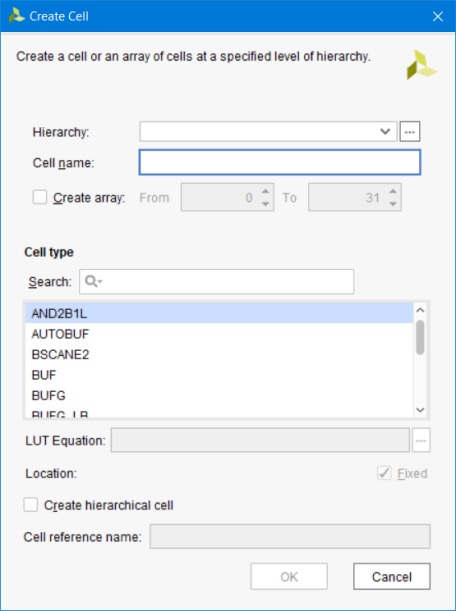

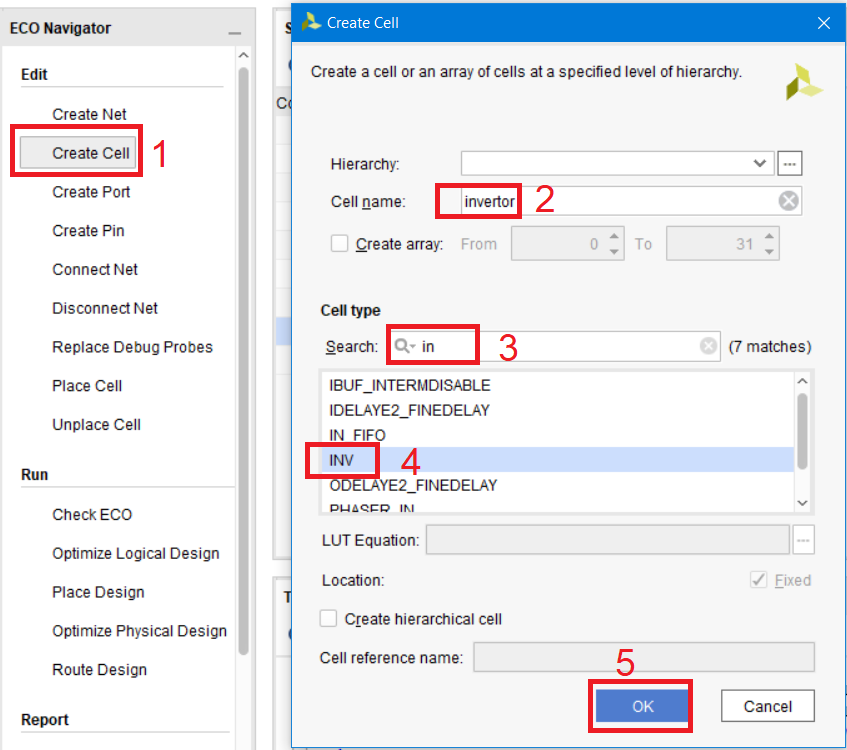

86 – Create NetCreate Cell: , . . , , black box. LUT, , (. 87).

87 – Create Cell

Create Port: . : , , .. (. 88).

88 – Create Port

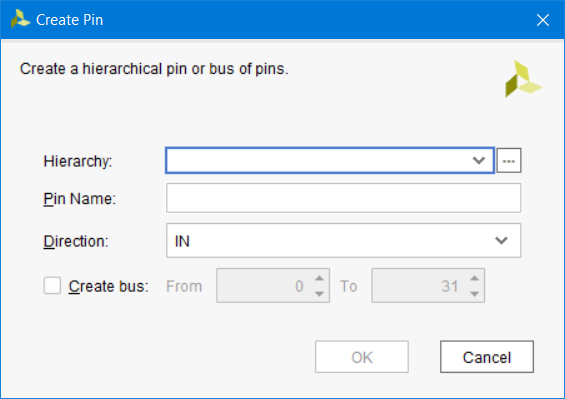

Create pin: . ( cell) . create_port. , (. 89).

89 – Create Pin

89 – Create PinConnect Net: . . , .

Disconnect Net: , . , cell, , .

Replace Debug Probes: , ILA / VIO (Virtual Input Output), , .

Place Cell: cell .

Unplace Cell: cell .

Run

Run , .

ECOをチェック:エラーチェックを実行(DRC-デザインルールチェック)注:Vivadoでは、ECOモードコマンドを使用してネットリストに多くの変更を加えることができます。ただし、プロジェクトに導入された論理的な変更は、実現不可能な物理的実装につながる可能性があります。 ECOフロールートの初期段階でエラーを排除するために、プロジェクトの実装を計画する前に、ECOのチェックを開始する必要があります。論理設計の最適化:場合によっては、opt_designコマンドおよび対応するオプション[9]を使用してネットリストの最適化を実行することをお勧めします。 [論理設計の最適化]を使用すると、opt_designコマンドに適切なTcl引数を入力できるダイアログボックスを呼び出して、オプション行で設定できます。配置設計:現在のネットリストのコンポーネントの増分(つまり、以前のネットリストに基づく)配置を実行します。 place_designコマンドの最後にコンソールに表示されるIncremental Placement Summaryレポートでは、変更が行われる前の元のDCPにあった前の配置の結果の再利用に関する統計を表示できます。 Place Designをクリックすると、place_design [9]コマンドの対応するオプションを設定できるウィンドウが表示されます。インクリメンタル実装の詳細については、インクリメンタルコンパイルセクションの[3]を参照してください。物理設計の最適化:場合によっては、物理的な最適化を実行する必要があります(phys_opt_design [9]コマンド)。 [物理デザインの最適化]をクリックして呼び出されるダイアログボックスでは、phys_opt_designコマンドの適切なオプションを入力できます。Route Design:選択に応じて、ネットリストに加えられた変更の増分トレース、選択されたピンまたは回路のトレースを実行できるダイアログボックスを開きます。再利用された腐食チェーンの割合が75%未満の場合、通常のネットリストトレースが生成されます。インクリメンタル実装の詳細については、インクリメンタルコンパイルセクションの[3]を参照してください。レポートセクションこのセクションでは、使用されたリソース、時間特性、クロックドメインの共通部分などのレポートを含む、変更されたネットリストに必要なレポートを生成できます。プログラムセクションこのセクションのツールを使用すると、新しいDCPに加えられた変更を保存し、FPAファームウェアファイルを作成し、ILAを介してデバッグされた回路の新しいリストを作成できます。Scratch

, , , . Con , PnR .

Scratch (. 90). , , . , [3] Vivado ECO Flow → Scratch Pad → Scratch Pad Pop-up Menu.

90 – Scratch

90 – Scratch6.

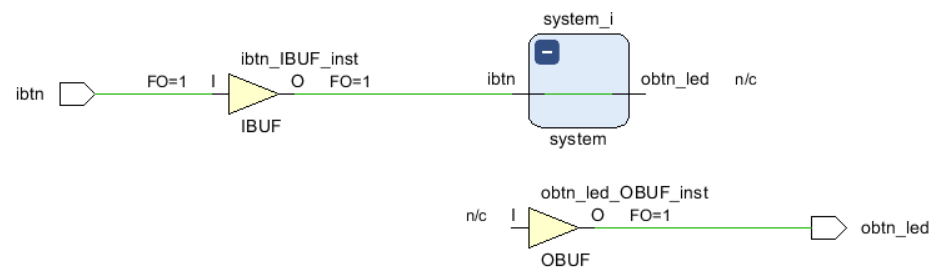

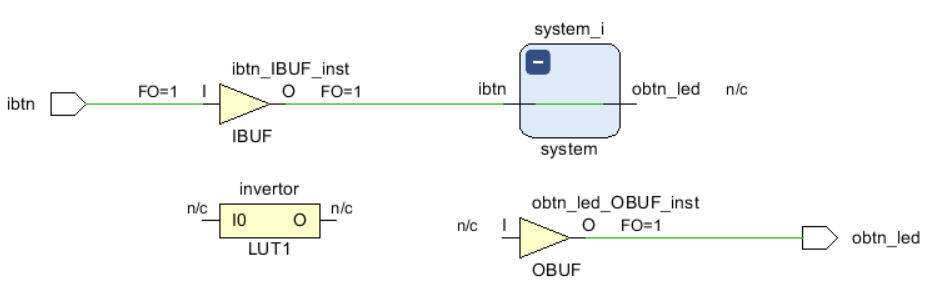

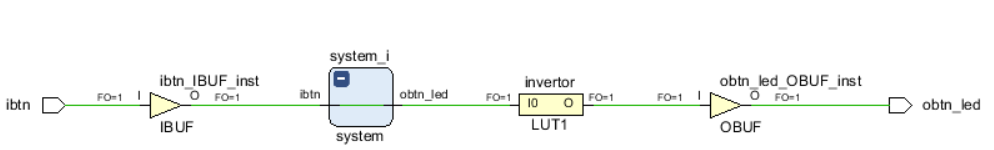

. , , . , LD0 , BTN0 . , , .

6.1。

, ibtn, , F4. , , .

91 –

91 –, ibtn. ibtn LD1 ( obtn_led). ibtn, Expand Cone To Flops or I/Os. Regenerate Layout (. 92)

92 – ,

92 – ,«» (. 93).

93 – «» ibtn obtn_led

93 – «» ibtn obtn_led, , , . system_i . obtn_led system_i I obtn_led_OBUF_inst, Edit Disconnect Net.

94 –

94 –Regenerate Layout , (. 95)

95 –

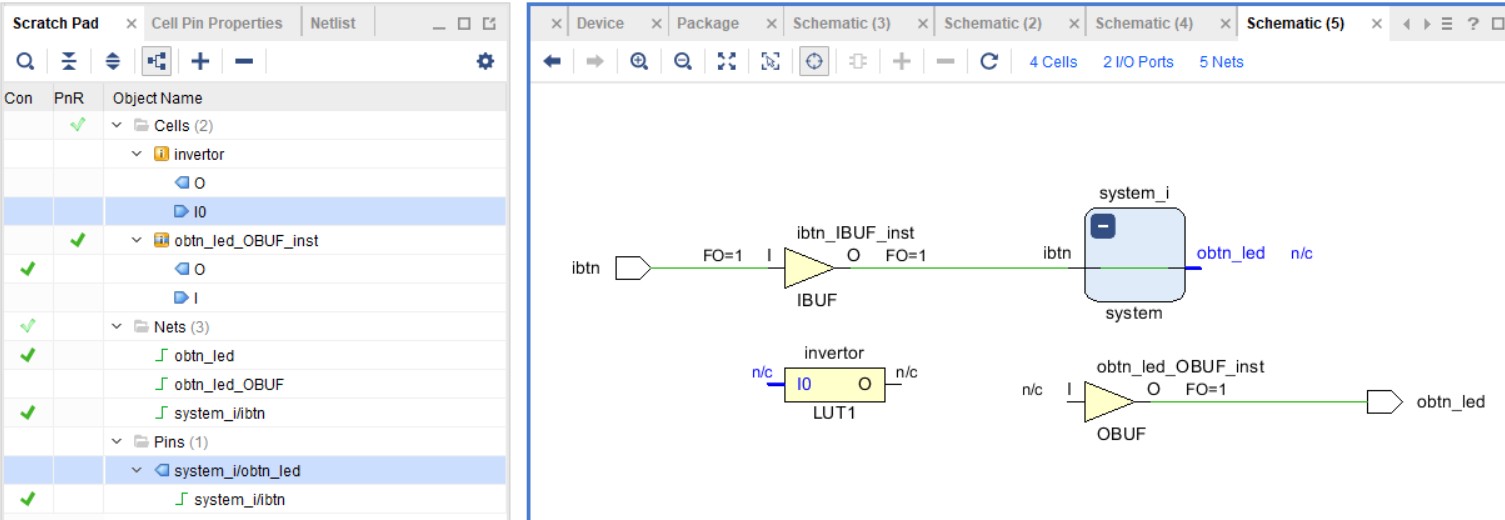

95 –Scratch Pad, .

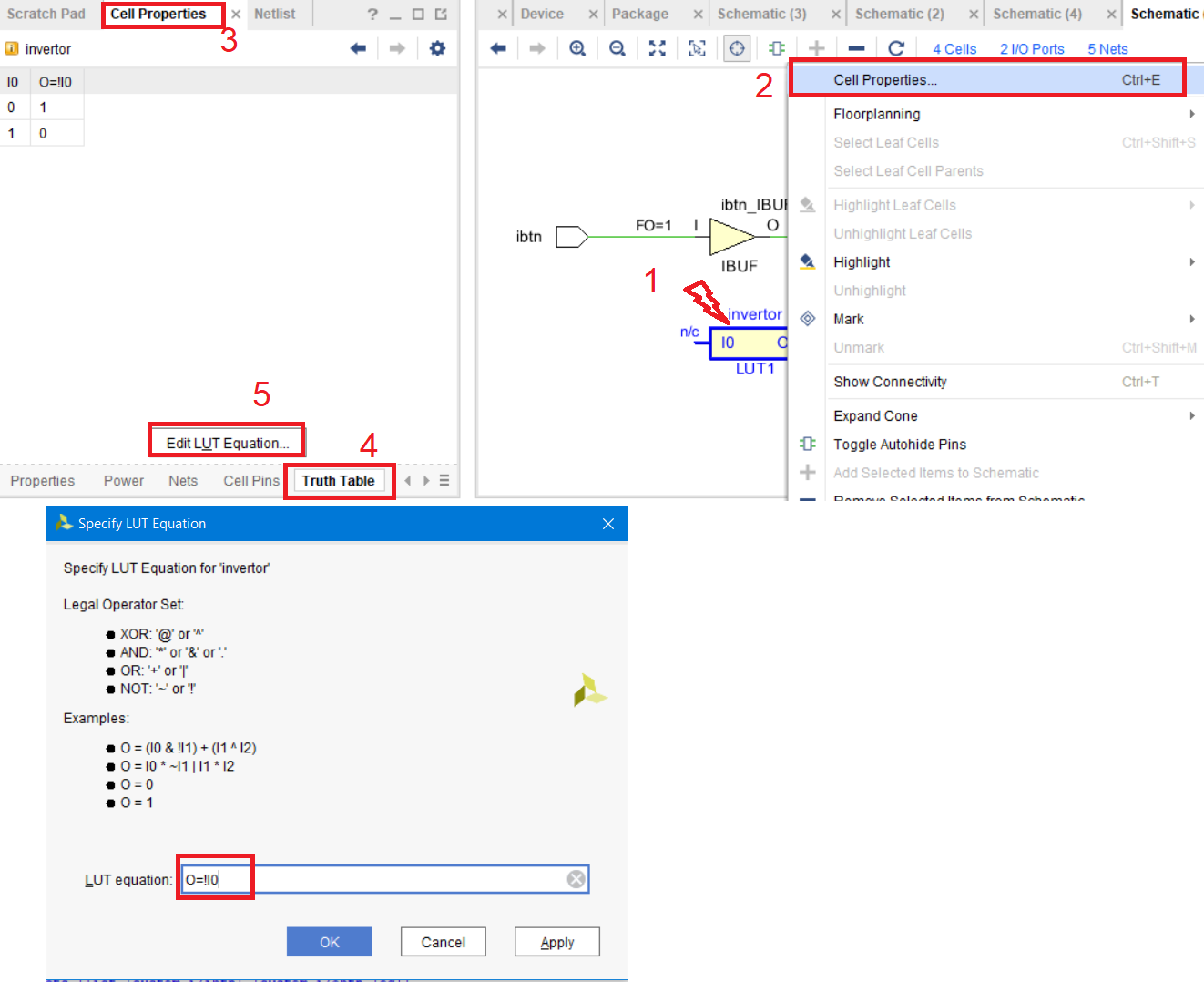

. Edit Create Cell, invertor, INV OK (. 96)

96 –

96 –INV (. 97)

97 –

97 –, LUT. , LUT , , , Cell Properties, Truth Table Edit LUT Equation… (. 98).

98 – LUT

98 – LUT. , Scratch Pad I0 invertor obtn_led system_i.

99 –

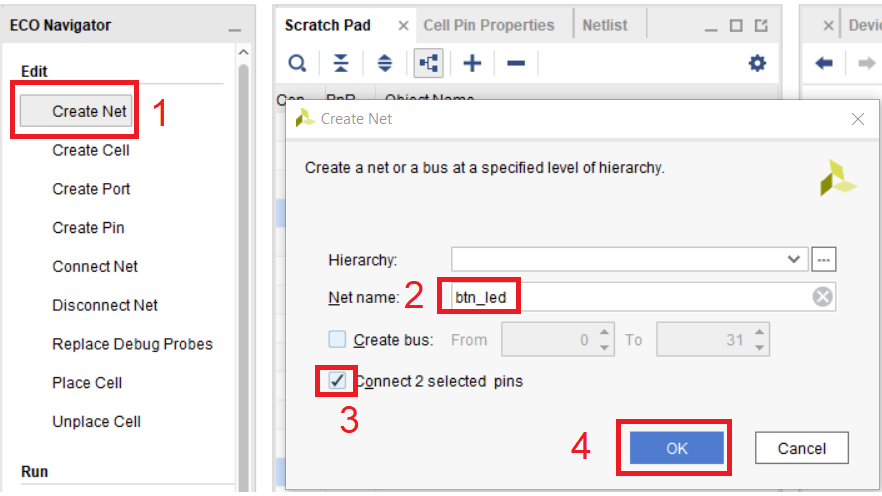

99 –. Edit Create Net. btn_led, (. 100)

100 –

100 –. Regenerate Layout (. 101)

101 –

101 –O invertor I obtn_led_OBUF_inst. -, . btn_led_o. . 102

102 –

DCP , (. 103).

103 – ECO

103 – ECO配置とトレースを実行しなかったため、これを示すエラーが多数表示されます。

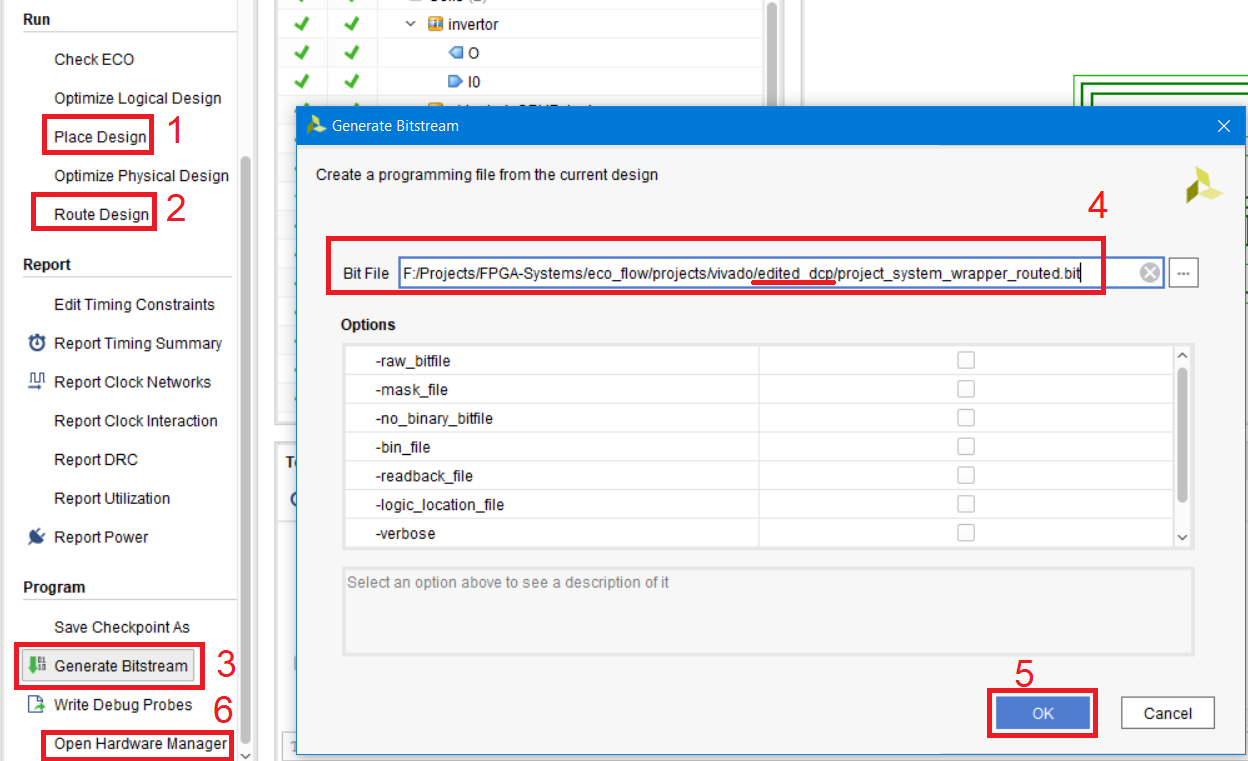

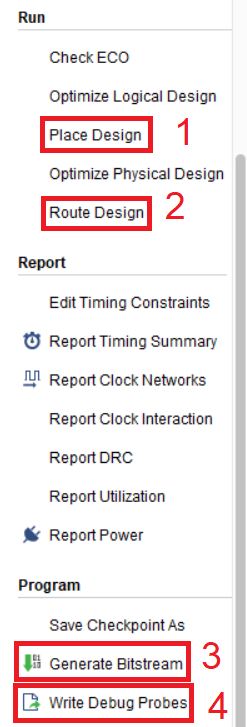

それでは、ファームウェアファイルを少し生成してみて、変更が正しく行われたかどうかを確認しましょう。これを行うには、実行セクションの手順を順番に実行する必要があります。すべてが明確でオプションがないわけではありません。デフォルトではすべてが残っています(図104)。

[デザインの配置]をクリックし、オプションを入力せずに[OK]をクリックします。操作の完了を待ってから、[ルート設計]をクリックし、表示されるウィンドウで[インクリメンタルルート]を選択して、[OK]をクリックします。

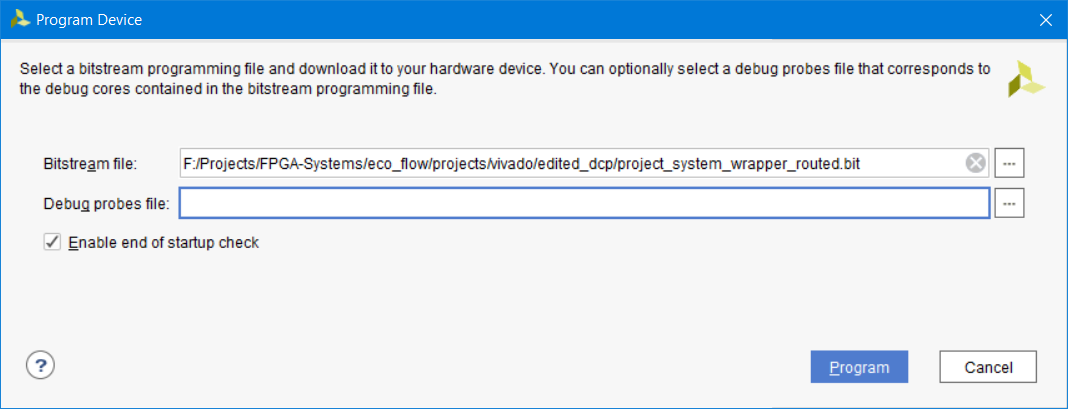

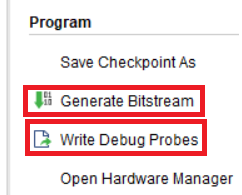

その後、Generate Bitstreamをクリックしてビットファイルを生成します。ファイルパスフィールドにedited_dcpフォルダが指定されていることを確認してください。その後、ハードウェアマネージャーを開いてFPGAをフラッシュします。

図104-.bitファームウェアファイルを取得する手順のシーケンス

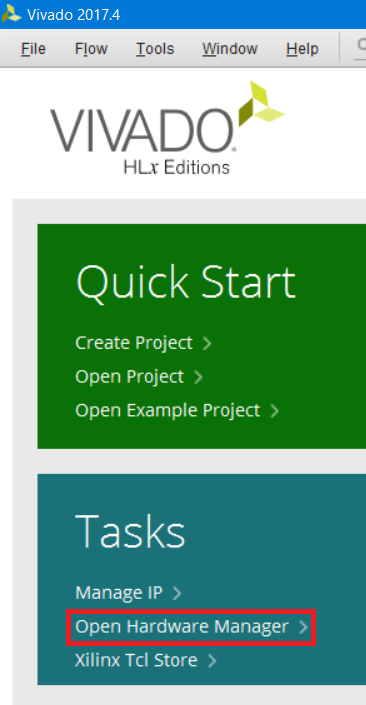

図104-.bitファームウェアファイルを取得する手順のシーケンス, Vivado. , Vivado Hardware Manager (. 105). , .bit ILA .ltx

105 – Hardware Manager Vivado

, .67-69 . , , edited_dcp (. 106).

106 –

, LD0 , BTN0 .

6.2。 /

ECO . brom_reader, , , . BROM INIT, .

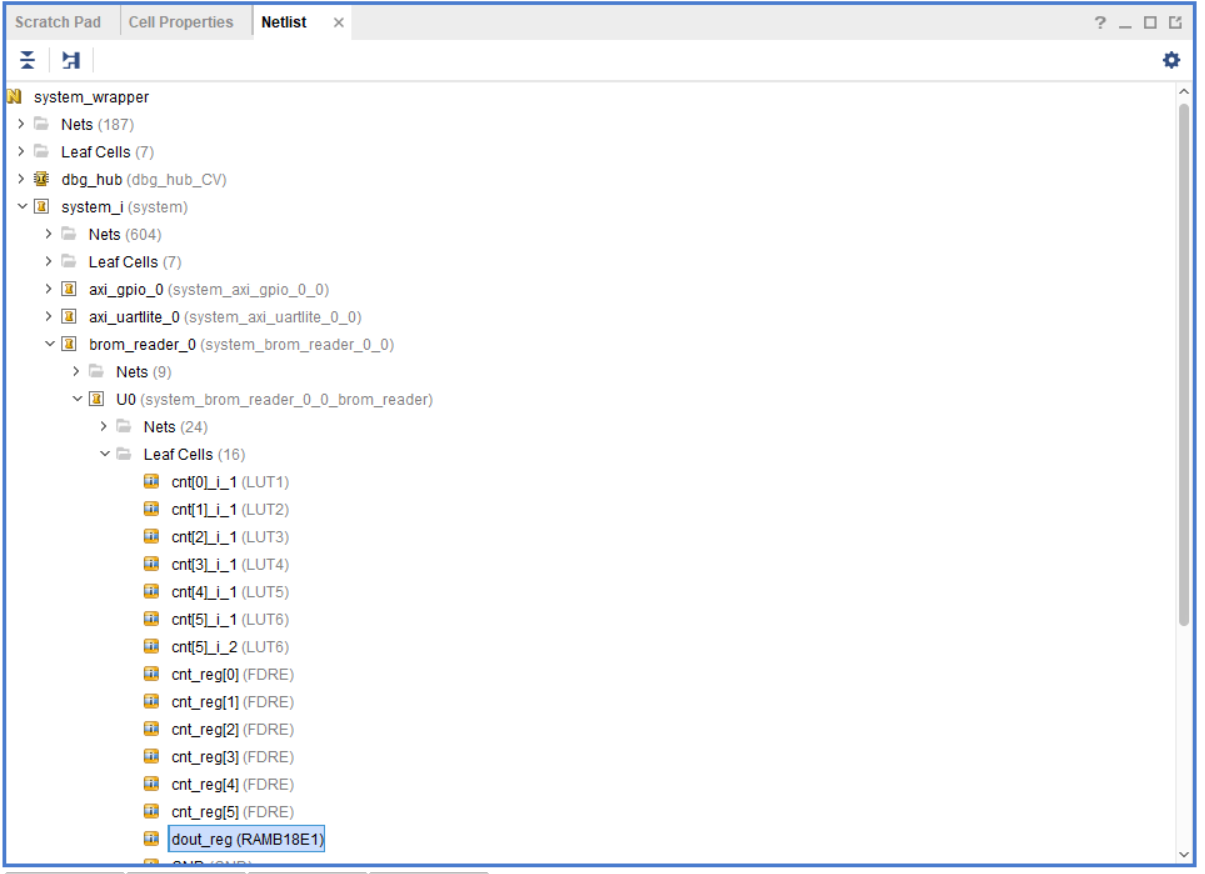

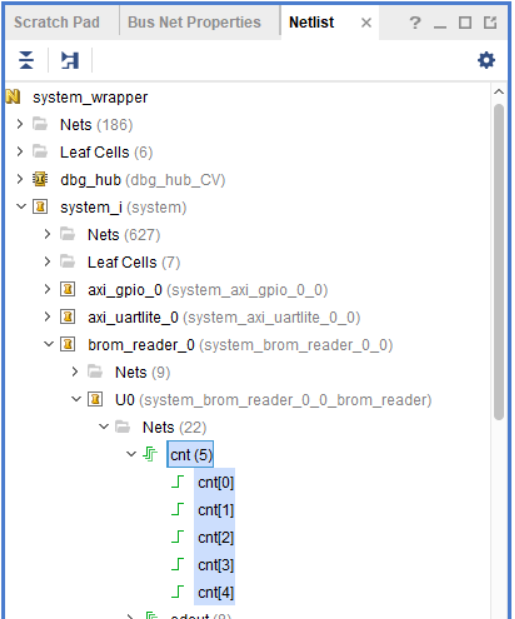

Netlist brom_reader (.107).

107 – brom_reader

107 – brom_reader, , Cell Properties (. 108). Properties INIT.

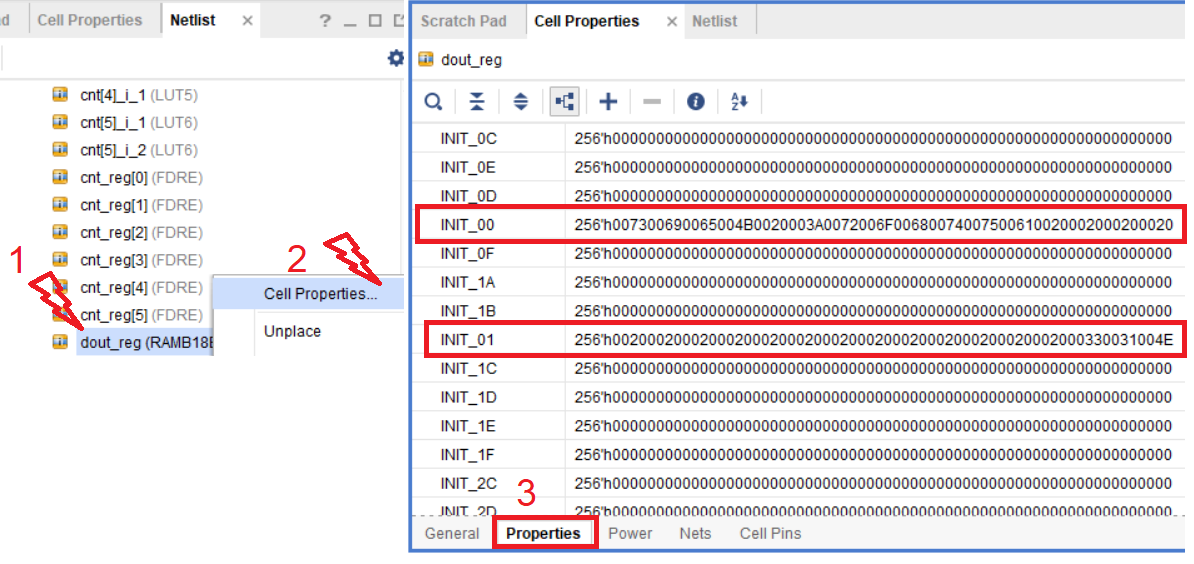

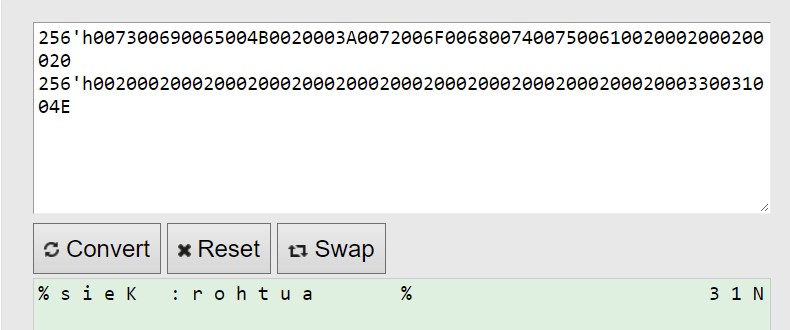

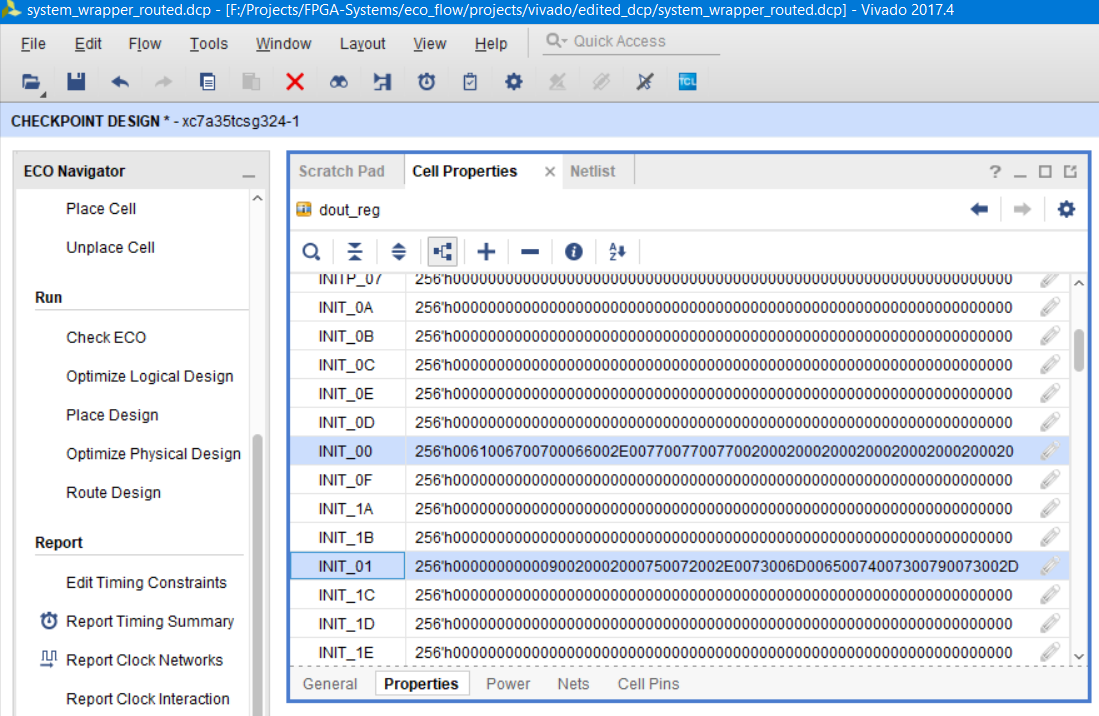

図108-選択したブロックメモリのINITプロパティご覧のとおり、ブロックメモリの初期化値はINITプロパティに保存されます。多くのプロパティの中で、興味があるのはINIT_00とINIT_01のみです。これら2つのプロパティの内容、HEXからASCIIへのコンバーター[15]をコピーすると、図に見られる碑文が得られます。77、ただし逆の順序で記述されています(図109)図109-ASCII形式のINITプロパティの内容

図108-選択したブロックメモリのINITプロパティご覧のとおり、ブロックメモリの初期化値はINITプロパティに保存されます。多くのプロパティの中で、興味があるのはINIT_00とINIT_01のみです。これら2つのプロパティの内容、HEXからASCIIへのコンバーター[15]をコピーすると、図に見られる碑文が得られます。77、ただし逆の順序で記述されています(図109)図109-ASCII形式のINITプロパティの内容

コンポーネントプロパティを変更するには、鉛筆アイコンをクリックして新しい値を入力するか、Tclコンソールとset_ptopertyコマンドを使用します。

図110に従ってプロパティ値を置き換え、結果を保存します。

INIT_00:256'h0061006700700066002E00770077007700200020002000200020002000200020

INIT_01: 256'h0020002000200020002000750072002E0073006D00650074007300790073002D

110 – INIT ASCII

110 – INIT ASCII, . Generate Bitstream . .ltx, (. 111).

111 –

111 –Hardware manager FPGA .bit .ltx (.112). , edit_dcp.

112 –

112 –, . 73-75 ( hw_ila_2, ASCII ). , . 113.

113 –

113 –, , , , . , , , , MMCM PLL . , , , , (Report Timing Summary ..).

6.3. ILA

, ECO , . , , « ». , gnd vcc.

, , , .

ECO, , ; .

: , « », : . : , , Disconnect Net . «DONT_TOUCH» ( «unrote») – Disconnect Net . .

, , . , brom_reader. . , (. 114). cnt, , 5.

114 –

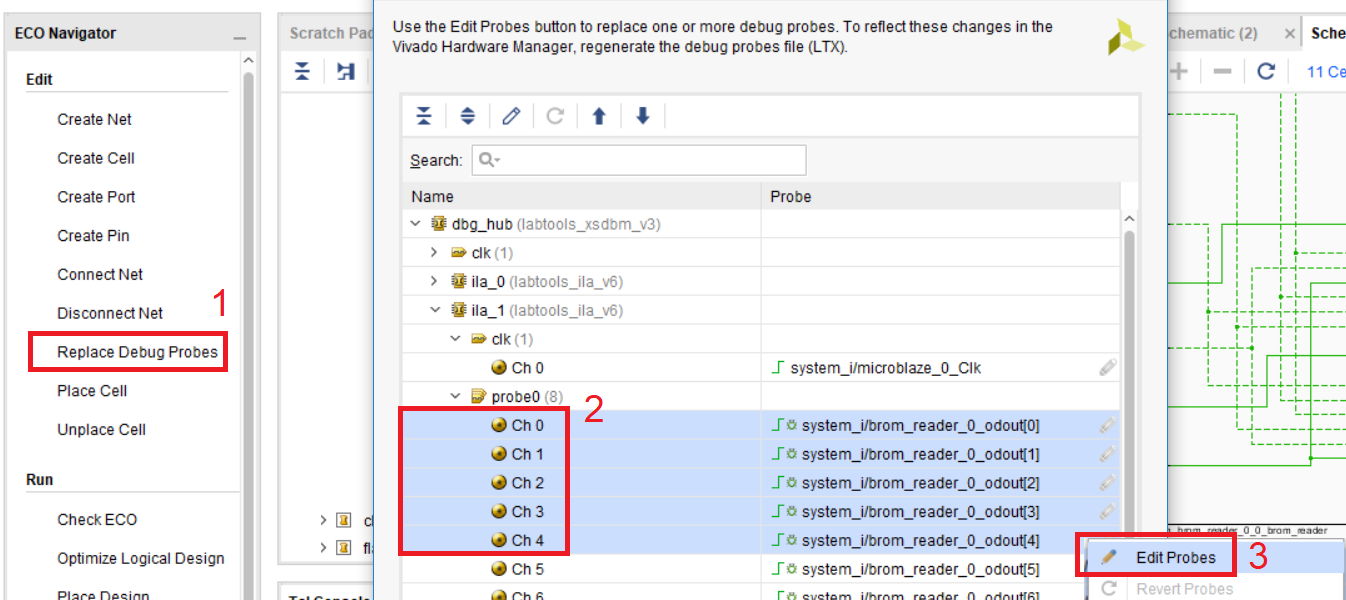

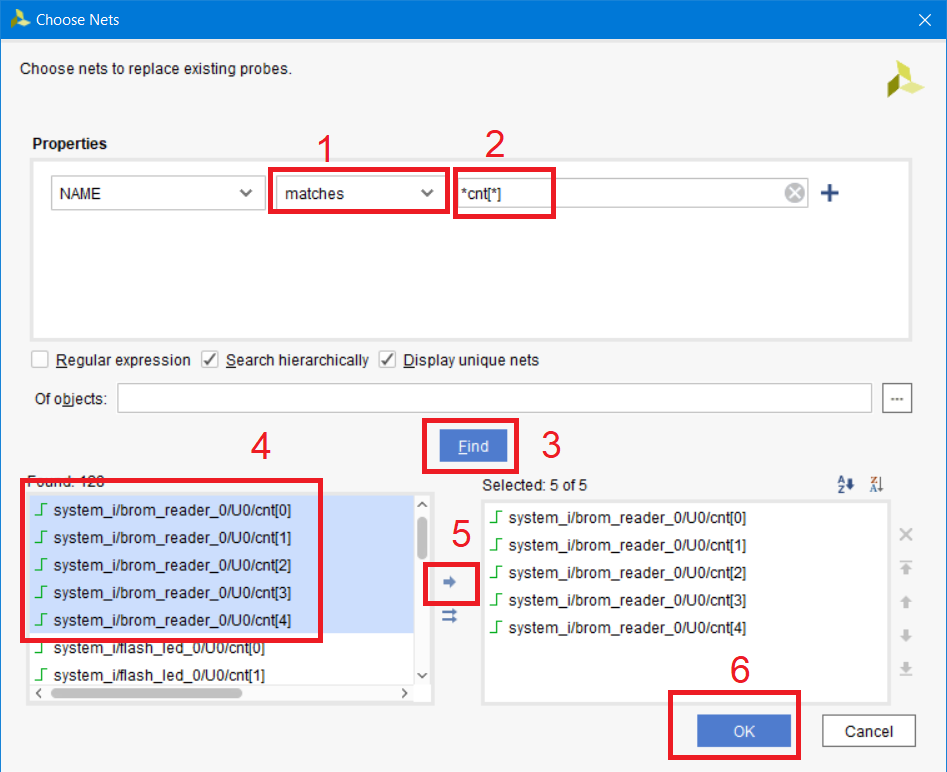

Replace Debug Probes. 31, 5 , ila_1, Edit Probes (. 115). ila, . , .

115 –

115 –, *cnt[*]. , . , 5 , 5 . contains match tcl . Tcl , .

116 –

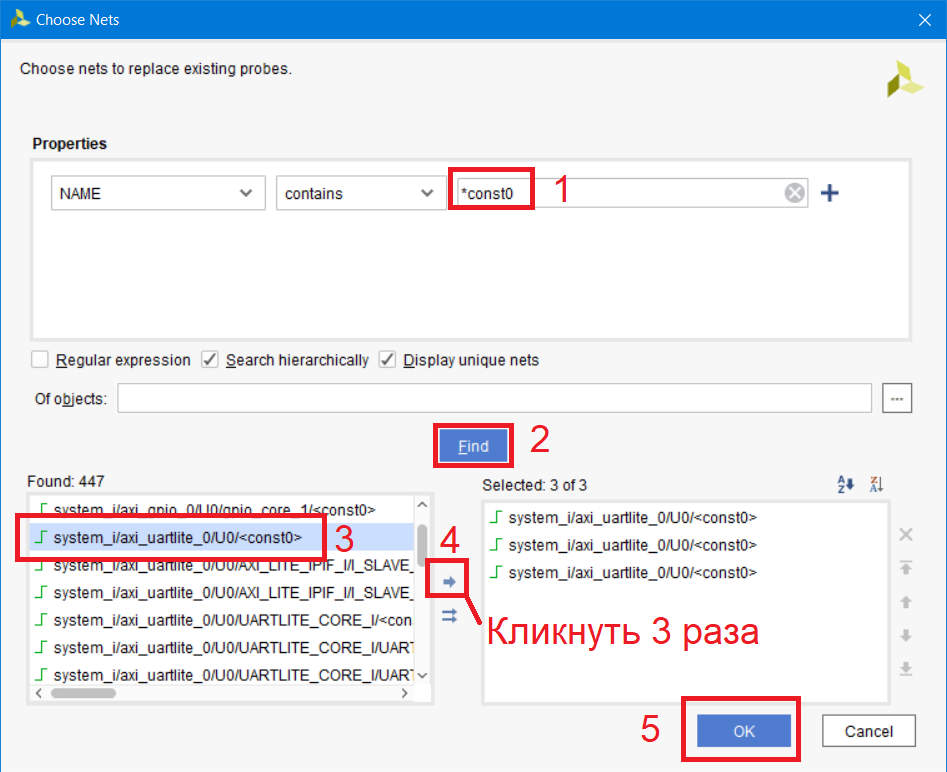

116 –«0», Vivado , gnd const0. , Edit Probes (.117).

117 – ila_1

117 – ila_1*const0 , , (. 118). !!! Debug Hub (dbg_hub), Vivado , . IP, , uartlite.

118 –

118 –ila_1 . 119. , . , DRC.

119 – ila_1

119 – ila_1OK , , DONT_TOUCH , ila_1. , . , , . , Unset Property DCP.

, , (.120). 1 . , !

120 –

Hardware Manger , .bit .ltx .

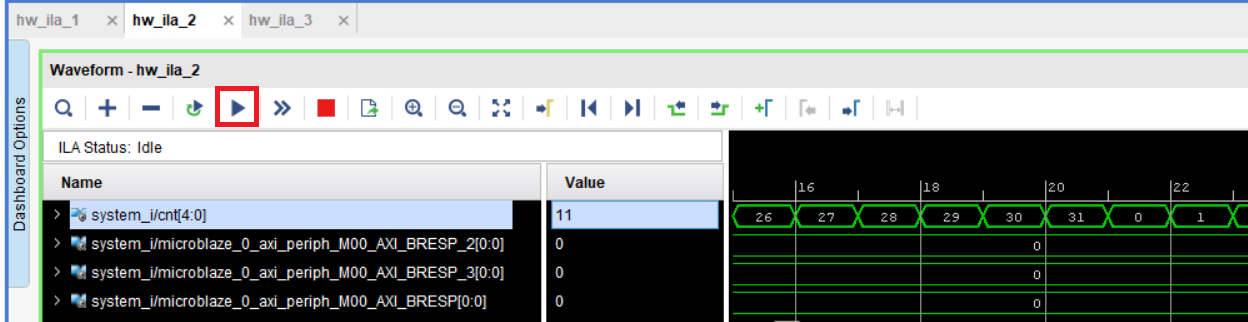

hw_ila_2 4 : cnt const0. cnt hex unsigned decimal ( . 75) , . , cnt 0 31 1 (.121).

121 – cnt ila_1

121 – cnt ila_1, .

6.4. /

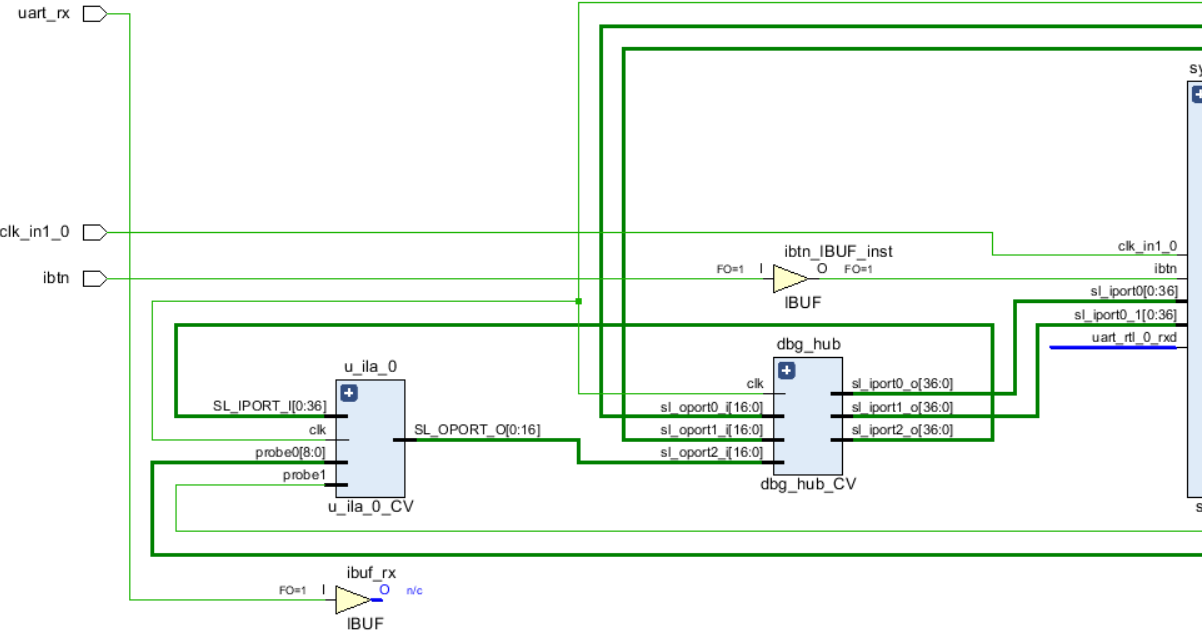

, rx tx uart - Hello World . , ECO , . .

. , , cell, . , .

.

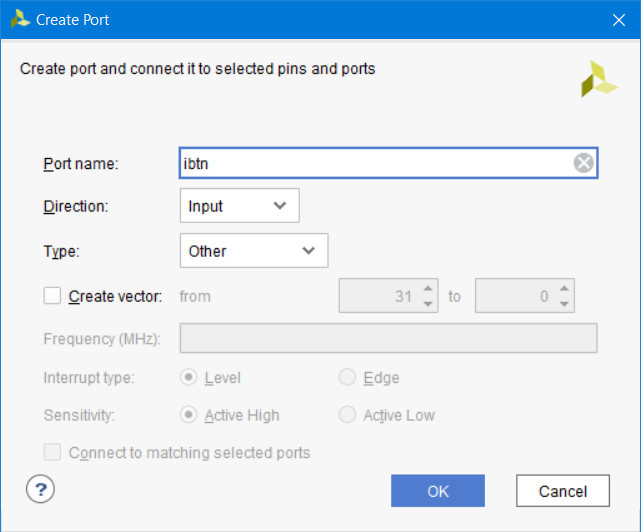

uart_rtl_0_rxd, . unplace cell (. 122). , , .

122 –

122 –. uart_rx, Create Port . 123

123 –

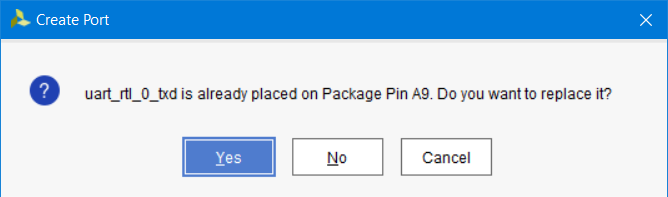

123 –A9 , Vivado , A9. (. 124)

124 –

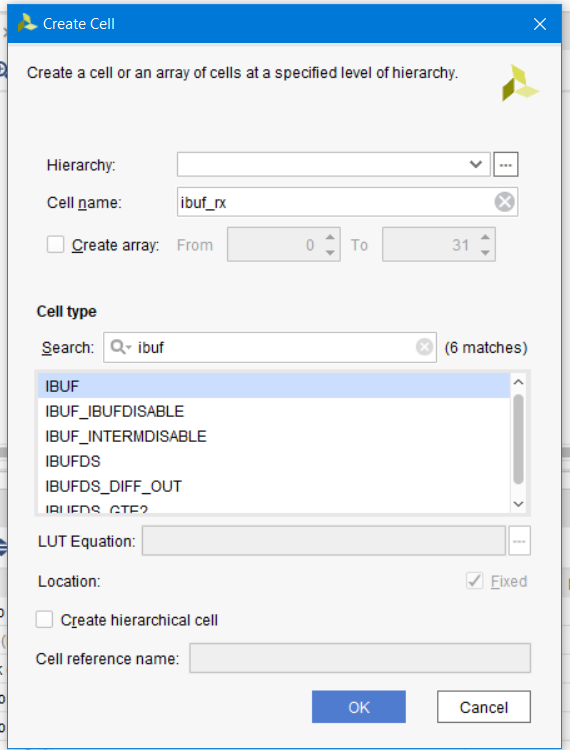

124 –. Create Cell, ibuf_rx (. 125)

125 –

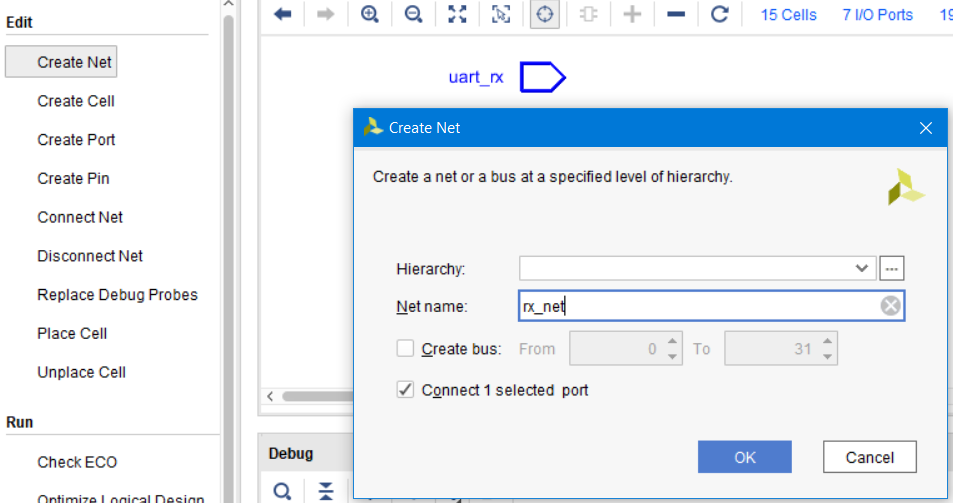

. . , . uart_rx Create Net. rx_net.

126 –

126 –I Connect Net. (. 127)

127 –

127 –, system_i. O uart_rtl_0_rxd, system_i Create Net

128 –

128 –.

uart_rtl_0_txd, . Unplace cell, , (. 122). , , .

129 –

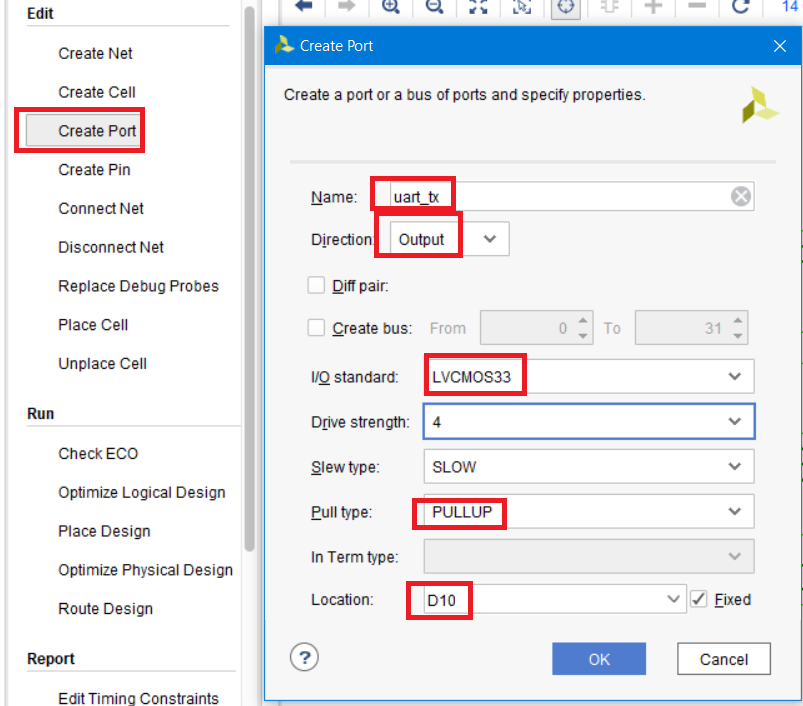

129 –uart_tx, Create Port, Output LVCMOS33 (. 130)

130 –

tx_net, uart_tx. uart_tx Create Net

131 – tx_net

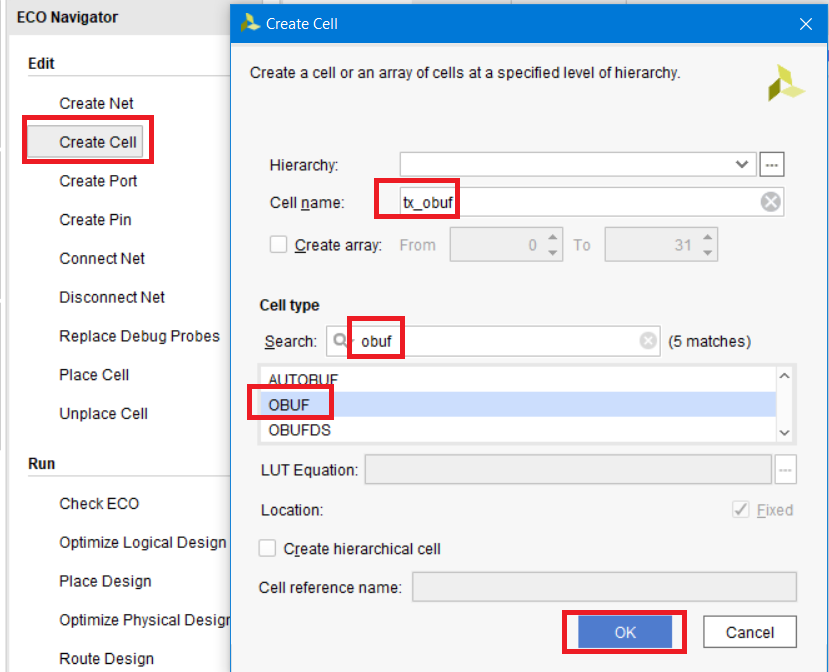

131 – tx_nettx_obuf, Create Cell OBUF (. 132)

132 –

132 –O , uart_tx Connect Net.

133 –

133 –system_i. I uart_rtl_0_txd (. 134).

134 –

134 –. (. 135).

135 –

135 –Hardware Manager . SDK (. . 70). , Hello World: cycle (. 136).

136 – Hello World SDK Terminal

136 – Hello World SDK Terminal7.

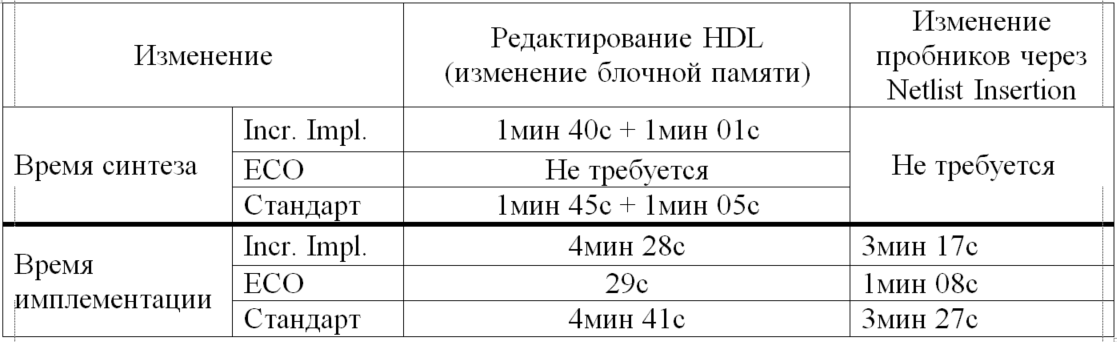

, . , , , .. , , .. HDL , , «-» . 1. , , . , . , IP Integrator – IP RTL.

表1.さまざまなモードで最終ファームウェアファイルを取得するのにかかる時間の比較分析。

比較分析を要約すると、もう一度私はそれが非常に表面的であると言います。FPGAは複雑なシステムであり、デザインルートのこの段階またはその段階は非常に変化する可能性があることを完全に理解しています。それにも関わらず、ECOは合成を必要とせず、特にクリスタルトレースを保存してコンポーネントの内容のみを変更したい場合、プロジェクトへの小さな変更は非常に高速です。8.結論

実際にECOモードを適用したことがありますか? はい , , , . ECO; , Tcl-, . , ECO – , LogicAnalyser (ChipScope) ILA ( ) . , , - , .

ECO Flow , , : Vivado ECO Flow.

. 頑張って

9.

- , LUT, , .

- ECO. Tcl Vivado [9].

- AXI-lIte, GPIO. ECO , ila_1 uartlite, gpio.

- * , MMCM, 100. 50 . , . , , .

- * Tcl , ECO. , , , ..

- ** , brom_reader, 32 ASCII, /

1. Vivado Xilinx

2. Arty Board Digilent

3. UG904 Vivado Design Suite User Guide: Implementation

4. UG908 Vivado Design Suite User Guide Programming and Debugging

5. UG986 Vivado Design Suite Tutorial: Implementation

6. Wiki : ECO

7. UG949 UltraFast Design Methodology Guide

8. UG892 Vivado Design Suite User Guide Design Flows Overview

9. UG835 Vivado Design Suite Tcl Command Reference Guide

10. UG894 Using Tcl Scripting

11. UG901 Vivado Design Suiteユーザーガイド合成

12. Artyリファレンスマニュアル

13. UG908プログラミングおよびデバッグ

14. UG1037 Vivado Design Suite AXIリファレンスガイド

15. Hex-to-ASCII

16. マニュアル: MicroBlazeソフトウェアプロセッサに基づいたプロセッサシステムの開発ザイリンクスVivado IDE / HLx

付録A. flash_ledモジュールのリスト非表示のテキスト library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity flash_led is Port ( iclk : in STD_LOGIC; oled : out STD_LOGIC); end flash_led; architecture rtl of flash_led is signal cnt : natural range 0 to 100_000_001 := 0; signal led : std_logic := '0'; begin process(iclk) begin if rising_edge(iclk) then if cnt = 100_000_000 then cnt <= 0; else cnt <= cnt + 1; end if; if cnt < 50_000_000 then led <= '0'; else led <= '1'; end if; end if; end process; oled <= led; end rtl;

付録B. brom_readerモジュールのリスト非表示のテキスト library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.NUMERIC_STD.ALL; entity brom_reader is Port ( iclk : in STD_LOGIC; odout : out std_logic_vector(7 downto 0) ); end brom_reader; architecture rtl of brom_reader is alias slv is std_logic_vector; type rom_type is array (0 to 31) of natural; signal rom : rom_type := ( 32 , 32, 32, 32, 97, 117, 116, 104, 111, 114, 58, 32, 75, 101, 105, 115, 78 , 49, 51, 32, 32, 32, 32, 32, 32 , 32, 32, 32, 32, 32, 32, 32 ); signal cnt : natural range 0 to rom'length-1 := 0; signal dout: slv(odout'range) := (others => '0'); attribute RAM_STYLE : string; attribute RAM_STYLE of rom : signal is "BLOCK"; begin process(iclk) begin if rising_edge(iclk) then dout <= slv(to_unsigned(rom(cnt), dout'length)); if cnt = (rom'length - 1) then cnt <= 0; else cnt <= cnt + 1; end if; end if; end process; odout <= dout; end rtl;

付録B. helloworldプログラムのリスト非表示のテキスト #include "platform.h" #include "xil_printf.h" #include "xparameters.h" #include "xgpio.h" XGpio Gpio; #define DELAY 10000000 int main() { init_platform(); int Status; volatile int Delay; int k = 0; Status = XGpio_Initialize(&Gpio, XPAR_GPIO_0_BASEADDR); if (Status != XST_SUCCESS) { xil_printf("Gpio Initialization Failed\r\n"); return XST_FAILURE; } while (1) { XGpio_DiscreteWrite(&Gpio, 1, 1); xil_printf("Hello World: cycle %d\n\r", k); k++; for (Delay = 0; Delay < DELAY; Delay++){}; XGpio_DiscreteWrite(&Gpio, 1, 0); for (Delay = 0; Delay < DELAY; Delay++){}; } cleanup_platform(); return 0; }

PS: intekus Des333 , ishevchuk , roman-yanalov 91 ( Word), .