パートIパートIIパートIIIパートIVパートvRAMマシン

パートIパートIIパートIIIパートIVパートvRAMマシンに関する

記事はすでにHabréで公開されています。

一般的に、

RAMマシン に関する記事はウィキペディアにあります。

本「Computation and Analysis of Computational Algorithms」の著者:Aho、Hopcroft、Ulmanに記載されている

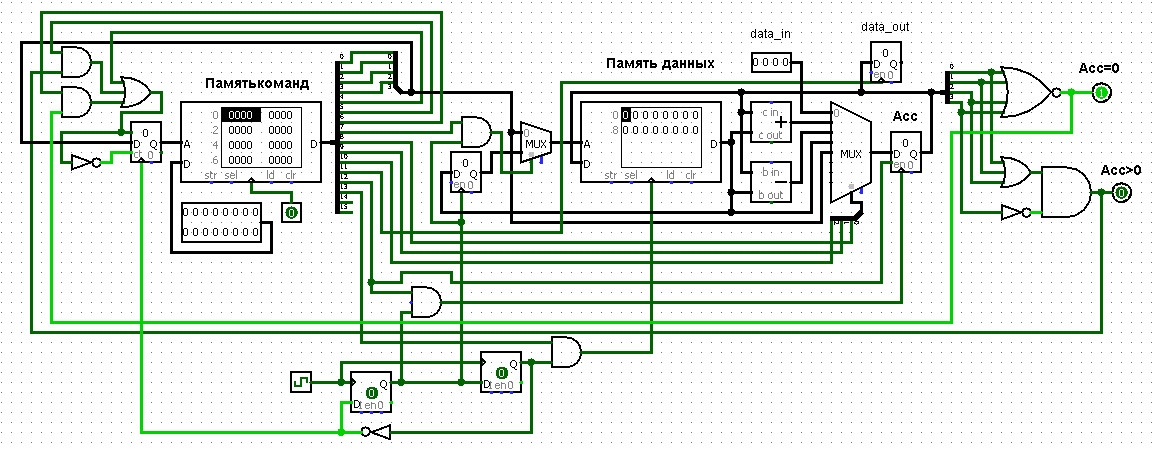

RAMマシンには、限られた数の算術命令セット(加算、減算、乗算、除算)、無条件ジャンプコマンド、2つの条件付きジャンプコマンドがあります。 私たちの場合、算術チームからは、

加算と

減算のみがあり、分岐(遷移)コマンドは本で与えられたコマンドと同一です。

LIttle Man Computer (サイクルの前の部分で説明した)と

RAMマシンの違いは、間接アドレッシング(メモリに格納された数値をアドレスとして使用する機能)を提供するメカニズムです。

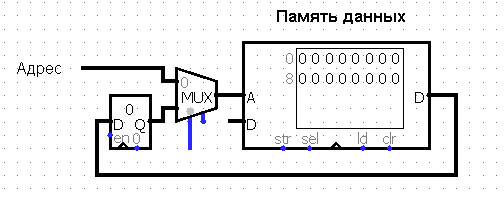

メモリに保存されている番号をアドレスとして使用するために、

MUXマルチプレクサを

データメモリのアドレス入力

に接続し、アドレス自体(

コマンドメモリから来る)とアドレスを表し

データメモリに保存されている番号を選択します。

新しいコマンドが

Command Memoryからフェッチされるたびに、メモリからレジスタに数値をロードします。

MUXマルチプレクサを切り替えると、アドレスレジスタに記録されたアドレスに移動します。

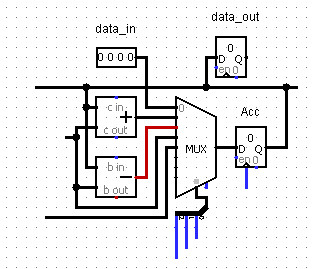

また、コマンドアドレスを数値として

Accバッテリーにロードします。このため、バッテリー

Assにロードするデータを選択するマルチプレクサーのアドレス入力のビット深度を増やします。 アドレスは、マルチプレクサの4番目の入力にロードされます。

コマンドの処理は2つの方法で実行されます。 これを行うには、2つのDフリップフロップをクロックに接続します。これにより、クロック信号が到着したときに相互に切り替わります。

1サイクル目はアドレスをアドレスレジスタにロードし、2サイクル目は数値を

Accアキュムレータまたは

データメモリにロードし

ます 。

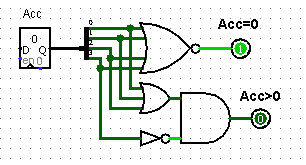

2つのフラグをバッテリーに接続します。

1.フラグ

Acc = 0 。

Assの内容がゼロの場合、フラグが立てられます。

2.フラグ

Acc> 0 。

Assの内容がゼロより大きい場合、フラグが立てられます。

結果はそのようなスキームであり

、ここからダウンロードできます。

回路がバギーにならないように、バッテリイネーブル入力へのラインが必要です。

いくつかのコマンドをオフにし、ゼロセルに格納されているアドレスで

データメモリのゼロセルをロードするプログラムを作成します。 サイクルでは、ゼロセルの値を1つ増やします。 T.O.

データメモリにシリアル番号を入力します。

Accの 1401のロード

、番号

11100は、

Accの数値を

ゼロセルの数値に加算します

2000は結果をゼロセルに保存します

2080は、

ゼロセルによって参照されるアドレスの

Accから数値をロードします

0010プログラムの先頭にジャンプ

要約するプログラムを作成します

自然数。

1番目のセルに自然数を、0番目のセルにそれらの合計を書き込みます。

最初に、最初のセルに自然数をロードするプログラムを作成します

Accの 1401のロード

、番号

11101は、

Accの数値を最初のセルの数値に追加します

2001結果を最初のセルに保存します

0番目のセルでは、合計を実行します。 1番目のセルの数値を増やした後、この数値を0番目のセルに追加する必要があります。

セル0からの

Accの 1300ロード

1101は、

Accの数値を最初のセルの数値に追加します

2000は0番目のセルに結果を保存します

0010プログラムの先頭にジャンプ

プログラムの全文

140111012001130011012000年0010計算するために

等差数列の項では、最初の項を0番目のセルにロードする必要があります

、最初のセルに算術進行の差をロードします

。

次に、要約する必要があります。

セル0から

の番号に

Accで 1300ロード

1101は、

Accの数値を最初のセルの数値に追加します

2000は0番目のセルに結果を保存します

次に、3つのチームに戻って、この一連の操作を繰り返す必要があります

回。

クラシックRAMマシンのエミュレーター(個別の読み取り/書き込みテープ付き)は

、ここからダウンロードでき

ます 。

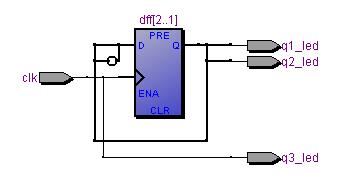

2つのdトリガーで構成される回路の動作を確認しましょう。 この回路は2クロックモードを提供します。

通常のdトリガーの図を作成してみましょう(リセットおよび有効化なし)。 データポートとクロックポートの2つの入力ポートがあります。

module dff ( input [1:0] key, output led ); wire clk; assign clk = key [0]; // wire d = key [1]; // reg q; always @(posedge clk) q <= d; assign led = q; endmodule

LEDは、dトリガーのステータスを示します。

2つの

dffを一般的な回路に接続します。

最初のdトリガーのステータスは、

q1_led LEDによって示されます。

2番目のdトリガーのステータスは、

q2_led LEDによって示されます。

クロック信号を別の

q3_led LEDに出力します。

module dff_dff ( input clk, output q1_led, q2_led,q3_led ); assign q3_led = clk; wire d1_in; assign d1_in=~q2_led; dff dff1( .clk(clk), .d(d1_in), .q(q1_led) ); wire d2; assign d2=q1_led; dff dff2( .clk(clk), .d(d2), .q(q2_led) ); endmodule

dff_dffモジュールのRTLモデルは次のようになります

このスキームはすべてのボードで機能するわけではありません;一部のボードでは、d-フリップフロップを初期化する必要があります。 同じ理由で、そのようなスキームはModelSimでシミュレートされません。