この事実は、以前はマイクロコントローラーを扱っていた初心者の開発者を麻痺状態に陥れます。 一方、FPGAは柔軟に構成可能なロジックセルのセットであり、単純なケースでは、この構成を格納できるメモリがボード上にないため、この動作は正常です。 解決策は、設定を外部メモリに書き込み、電源が投入されたときに自動的にロードすることです。 このプロセスは、ホワイトペーパー

AN 370に記載されています。 また、このプロセスのイラストの私のバージョンを見ることを提案します。

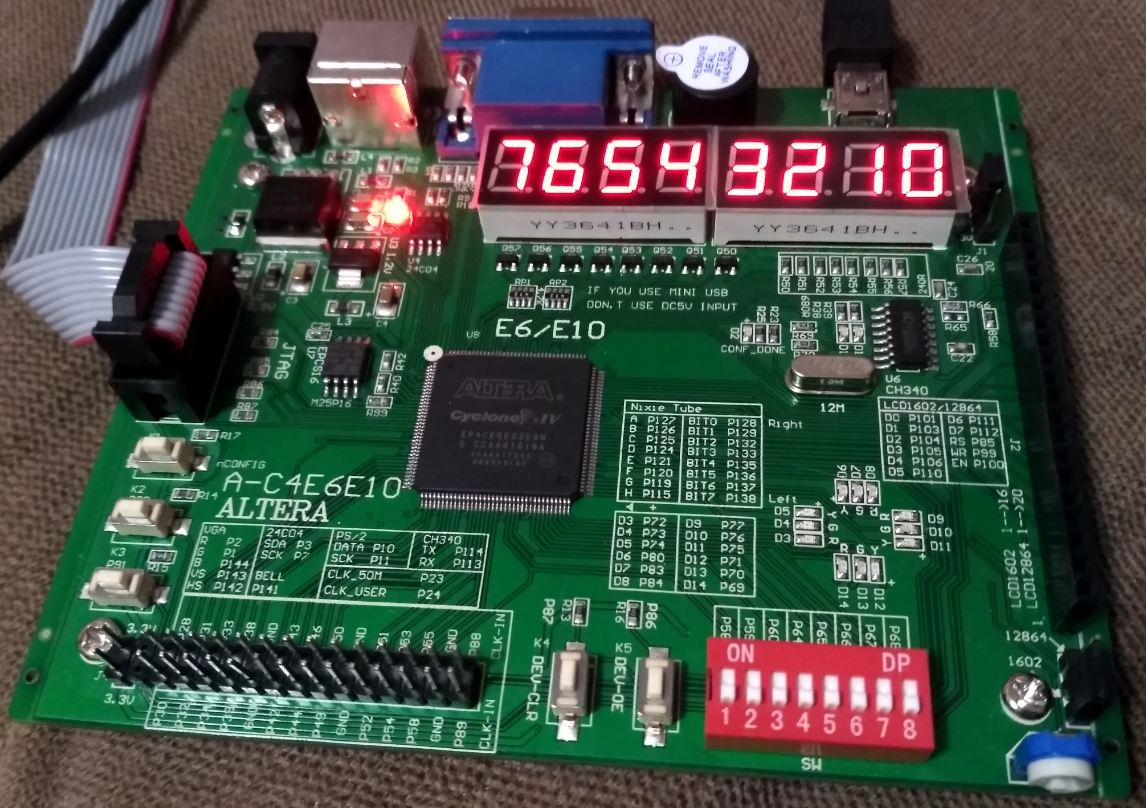

EP4CE6E22C8Nに基づいた

開発ボード用の開発ボードがあります。 初めてオンにすると、美しいプロジェクトがロードされます。

そして、書かれた構成を記入したという事実にもかかわらず、再起動後に何度もそれを見ます。 電力が供給されたときにロードするように記述した構成のために、Quartusでいくつかのアクションを実行する必要があります。

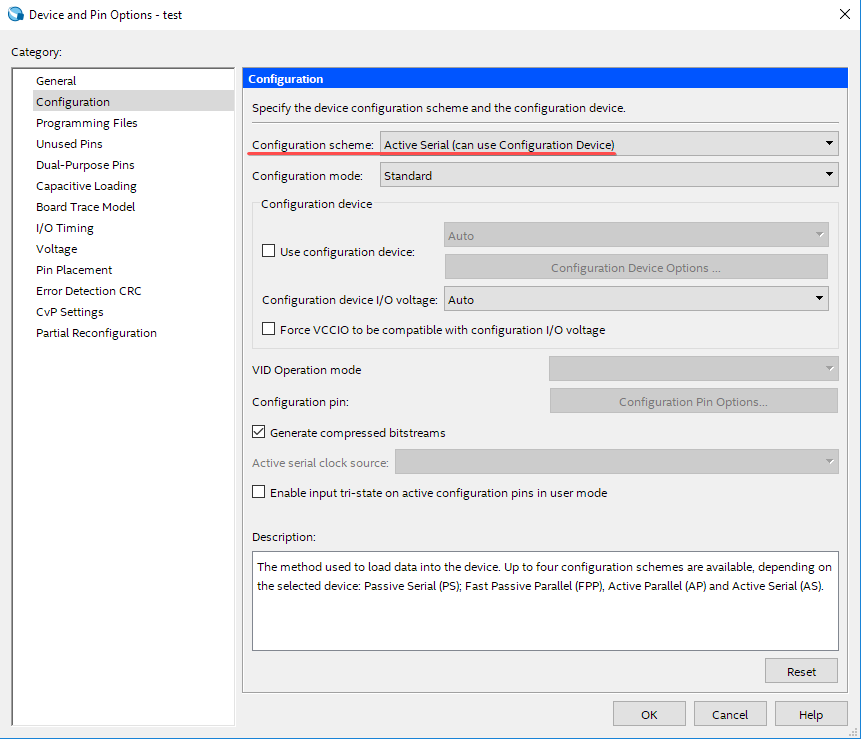

- [構成スキーム]フィールドで[アクティブシリアル]が選択されていることを確認します。 (Assigments-> Device-> Device and pin options-> Configuration)

- プロジェクトをコンパイルする

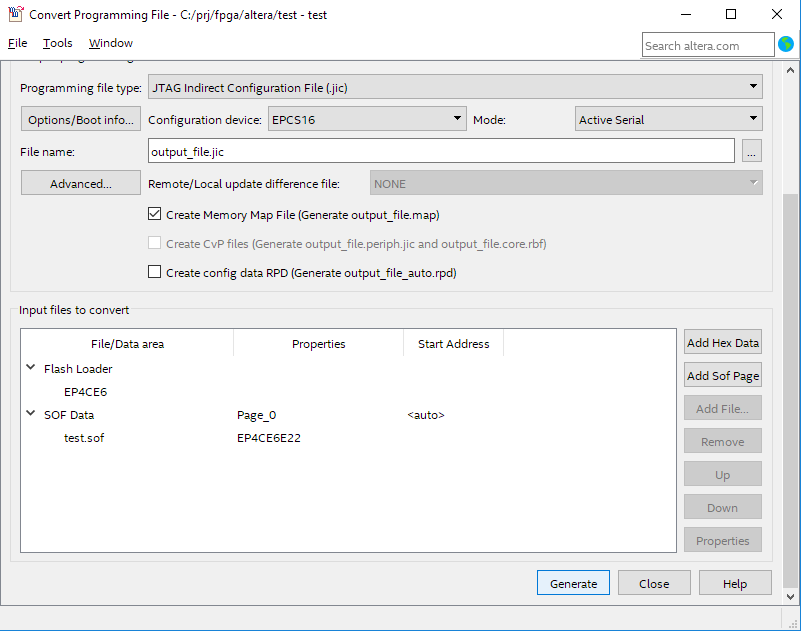

- jicファイルの生成:ファイル->プログラミングファイルの変換->プログラミングファイルタイプの出力->.ji

同じウィンドウで、フラッシュのタイプを選択します。 回路基板を見ると、M25C16があります。 これはまさにQuartusが提供していないものですが、EPCS16オプションが提供します。

以下の同じウィンドウで、変換する入力ファイル->フラッシュローダー->デバイスの追加-> Cyclone IV E-> EP4CE6

SOFデータ->コンパイル段階で取得したファイル(ロード時に表示するファイル)を指定します

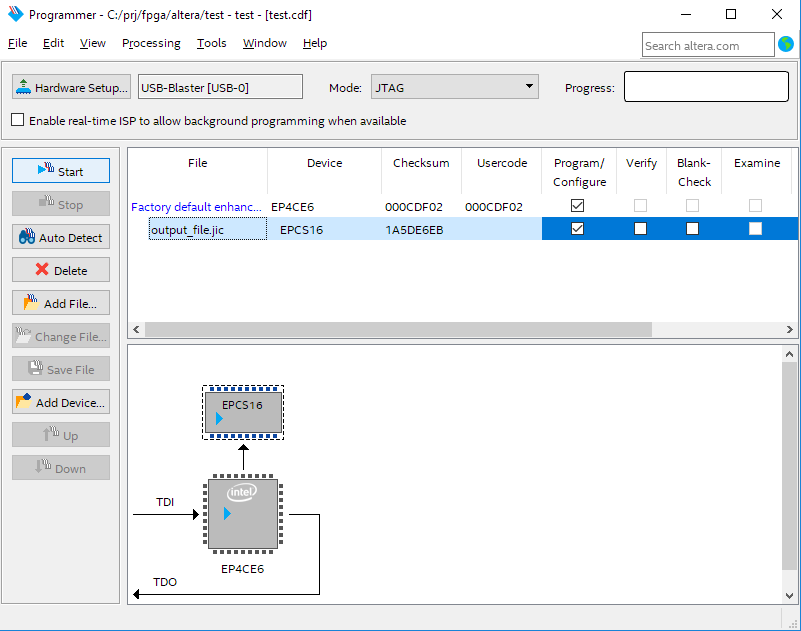

生成をクリックします。 - 受信したjicファイルに入力します

これで、再起動後、作成した構成が表示されます。これにより、電源が投入されるとFPGAが自動的に構成されます。